版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

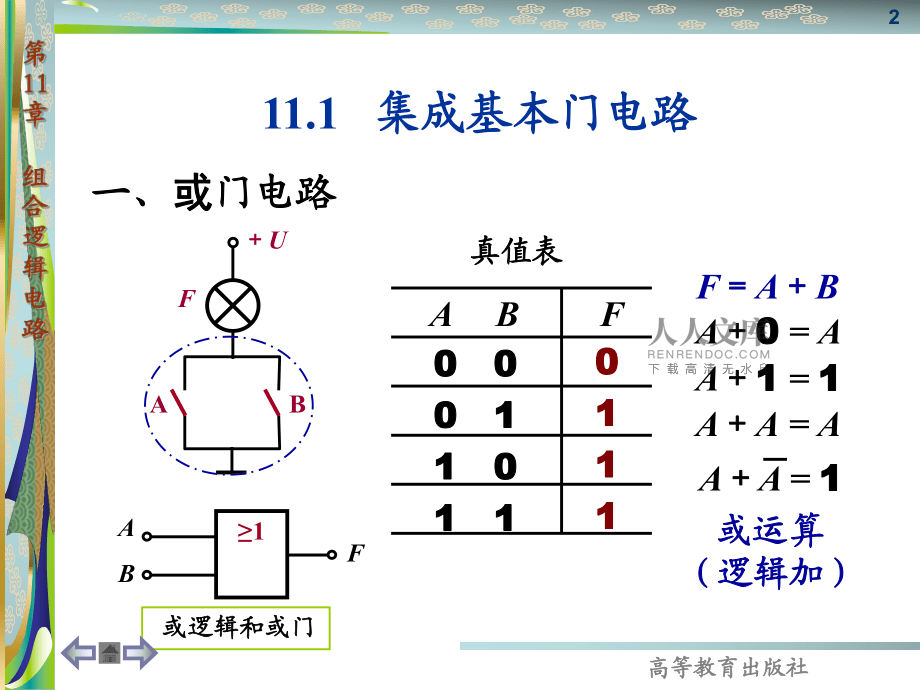

1、电子技术电子技术 下一章下一章 上一章上一章 返回主页返回主页 2一、一、或或门电路门电路 11.1 集成基本门电路集成基本门电路 UABF1 ABF0 01 11 11 10 0 0 00 0 1 11 01 01 1 1 1A B F 真值表真值表FAB A0 0 = AA1 1 = 1 1 AA = AAA = 1 1 或运算或运算(逻辑加)(逻辑加) 或逻辑和或门或逻辑和或门 高等教育出版社高等教育出版社3信号输入端信号输入端信号控制端信号控制端当当 B = 0 0 时,时,F = A 门打开门打开当当 B = 1 1 时,时,F = 1 1 门关闭门关闭 或或门还可以起控制门的作用门

2、还可以起控制门的作用 1 ABF高等教育出版社高等教育出版社4信号输入端信号输入端信号控制端信号控制端当当 B = 0 0 时,时,F = A 门打开门打开当当 B = 1 1 时,时,F = 1 1 门关闭门关闭 或或门还可以起控制门的作用门还可以起控制门的作用 1 ABF高等教育出版社高等教育出版社5 例例11.1.1 下图所示为一保险柜的防盗报警电路。下图所示为一保险柜的防盗报警电路。 保险柜的两层门上各装有一个开关保险柜的两层门上各装有一个开关S1和和S2。门关上时,。门关上时, 开关闭合。当任一层门打开时,报警灯亮,试说明该开关闭合。当任一层门打开时,报警灯亮,试说明该 电路的工作原

3、理。电路的工作原理。+5V1 S1S21k1k30 EL分析:开关分析:开关 S1 和和 S2 任一个打开时,报警灯亮。任一个打开时,报警灯亮。 高等教育出版社高等教育出版社6二、二、 与与门电路门电路FABA 0 0 = 0 0 A 1 1 = A A A = A 0 00 00 01 10 0 0 00 10 11 01 01 11 1ABUFA B F 真值表真值表A A = 0 0 &ABF与运算与运算(逻辑乘)(逻辑乘) 与逻辑和与门与逻辑和与门 高等教育出版社高等教育出版社7当当 B = 1 1 时,时,F = A 门打开门打开当当 B = 0 0 时,时,F = 0 0

4、门关闭门关闭信号输入端信号输入端 与与门也可以起控制门的作用门也可以起控制门的作用 &ABF信号控制端信号控制端高等教育出版社高等教育出版社8三、三、 非非门电路门电路AUFR1AF0 01 11 10 0F = A 非运算非运算 (逻辑非)(逻辑非) A F 真值表真值表0 0 = 1 1 1 1 = 0 0 A = A 非逻辑和非门非逻辑和非门 高等教育出版社高等教育出版社911.2 集成复合门电路集成复合门电路TTL 电路电路CMOS 电路电路CT1000 通用系列通用系列CC0000 CC4000CT2000 高速系列高速系列 CT4000 低功耗系列低功耗系列CT3000高等

5、教育出版社高等教育出版社10一、 或非或非门电路F1 AB1 10 00 00 00 0 0 00 10 11 01 01 11 1A B F 真值表真值表F = AB 或非门或非门 高等教育出版社高等教育出版社11 CMOS 或或非门原理电路非门原理电路 A = 0 0,B = 0 0,F = 1 1 PMOS1 和和 PMOS2 导通导通 NMOS1 和和 NMOS2 截止截止 A = 0 0,B = 1 1,F = 0 0 PMOS1 和和 NMOS2 导通导通 NMOS1 和和 PMOS2 截止截止 A = 1 1,B = 0 0,F = 0 0 NMOS1 和和 PMOS2 导通导通

6、 PMOS1 和和 NMOS2 截止截止 A = 1 1,B = 1 1,F = 0 0 PMOS1 和和 PMOS2 导通导通 NMOS1 和和 NMOS2 截止截止 CMOS 或非门或非门 NMOS2PMOS1PMOS2FANMOS1DDDDSSSS+UB高等教育出版社高等教育出版社12二、 与非与非门电路F&AB1 11 11 10 00 0 0 00 10 11 01 01 11 1A B F 真值表真值表F = A B 与非门与非门 高等教育出版社高等教育出版社13 TTL 与非门原理电路与非门原理电路 A = 0 0,B = 0 0, A = 0 0,B = 1 1, A

7、= 1 1,B = 0 0, F = 1 1 T1 处于饱和状态处于饱和状态 T3 导通导通T2 和和 T4 处于截止状态处于截止状态 A = 1 1,B = 1 1, T1 和和 T3 处于截止状态处于截止状态 T2 和和 T4 处于饱和导通处于饱和导通 F = 0 0 TTL 与非门与非门 1B1CD+ 5 VT4RB1RC2RC3ABF T1 T2 T3 RE23.6V 0V高等教育出版社高等教育出版社14三、 三态与非与非门逻辑符号逻辑符号逻辑功能逻辑功能:F&ABE ENE = 0 0 F = ZE = 1 1 F = A BE = 1 1 F = ZE = 0 0 F =

8、A BF&ABE EN高等教育出版社高等教育出版社15例例11.2.1 试利用与非门来组成非门、与门和或门。试利用与非门来组成非门、与门和或门。 (b) 与门与门 (c) 或门或门 (a) 非门非门 F = A A = AF = A B =A BF = A B =A + B解:解:&AF&FAB&FAB高等教育出版社高等教育出版社1611.3 组合逻辑电路的分析组合逻辑电路的分析一、组合逻辑电路一、组合逻辑电路(1)由输入变量由输入变量 (即即 A 和和 B ) 开始,逐级推导出开始,逐级推导出各个门电路的输出,最好将结果标明在图上。各个门电路的输出,最好将结果

9、标明在图上。二、二、 分析步骤分析步骤(2) 利用逻辑代数对输出结果进行变换或化简。利用逻辑代数对输出结果进行变换或化简。三、逻辑代数简介三、逻辑代数简介 由门电路组成的逻辑电路叫由门电路组成的逻辑电路叫组合逻辑电路组合逻辑电路。 逻辑变量只取逻辑变量只取 0 0、1 1 两个值。两个值。高等教育出版社高等教育出版社17公式名称公式名称 公式内容公式内容自等律自等律A+ 0 0 = AA 1 1 = A0-1律律A+ 1 1=1 1A 0 0= 0 0重叠律重叠律A+ A = AA A = A互补律互补律A+ A = 1A A = 0 复原律复原律A = A表表11.3.1 逻辑代数的基本公式

10、(逻辑代数的基本公式(1) 高等教育出版社高等教育出版社18 公式名称公式名称 公式内容公式内容 交换律交换律 结合律结合律 分配律分配律 吸收律吸收律 反演律反演律 (摩根定律摩根定律)A+B = B+AA B = B AA+(B+C) = B+(C+A) = C+(A+B) A (B C) = B (C A)=C (A B)A+(B C) = (A+B) (A+C)A (B + C) = (A B) + (A C)A+(A B) = AA (A + B) = A A B = A + B A + B = A B 表表11.3.1 逻辑代数的基本公式(逻辑代数的基本公式(2) 高等教育出版社高

11、等教育出版社19B AB0 0 0 00 10 11 01 01 11 1A ABAB异或门异或门 F = A AB B AB= A BA B = A ( AB )B ( AB ) = A ABB AB = 例例11.3.0 分析图示逻辑电路的功能。分析图示逻辑电路的功能。 0 01 11 10 0A B F 真值表真值表A B F &A AB B AB 解:解:高等教育出版社高等教育出版社20F = A B + A B= A B + A B = A B 异或门异或门 =1A BF1 =1AB F 1F=1AB F 同或门同或门 =高等教育出版社高等教育出版社21 名称名称国标逻辑符号

12、国标逻辑符号IEC逻辑符号逻辑符号逻辑表达式逻辑表达式或门或门与门与门非门非门或非门或非门与非门与非门表表11.3.3 常用门电路的逻辑符号和逻辑表达式常用门电路的逻辑符号和逻辑表达式1 ABF&ABFF&ABF1 AB1AFF = ABF = AB F = A F = A B F = AB 高等教育出版社高等教育出版社22例例11.3.1 分析图示密码锁电路的密码。分析图示密码锁电路的密码。 S +5VA B C D E F1F211 1 ABCDE F1 = 1 1 A B C D E = 1 1 开锁信号。开锁信号。 1 1 0 01 10 01 1 = 1 1 报警信号

13、。报警信号。1 11 11 11 11 1密码为:密码为:1 0 1 0 11 0 1 0 1。 ABCDE F2 = 1 1 A B C D E 解:解: 高等教育出版社高等教育出版社2311.4 组合逻辑电路的设计组合逻辑电路的设计(1) 根据逻辑功能列出真值表根据逻辑功能列出真值表0 00 01 1 0 01 1 0 00 0 1 1A BF C0 0 0 0 0 1 0 1 1 01 01 1 1 1 两个一位两个一位二进制数二进制数 本位和本位和 进位位进位位 高等教育出版社高等教育出版社24(3) 根据逻辑表达式画出逻辑电路根据逻辑表达式画出逻辑电路&C ABF =1ABF

14、 C CO 半加器半加器 (2) 根据真值表写出逻辑表达式根据真值表写出逻辑表达式 本位和本位和 进位位进位位 C = A BF = A B +A B = A B 高等教育出版社高等教育出版社25(1) 根据逻辑功能列出真值表根据逻辑功能列出真值表Ai Bi Ci-1 Fi Ci0 00 00 10 11 01 01 11 10 0 1 10 01 10 01 10 01 1两个两个 n 位二进位二进制数中的一位制数中的一位本位和本位和 进位位进位位 0 0 0 0 1 1 0 0 1 1 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 1 1 1 1 1 1 Fi = Ai

15、BiCi1 AiBiCi1 AiBiCi1 AiBiCi1 Ci = AiBiCi1 AiBiCi1 AiBiCi1 AiBiCi1 (2) 根据真值表写出逻辑表达式根据真值表写出逻辑表达式 高等教育出版社高等教育出版社26(3) 化简或变换逻辑式化简或变换逻辑式 = (AiBiAiBi ) Ci1 = (Ai Bi ) Ci1 = (Ai Bi) Ci1= ( Ai Bi ) Ci1 + AiBi = Ai Bi Ci1 ( AiBiAiBi ) Ci1 ( Ai Bi ) Ci1 = ( Ai Bi AiBi ) Ci1 AiBi ( Ci1Ci1 ) Fi = Ai BiCi1 AiBi

16、Ci1 AiBiCi1 AiBiCi1 Ci = AiBiCi1 AiBiCi1 AiBiCi1 AiBiCi1 高等教育出版社高等教育出版社27(4) 根据逻辑表达式画出逻辑电路根据逻辑表达式画出逻辑电路AiBiAi Bi Fi Ci COAi Bi 1(Ai Bi ) Ci(Ai Bi ) Ci1 COCi1 Fi = Ai Bi Ci1Ci = (Ai Bi)Ci1 + AiBi Ai Bi Ci1 Fi Ci CI CO全加器全加器 全加器全加器 高等教育出版社高等教育出版社28 4 位全加器逻辑图:位全加器逻辑图: CI COCI COCI COCI COF4F3F2F1C4C3C2

17、C1C0A4 B4A3 B3A2 B2A1 B1 4 位全加器逻辑图位全加器逻辑图 高等教育出版社高等教育出版社2911.5 编码器编码器控制信息控制信息编码器编码器二进制代码二进制代码编码器的分类编码器的分类 可实现编码功能的组合逻辑电路。可实现编码功能的组合逻辑电路。 普通编码器普通编码器 优先编码器优先编码器 二进制编码器二进制编码器 二二- -十进制编码器十进制编码器 高等教育出版社高等教育出版社30一、普通编码器一、普通编码器 每次只允许输入一个控制信息的编码器。每次只允许输入一个控制信息的编码器。 1. 二进制编码器二进制编码器 将输入信号编成二进制代码的电路。将输入信号编成二进制

18、代码的电路。编码器编码器高等教育出版社高等教育出版社31当当 n = 2 时,即为时,即为 4 线线2 线编码器:线编码器: 四个需要四个需要编码的信号编码的信号 两位二进制代码两位二进制代码F1F2A0A1A2A3二进二进制编制编码器码器0 00 00 10 11 1 0 01 1 1 1输入输入F1 F2A0A3A1A2 4 线线-2 线编码器线编码器 高等教育出版社高等教育出版社32 2. 二十进制编码器(二十进制编码器(BCD 码)码) 十进制数十进制数 0 9:0000 10010000 1001 (8421 BCD 码码)例如十进制数例如十进制数 357 用二进制数表示为:用二进制

19、数表示为: 0011 0101 01110011 0101 0111键控二十进制编码器键控二十进制编码器:输入端:十个按键输入端:十个按键 A0 A9输出端:输出端:F1 F4357高等教育出版社高等教育出版社33表表11.5.1 编码器真值表编码器真值表 A0 A1 A2 A3 A4 A5 A6 A7 A8 A9F4 F3 F2 F1 0 1 1 1 1 1 1 1 1 1 0 0 0 0 1 0 1 1 1 1 1 1 1 10 0 0 1 1 1 0 1 1 1 1 1 1 10 0 1 01 1 1 0 1 1 1 1 1 1 0 0 1 11 1 1 1 0 1 1 1 1 10 1

20、 0 01 1 1 1 1 0 1 1 1 1 0 1 0 11 1 1 1 1 1 0 1 1 10 1 1 0 1 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 1 0 1 1 0 0 01 1 1 1 1 1 1 1 1 0 1 0 0 1编码器表达式编码器表达式F1 = A1 A3 A5 A7 A9F2 = A2 A3 A6 A7 F3 = A4 A5 A 6 A7 F4 = A8 A9高等教育出版社高等教育出版社34 编码器电路编码器电路 A0& 1&G4&G1&G3&G21k10F4F3F1F2+5VSELA

21、4A5A6A7A8A9A3A2A1 G5G6高等教育出版社高等教育出版社35当有键按下时,当有键按下时, S = 1 1 灯亮灯亮当所有键未按下时,当所有键未按下时,S = 0 0 灯不亮灯不亮区分:区分:当所有键都未按下时,输出当所有键都未按下时,输出 00000000当当 A0 键按下时,输出键按下时,输出 00000000S = A0 F1+F2+F3+F4 = A0 + F1+F2+F3+F4高等教育出版社高等教育出版社36表表11.5.2 优先权编码器真值表优先权编码器真值表 如果同时有多如果同时有多 个信号输入,个信号输入, 输出的是数码输出的是数码 大的输入信号大的输入信号 对应

22、的代码。对应的代码。 二、二、优先编码器优先编码器 A1 A2 A3 A4 A5 A6 A7 A8 A9F4 F3 F2 F1 1 1 1 1 1 1 1 1 1 1 1 1 10 1 1 1 1 1 1 1 1 1 1 1 0 0 1 1 1 1 1 1 11 1 0 1 0 1 1 1 1 1 1 1 1 0 0 0 1 1 1 1 11 0 1 1 0 1 1 1 1 1 0 1 0 0 1 1 11 0 0 1 0 1 1 1 0 0 0 0 1 0 1 1 1 0 0 1 1 0高等教育出版社高等教育出版社3711.6 译码器译码器 将具有特定含义的二进制代码变换成一定将具有特定含义

23、的二进制代码变换成一定n 位二进制位二进制代码输入代码输入2n 种状态种状态2n 种输出种输出译码器译码器二进制数代码二进制数代码 按其编码时的原意翻译成按其编码时的原意翻译成 对应的信号输出对应的信号输出一、一、 二进制译码器二进制译码器的输出信号,以表示二进制代码的原意,这一的输出信号,以表示二进制代码的原意,这一实现译码功能的组合电路为译码器。实现译码功能的组合电路为译码器。过程称为译码。过程称为译码。高等教育出版社高等教育出版社38n = 2 时即为时即为 2 线线4 线译码器:线译码器: F1 E A21 A2A1F1 F2F3F4E 111F3 E A21 F2 E A21 F4

24、E A21 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 低电平译码低电平译码 E A1 A2 F1 F2 F3 F41 1 0 0功功 能能 表表1 1 1 11 1 1 10 0 1 1 1 1 1 11 1 0 0 1 1 1 11 1 1 1 0 0 1 11 1 1 1 1 1 0 0=E+A1+A2=E+A1+A2 译码器电路译码器电路 =E+A1+A2=E+A1+A2高等教育出版社高等教育出版社39共共阳阳极极共共阴阴极极a b c d e f gUCCa b c d e f g LED 显示器的两种接法显示器的两种接法 a b d e f gc f g a b

25、e d c h高等教育出版社高等教育出版社40输输 入入 输输 出出 A4 A3 A2 A1 a b c d e f g 显显 示示 0 0 0 00 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 0 1 0 0 0 1 1 0 0 1 1 0 1 0 0 0 1 0 0 0 1 0 1 0 1 0 1 0 1 1 0 0 1 1 0 0 1 1 1 0 1 1 1 1 0 0 0 1 0 0 0 1 0 0 1 1 0 0 1 表表11.6.2 显示译码器功能表显示译码器功能表 1 1 1 1 1 1 0 1 1 1 1 1 1 0 0 1 1 0 0 0 00 1 1 0

26、 0 0 01 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 1 1 0 0 1 1 1 1 1 0 0 1 0 1 1 0 0 1 1 0 1 1 0 0 1 1 1 0 1 1 0 1 1 1 0 1 1 0 1 1 1 0 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 0 0 0 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 11 1 1 1 0 1 101 23456789 高等教育出版社高等教育出版社41 显示译码器的连接图显示译码器的连接图 +UCCabc defgA4 A3 A2A1 BCD码码输输入入显示显示译码器译码器LED显示器显示器 显示译码器显示译码器 高等教育出版社高等教育出版社42* 11.7 可编程逻辑器件可编程逻辑器件PLD与与门阵列门阵列或或门阵列门阵列 或门或门 实现实现或或运算运算 与门与门 实现实现与与运算运算 与门和或门通常改用示意符号表示。与门和或门通常改用示意符号表示。 &ABF1ABCF 1FA B CA B C&F 或门的示意画法或门的示意画法 高等教育出版社高等教育出版社43 与门阵列和或门阵列与门阵列和或门阵列 11111111iAiB1iCiAiB1iCA4 A3 A2 A1F1 F2 F3 F4&高等

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- Unit 1 A new start:Presenting ideas 教学设计 2024-2025学年外研版(2024年)英语七年级 上册

- 5《搭石》教学设计-2024-2025学年统编版语文五年级上册

- 三年级信息技术上册 4 熟悉键位分布教学实录2 闽教版

- 6 班级生活有规则 (教学设计)2024-2025学年统编版道德与法治二年级上册

- 2025违反租赁合同赔偿标准

- 多媒体课件又称为

- 七年级生物上册 1.1.1生物的特征教学实录 (新版)新人教版

- 2025年北京市公司租房合同

- 2025租赁合同条款包括什么

- 2025租赁合同例范文

- 建筑施工结构加固工程施工方案

- 钢结构原理与设计概述课件

- 高校辅导员素质能力大赛基础知识选择题题库(80题)

- 新时代中小学教师职业行为十项准则考核试题及答案

- 初中数学几何模型半角模型探究公开课课件

- 丝袜英文对照表

- 工器具检查及记录表

- 教学运行管理

- Unit 6 Food and Drinks-Grammar 可数名词与不可数名词课件(共12张PPT)-2022-2023学年中职英语新高教版(2021)基础模块1

- 墙面裱糊工程施工方案及工艺方法

- 核电厂安全核电厂安全设计

评论

0/150

提交评论