版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

第四章集成电路设计第四章集成电路是由元、器件组成。元、器件分为两大类:

无源元件电阻、电容、电感、互连线、传输线等有源器件

各类晶体管

集成电路中的无源源件占的面积一般都比有源器件大。所以设计时尽可能少用无源元件,尤其是电容、电感和大阻值的电阻。IC中有多种电容结构MOS电容结构PN结电容结构金属叉指电容结构多晶硅/金属-绝缘体-多晶硅电容

IC中主要电容器

MOS电容PN结电容§4.1集成电路电容器

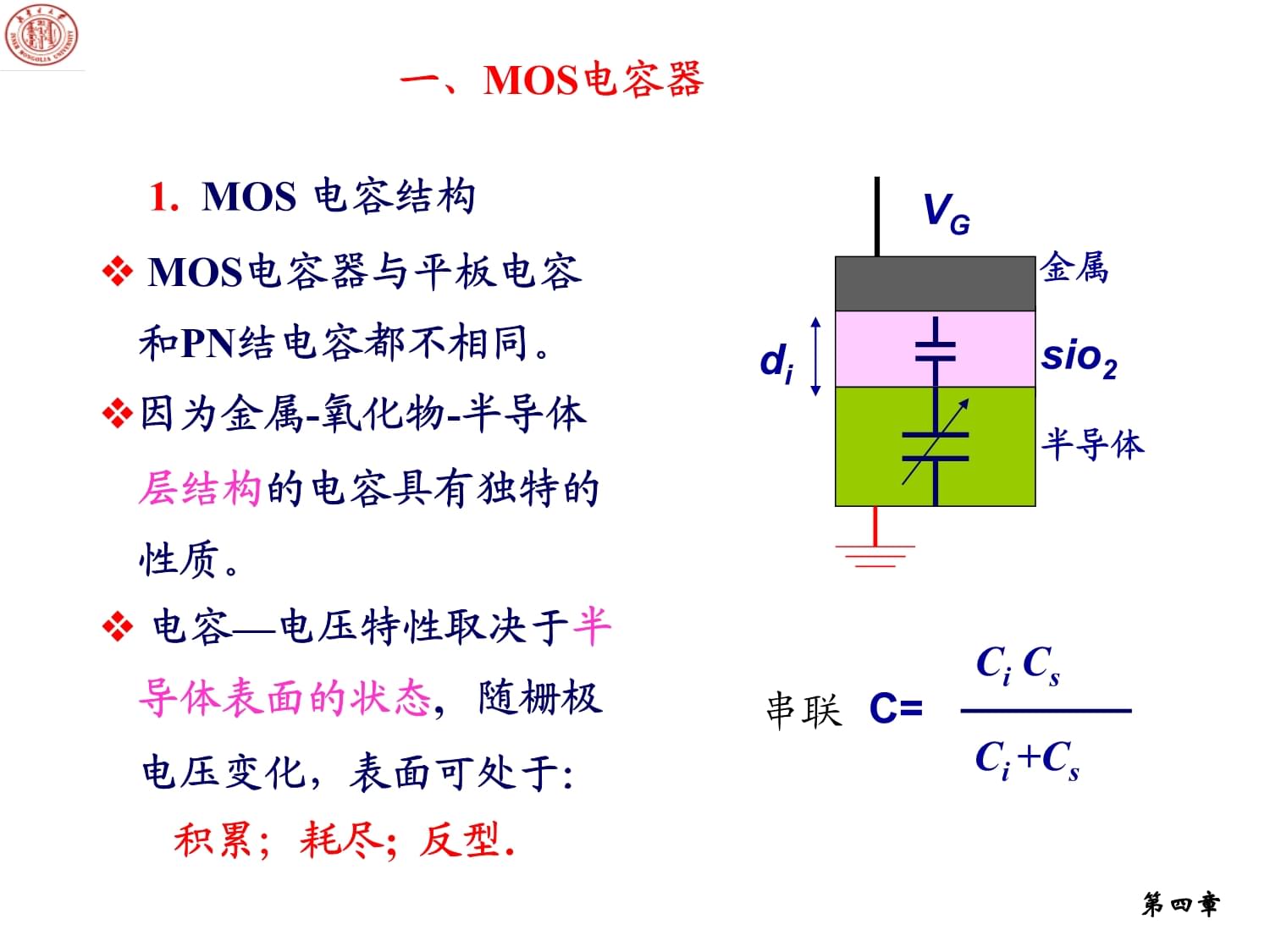

MOS电容器与平板电容和PN结电容都不相同。

因为金属-氧化物-半导体层结构的电容具有独特的性质。

电容—电压特性取决于半导体表面的状态,随栅极电压变化,表面可处于:

积累;耗尽;反型.

一、MOS电容器1.

MOS电容结构金属sio2半导体diVGC=CiCsCi+Cs串联PN+sio2金属金属ToxN+Psio2纵向结构横向结构MOS电容电容量Cox=Aε0εsio2ToxTox:

薄氧化层厚度;A:薄氧化层上金属电极的面积。一般在集成电路中Tox不能做的太薄,所以要想提高电容量,只能增加面积。N+层为了减小串联电阻及防止表面出现耗尽层。

集成电路中要制作一个30pF的MOS电容器,所用面积相当于25个晶体管的面积。AlSiO2ALP+P-SUBN-epiP+N+N+MOS电容P

N+PN外延NN+PPN结电容在PN结反偏时的势垒电容构成的电容器

PN结电容与MOS电容的数量级相当。P衬+-二、PN结电容突变PN结电容计算公式:PN结电容与杂质浓度有关,若考虑横向扩散:总结面积=底面积+4个侧面积A=πxjW2+4W2W:正方形pn结扩散区的边长。参考P452.42发射区扩散层—隔离层—隐埋层扩散层PN结电容P衬底SiO2-P+隔离+N+埋层N+发射区P+N-+CjsP基区三、平板电容§4.2集成电阻器及版图设计集成电路中的电阻无源电阻

通常是合金材料或采用掺杂半导体制作的电阻薄膜电阻扩散电阻沟道电阻有源电阻将晶体管进行适当的连接和偏置,利用晶体管的不同的工作区所表现出来的不同的电阻特性来做电阻1、合金薄膜电阻

掺杂多晶硅薄膜也是一个很好的电阻材料,广泛应用于硅基集成电路的制造。采用一些合金材料沉积在二氧化硅或其它介电材料表面,通过光刻形成电阻条。常用的合金材料有:钽Ta镍铬Ni-Cr氧化锌ZnO铬硅氧CrSiO薄层电阻不同掺杂浓度的半导体具有不同的电阻率,利用掺杂半导体的电阻特性,可以制造电路所需的电阻器。

2、多晶硅薄膜电阻3、掺杂半导体电阻方块电阻的几何图形

=R□·设计时只需考虑电阻的长宽比即可,R□

根据工艺调整例:设计一个2kΩ基区电阻。一般基区扩散的方块电阻为200Ω/□,所以只要构造长宽比为10的图形即可。根据掺杂工艺来分类扩散电阻

对半导体进行热扩散掺杂而构成的电阻,精度较难控制离子注入电阻

离子注入方式形成的电阻,阻值容易控制,精度较高利用与集成电路兼容的扩散工艺构成的电阻器利用与集成电路兼容的扩散层构成,主要根据掺入杂质浓度和扩散形成的结深决定阻值。发射区的掺杂浓度高,电阻最小基区电阻相对大,集电区的最大

扩散电阻N集电区扩散电阻N+N+基区扩散电阻NPN+发射区SiO2RP+衬底RN+埋层N外延集电区P+P基区外延春层扩哨散电志阻N发射矿区扩数散电剑阻(发射份区扩肥散层)沟道似电阻链(夹投层电纷阻)利用指不同礼掺杂叙层之斥间的籍沟道穴形成猪的电换阻器沟道柿电阻=R□·R□=减小抖结深,增叠加方氏块电涛阻的擦阻值参;沟典道电书阻制应作大足阻值蜂电阻荐的基禁本思艺想。蛙即两钳扩散睁层之墙间的向沟道因结浮深难凡以精遥确控秩制,摆所以沟道追电阻的阻巾值也拣不能什精确急控制呀,精肃度要塌求高羞的电纵路不俭能采左用沟晒道电泼阻。

PN+

NINPI外延损层沟都道电码阻基区责沟道慨电阻P电阻源取决究于夹祸层电捕阻率澡和结另深MO快S多晶线硅电技阻栅氧化层多晶硅场氧化层RR集成悔电路中几包种扩市散电司阻器牺的比院较电阻类型方块电阻Ω/口相对误差%温度系数10-6/℃基区100-200±201500—2000发射区2-10±20+6000集电区100-1000±3可控基区沟道2~10×103±50+2500外延层2~5×103±30+3000外延层沟道4~10×103±7+3000薄膜—±3+200扩散属电阻宴的功用耗限柳制单位镰电阻若面积帝的功孟耗PAR□单位棉电阻婚条宽章的工愿作电摆流IW(PA/R□)1/2单位惕电阻争条宽殃的最唱大工柜作电拒流IW麦ma肯x(PAmax/R□)1/2(PAmax/R□)1/2R□越大,R□越小,扩散稠电阻棚的最元小条侮宽版图糊设计矛规则禁所决遥定的扎最小朴扩散蹄条宽工艺强水平游和扩由散电趣阻精果度要柏求所违决定技的最颂小扩查散条较宽电阻常最大萄允许公功耗已所决斗定的赛最小充扩散候条宽在设雀计时廉应取喂最大辫的一惑种扩散类电阻粉的最动小条想宽WRm狸in受三清种因纵素的北限制:b.基区疼电阻摸等效季模型c.衬底征电位牺与分音布电饭容集成施电路助中电按阻模剂型集成略电路买中电欣阻基件本是斑由各碰扩散枝层形欲成,罗除了外电阻辟本身唐,有扇反偏狠的PN结特敢性,凭带来附加擦的电拴阻和拜电容(寄生露参数)衬底s,n端接最高睬电位防止赔电阻愧器的pn结正偏伟使电喜阻失宜效晶体顽管有雾源电溜阻采用均晶体称管进窜行适爹当连塌接并缝使其周工作叫在一持定的触状态概,利议用它乱的导通万电阻作为曲电路夕中的齐电阻棉元件面使用双极拨晶体办管和MO那S晶体旋管都育可用救作有妙源电霜阻MO欲S管有咽源电冠阻器MO笛S有源品电阻靠及其I-申V曲线晶体织管有肌源寄搏生电汇阻N+PN+

P衬底IcR1R2R3R4R5Rc=夺R1+R2+白R3+肺R4+闯R5双极替晶体鼻管集集电区牙电阻集成粪电路映中集罪电区体电阻Rc要比障分立些管的习大。Rc的增磁大会影垒响高导频特项性和循开关刺性能。R1长方吸体电季阻R2埋层河拐角树体电钢阻R3梯形钻电阻R4埋层吩拐角卸体电侮阻R5长方丘体电老阻分别胜计算智出各缝区的爹电阻法后相帮加参看壳书:P.华15好2为方蝇便起江见常胳将集电奏极电词流流殿经的存区域价划分腐为五恋个区§最4.生3集成宽电路拥的互连访技术耳和电感互连矩线单片歉芯片解上器疫件之春间互信连:金属孙化工想艺,金停属铝态薄膜电路祝芯片项与外昂引线主之间膀的连也接(电路伟芯片压与系块统的镇互联):引线绝键合询工艺为保跳证模劈燕型的的精确会性和绣信号交的完姥整性仿,需响要对眨互连卵线的禁版图础结构姓加以移约束姓和进焦行规文整。在连捉接线笨传输刺大电注流时省,应党估计抓其电练流容真量并保莫留足烈够裕坊量。各种棍互连伸线设仿计应醋注意忘的问将题为减圈少信萄号或鸡电源逆引起个的损邻耗及灭减少妈芯片面积张,连姐线应尽量石短。为提势高集距成度寒,在席传输涉电流竭非常者弱时华如:MO卸S栅极泄,大集多数互连去线应以融制造裕工艺提供云的最粒小宽侍度来爽布线谎。集成但电路总电雀感可有以有序两种秃形式单匝之线圈予多匝升线圈多匝螺旋型线圈三.集成充电路读的电感多匝直角型线圈单匝线圈4.精4集成称器件喷和电摸路版丑图设陆计一.版图绑设计槽方式主要向规定站了掩宪模版旬各层歼图形绑的宽度、间隔、重叠和两个博独立在的层宴间距乞离等的狭最小伞允许盟值。版图臂设计纸规则正是连宏接电血路设约计者和电呜路生初产者怀之间春的桥吗梁PN+N-Si集电区基区发射区集电托极引童线基极引线

发射极引线P

N+PN外延NN+P+-PN结电视容微米财设计闲规则以微床米为某尺度诵表示雪版图笔最小的允许旧值得范大小浅。λ设计注规则以λ为基鸟本单浴位的拐几何调设计搭规则权。将版粘图规创定尺顾寸均既取为λ的整数淡倍来表枯示。有两差种设碍计规讯则:微米差设计政规则言,λ设计计规则控制爱掩模所版各殊层图方形的宽度、间隔和两个具独立雷的层泊间距计离实际犬工艺领中,λ值不慕能简奏单的暂按比封例压壮缩,只仍然耍保留棋微米设计宗规则按比奥例缩套小原鸭则CV规则吓是在滥保持图器件婚和电松路中评各点电位不变凉的条律件下谷,尽陈量来贪缩小材尺寸丈,以悟提高艘器件舅和电乳路的绞有关瓦性能。CE缩小甘规则催基本撒指导争思想舌是在MO太SF垦ET内部知电场不变滴的条猾件下息,通过详按比穿例缩京小器把件的遗纵向烈和横腐向尺谷寸(摸与此岁同时碎,电源遭电压貌和阈祸值电箩压也沙要与侮器件怀尺寸勺缩小虎相同上的倍绒数)揭,以提浩高跨撤导和昂减小六负载遣电容雁,从配而达望到增炒强集秘成电桥路性酬能的目胞的为了怒提高拍器件究和IC的频忌率、骡速度谨性能锻,就鞭需要缩小而器件跳的特住征尺寸。按芒比例南缩小排规则炮(sc话al准in宏g粱la茎w)就驶是为龟了方夹便设帮计集盾成电路(I眼C)所采邀取的哨一种探规则N外延集电区

N+埋层

p-SiP基区N+N+集成患电路扔工艺课流程友针对答大量宵应用丸的NP喘N管设箩计的PN梢P晶体唯管制誓作需她要采奴用与NP保N管兼结容的私技术衬底PN央P管发射剑区是药利用NP酱N晶体压管的榜基区壶兼容陕而成反的基区万就是跑原来运的外土延层集电脖区为婶衬底NP金N晶体慕管横向PN羽P管P型发咬射区螺和集烧电区某是在巨标准勿基区P扩散鞭流程放中形更成的N型基董区就富是外帜延层穿,基肌极的阴引线蒜区是盗在标糠准发绸射区N+扩散旅形成N外延集电区

N+埋层

p-SiP基区N+N+多极NP堵N管电流闻大,旦使电统流均俱匀分岂布。将集划电极情、基唉极、唉发射垦极分象为多普个电傻极,强电极芦用金榴属电垦极连接在型一起啄。集电谣区用谣一个肝埋层略,集词电极展引线唱孔处瘦要加N+扩散售。p1痒59图4.厅11和图4.克12双极击型集肃成电康路基刺本制遗造工溜艺相面应的俭版图第一爪次光骆刻N+埋层挣扩散侍孔光浙刻埋层守氧化外延第二岛次光撒刻P+隔离爆扩散亡孔光毫刻第三果次光猛刻P型基仁区扩戏散孔觉光刻第四肌次光微刻N+发射裁区扩矿散孔迷、集电息极引读线扩宿散孔炊光刻第五裤次光名刻引线从接触昨孔光悄刻第六惹次光广刻金属猛化内赠连线信光刻-反刻畜铝栅压适为零企时,腾沟道狮不存娘在,加上半一个筐正的馆栅压缎才能饿形成N型沟减道栅压哥为零块时,轧沟道赢已存在,秤加上蓝一个捆负的颂栅压才能畜使N型沟敬道消靠失栅压哥为零蕉时,旁沟道艇不存在,超加上石一个界负的皂栅压才能阴形成P型沟由道。栅压仆为零阀时,暗沟道锣已存在,躲加上凶一个刺正的械栅压可以林使P型沟萝道消嚼失硅栅CM配OS器件(反相础器)一个肃增强正型nM球OS和增牛强型PM崭OS组成CM帜OS反相浓器工蚕作原晨理输入换端高存电平辅时:nM茎OS管导肥通,pM效OS截止签,输转出端问通过绸导通的nM鼓OS管接半地,睬输出久端呈馆低电撤平输入塘端低雷电平枝时:pM辱OS管导买通,nM裕OS截止趁,输俩出端妖通过粮导通的pM切OS管接福到VDD上,可呈现痒高电蝇平N阱CM王OS设计逼规则表4.柔7列出阿的最养小分晕辨率贿的微称米规堤则与蓄规则健工艺炊的特歌征尺咱寸,骂版图嫁基本琴几何赤图形画及间撑隔MO言S自隔乐离,P型衬千底接运地(Vss),N阱区颜接VDD多晶因硅作伶引线援,为俊降低承电阻张,减绪小功斥耗,劝提高赖速度吹。多熔晶硅醒要重四掺杂N+减小腹接触匪电阻旋,金趟属与N+和P+接触蝇连接(欧姆解接触);金鸭属与课多晶静硅和遥衬底婆接触忧,需慈增大采接触付面积N阱硅仍栅CM歪OS工艺甲流程CM碧OS反相汁器版图找设计

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 危险品包装可视化设计的互动性研究考核试卷

- 五金行业区域一体化与数字经济发展融合考核试卷

- 处理设施生命周期成本分析考核试卷

- 绿色供应链与企业内部环境管理体系整合考核试卷

- 租赁设备租赁保险管理考核试卷

- 住宅风水与室内空气质量控制考核试卷

- 人脸识别在无人零售场景下的商品质检探讨考核试卷

- 2025年中国PU水晶胶数据监测研究报告

- 2025年中国IC测试座数据监测研究报告

- 2025年中国DSNG数字电视激励器数据监测研究报告

- 云南省玉溪市(2024年-2025年小学六年级语文)统编版小升初真题((上下)学期)试卷及答案

- 公安网络安全培训

- 唐山购房协议模板

- 旅拍运营方案

- 国开 电大《政治学原理》形考测试一答案

- 高中化学乙醇教学反思

- 如皋市直属机关遴选笔试真题

- 2022-2023学年山东省济南市高一下学期期末数学试题(解析版)

- 2022-2023学年安徽省阜阳市高一下学期期末教学质量统测数学试卷(解析版)

- 华东师大版数学七年级上册教案全册

- 医患之间暴力行为预防与处理管理制度

评论

0/150

提交评论