版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

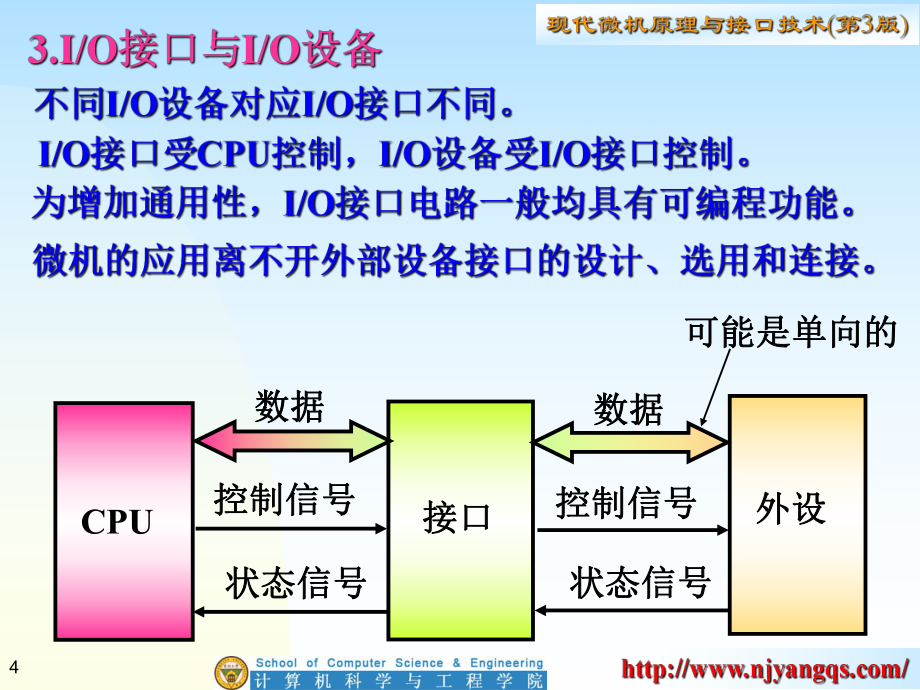

1、1第第5章章 输入输出与接口技术输入输出与接口技术 25.1 接口概述接口概述3 微机和微机和I/O设备的信息类型和格式可能不一样。设备的信息类型和格式可能不一样。 微机和微机和I/O设备信号传输处理的速度可能不匹配。设备信号传输处理的速度可能不匹配。 不用接口,不用接口, I/O直接接直接接CPU,随着外设增加,会,随着外设增加,会大大降低大大降低CPU的效率。的效率。 I/O直接接直接接CPU,会使外设硬件结构过于依赖,会使外设硬件结构过于依赖CPU,对外设本身发展不利。,对外设本身发展不利。4CPU接口接口外设外设数据数据数据数据控制信号控制信号控制信号控制信号状态信号状态信号状态信号状

2、态信号可能是单向的可能是单向的5通过寄存器或锁存器实现。通过寄存器或锁存器实现。接口中存放数据的寄存器或锁存器称之为接口中存放数据的寄存器或锁存器称之为接口中存放接口中存放CPU命令代码的寄存器称之为命令代码的寄存器称之为 接口中存放执行状态信息的寄存器称之为接口中存放执行状态信息的寄存器称之为CPU通过地址译码选择不同外设。通过地址译码选择不同外设。即即CPU通过地址译码选择不同通过地址译码选择不同I/O接口和接口和I/O接口中接口中连接的不同的设备。连接的不同的设备。协调总线信号与协调总线信号与I/O设备信号。设备信号。转换包括信号的逻辑关系、时序配合和电平转换。转换包括信号的逻辑关系、时

3、序配合和电平转换。增加接口的灵活性和智能性。增加接口的灵活性和智能性。6 接口由接口硬件和接口软件组成。接口由接口硬件和接口软件组成。7接口缓冲寄存器与外设间的数据交换;接口缓冲寄存器与外设间的数据交换;外设工作状态送给接口的状态寄存器;外设工作状态送给接口的状态寄存器;接口的内部控制逻辑控制外设工作的控制接口的内部控制逻辑控制外设工作的控制信号和同步信号。信号和同步信号。选择选择I/O接口中的不同寄存器接口中的不同寄存器(端口端口);命令或数据写入到相应寄存器,或者从相关命令或数据写入到相应寄存器,或者从相关寄存器读出数据或状态;寄存器读出数据或状态;控制命令的执行、时序、信号同步和片选;控

4、制命令的执行、时序、信号同步和片选;接口的部分工作状态信号。接口的部分工作状态信号。根据控制寄存器、状态寄存器、总线控制信号及外根据控制寄存器、状态寄存器、总线控制信号及外设状态信号控制设状态信号控制I/O接口的工作。接口的工作。8PS2鼠标鼠标PS2键盘键盘千兆网千兆网10/100M网卡网卡USB并行口并行口MIDI/游戏接口游戏接口VGA接口接口13941394a音箱音箱/线入线入/麦克风接口麦克风接口串行口串行口9声道输入声道输入前置扬声器输出前置扬声器输出麦克风输入麦克风输入中置与重低音中置与重低音后置扬声器输出后置扬声器输出侧置扬声器输出侧置扬声器输出10设置接口工作方式及初始条件。

5、设置接口工作方式及初始条件。CPU针对不同的针对不同的I/O设备有不同设备有不同的处理方式。如设置中断向量等。的处理方式。如设置中断向量等。完成接口任务的程序。完成接口任务的程序。对接口电路硬件保护及操作对接口电路硬件保护及操作系统中数据恢复。系统中数据恢复。提供人提供人-机对话手段。机对话手段。11是供是供CPU直接存取访问的接口中的寄存器或直接存取访问的接口中的寄存器或电路。电路。接口中的命令口、状态口和数据口均为接口中的命令口、状态口和数据口均为I/O端口。端口。是对接口中的不同寄存器或电路的编号,该编号加是对接口中的不同寄存器或电路的编号,该编号加上该接口的基地址称为该端口的上该接口的

6、基地址称为该端口的CPU通过向命令端口发命令来对接口,最终对设备通过向命令端口发命令来对接口,最终对设备进行控制。进行控制。一个接口中有多个一个接口中有多个I/O端口;端口;一个一个I/O端口可接受多种命令,对应多个寄存器。端口可接受多种命令,对应多个寄存器。5.2 I/O编址与访问编址与访问12一个一个I/O端口等同于一个存储器单元。端口等同于一个存储器单元。存储单元和存储单元和I/O端口统一编址。端口统一编址。 对对I/O端口的访问命令与对存储器单元访问相同,端口的访问命令与对存储器单元访问相同,不必使用专用不必使用专用I/O指令;指令; 外设数目或外设数目或I/O寄存器数几乎不受限制。寄

7、存器数几乎不受限制。 系统读写控制逻辑较简单。系统读写控制逻辑较简单。 I/O端口占用部分端口占用部分MEM空间,可用空间,可用MEM空间减小;空间减小; 对对MEM访问指令较长,执行速度较慢;访问指令较长,执行速度较慢; I/O端口地址译码时间较长。端口地址译码时间较长。MEMMEM空间空间I/OI/O空间空间N-1KK-10存储类指令存储类指令Motorola系列和系列和Apple 系列均采用此方式系列均采用此方式13 I/O端口地址空间与存储器地址空间相互独立。端口地址空间与存储器地址空间相互独立。Z-80系列和系列和x86系列均采用此方式。系列均采用此方式。 MEM地址空间不受地址空间

8、不受I/O端口地址空间影响;端口地址空间影响; I/O端口数量不多,占用地址线少,地址译码简端口数量不多,占用地址线少,地址译码简单,速度较快,使得此类指令执行速度快;单,速度较快,使得此类指令执行速度快; 使用专用使用专用I/O命令命令(IN/OUT),与,与MEM访问命令访问命令(LOAD/STORE、MOV)有明显区别有明显区别,便于理解和便于理解和检查。检查。MEMMEMI/OI/O设备设备N-1N-10 0存储类指令存储类指令I/OI/O类指令类指令K-1K-10 014支持支持I/O独立编址方式和独立编址方式和I/O统一编统一编址(存储器映象编址)方式。址(存储器映象编址)方式。仅

9、支持仅支持I/O独立编址方式。独立编址方式。 专用专用I/O指令增加指令系统复杂性,且指令增加指令系统复杂性,且I/O指令类型指令类型少,寻址方式也少,程序设计灵活性较差;少,寻址方式也少,程序设计灵活性较差; 要求处理器提供要求处理器提供MEMR#/MEMW#和和IOR#/IOW#两两组控制信号,增加了控制逻辑的复杂性。组控制信号,增加了控制逻辑的复杂性。15有有64K个独立编址的个独立编址的8位端口空间。位端口空间。两个连续两个连续8位端口可作为位端口可作为16位端口,位端口,4个连续的个连续的8位端口位端口可作为可作为32位端口处理。注意端口地址对齐。位端口处理。注意端口地址对齐。源于源

10、于IBM PC借用借用和和以及以及组成。组成。16I/O芯片名称芯片名称 地址范围地址范围 DMAC1DMAC2DMA页面寄存器页面寄存器 0000-001FH00C0-00DFH0080-009FH 中断控制器中断控制器1中断控制器中断控制器2 0020-003FH00A0-00BFH 定时器定时器并行接口芯片并行接口芯片(键盘接口键盘接口)RT/CMOS RAM协处理器(现保留)协处理器(现保留) 0040-005FH0060-006FH0070-007FH00F0-00FFH 17I/O接口名称接口名称 地址范围地址范围 游戏控制卡游戏控制卡 0200-020FH 并行口控制卡并行口控制

11、卡1并行口控制卡并行口控制卡2 0370-037FH0270-027FH 串行口控制卡串行口控制卡1串行口控制卡串行口控制卡2 03F8-03FFH02F8-02FFH 原型插件板原型插件板(用户可用用户可用) 0300-031FH 同步通信卡同步通信卡1同步通信卡同步通信卡2 03A0-03AF0380-038FH 单显单显MDA彩显彩显CGA彩显彩显EGA/VGA 03B0-03BFH03D0-03DFH03C0-03CFH 软驱控制卡软驱控制卡硬驱控制卡硬驱控制卡 03F0-03FFH01F0-01FFH PC网卡网卡 0360-036FH 18I/O端口支持直接寻址和间接寻址方式。端口

12、支持直接寻址和间接寻址方式。是使用一字节立即数寻址,端口寻址范围为是使用一字节立即数寻址,端口寻址范围为00HFFH共共256个。个。是使用是使用DX寄存器间接给出寄存器间接给出I/O端口地址,可端口地址,可寻址的范围是寻址的范围是0000HFFFFH共共64K个端口。个端口。IN、OUT。完成完成I/O端口和端口和EAX、AX、AL之间的数据传之间的数据传送,可使用直接寻址和间接寻址方式。送,可使用直接寻址和间接寻址方式。 举例:举例:mov dx, 3fdhmov al, 36h in al, dxout 43h, al19INSB/W/D、OUTSB/W/D。用用DX指定指定I/O端口地

13、址,输入端口地址,输入/输出时的目的输出时的目的/源源RAM地址用地址用ES:DI(EDI)/DS:SI(ESI)指定。指定。EFLAG寄存器中寄存器中DF位来决定地址加和减。位来决定地址加和减。通过前缀通过前缀REP在在I/O端口和连续的存储器空间端口和连续的存储器空间之间传送数据之间传送数据 CPU通过通过I/O指令对指令对I/O接口进行访问。接口进行访问。IN、OUT。inportb(inport)、outportb(outport)。_inp(_inpw)、_outp(_outpw)。20读取读取CMOS信息。信息。main() short int i, j; unsigned cha

14、r c_CmosMessage64; for (i=0;i=63;i+) j=i|0 x80 outportb(0 x70,j); c_CmosMessagei=inportb(0 x71) ; printf(CMOS信息读取完毕。信息读取完毕。n); 21或或A19A16/S6S322作业作业1 请参照上页请参照上页OUT 43H, AL 指令的时序图指令的时序图画出画出的时序图,假设从的时序图,假设从21H端端口中读到的数据是口中读到的数据是02H,21H是是8259芯片芯片的一个端口地址。的一个端口地址。23保护通过比较当前任务的特权级保护通过比较当前任务的特权级CPL和和的的IOPL字

15、段实现的。字段实现的。若若CPL IOPL,可执行,可执行IN、OUT、INS、OUTS、CLI、STI等敏感指令等敏感指令(对对IOPL敏感敏感);否则不行。;否则不行。每个任务都有自己的每个任务都有自己的IOPL,用以表示指定的,用以表示指定的I/O操作操作处于特权级的哪一级。它在处于特权级的哪一级。它在EFLAGS中。中。 0级特权的级特权的过程可通过过程可通过POPF和和IRET指令修改任务的指令修改任务的IOPL。 24I/O允许位映象用来修正允许位映象用来修正IOPL对对I/O敏感指令的影响,敏感指令的影响,允许低特权的程序访问某些允许低特权的程序访问某些I/O端口。端口。I/O允

16、许位映象是一个位向量,每位对应一个端口的允许位映象是一个位向量,每位对应一个端口的操作权限操作权限(0表示允许表示允许)。操作系统可通过改变任务操作系统可通过改变任务TSS中的中的I/O允许映象来允许映象来为某任务分配端口。(一定是在为某任务分配端口。(一定是在0级)级)25执行执行in, out指令指令CPL IOPL? IOPM相关位相关位=0? 进行进行I/O操作操作否否否否产生一个一产生一个一般保护异常般保护异常 是是是是是对所有是对所有VM都都起作用的权限机制,它以起作用的权限机制,它以位(位(bit)来代表每个端)来代表每个端口。某位为口。某位为1,则该代表,则该代表的端口被禁止访

17、问;某位的端口被禁止访问;某位为为0;则允许访问该位所;则允许访问该位所代表的端口。代表的端口。用以表示指定的用以表示指定的I/O操作处操作处于特权级的哪一级。它在于特权级的哪一级。它在EFLAGS中。中。当前段的当前段的I/O优先级,它实优先级,它实际上是际上是CS段选择符的第段选择符的第0第第1位。位。 26执行执行in, out指令指令IOPM相关位相关位=0? 进行进行I/O操作操作否否产生一个一产生一个一般保护异常般保护异常 是是27地址线低位直接组成。地址线低位直接组成。5.3 I/O端口地址译码方法端口地址译码方法其有效表明该接口芯片可以通过其有效表明该接口芯片可以通过系统总线与

18、系统总线与CPU进行数据交换进行数据交换使用使用IOW#/IOR#信号信号(有效有效)、AEN信号信号(无效无效)和地址和地址线高位(接口基地址)经过译码得到片选信号。线高位(接口基地址)经过译码得到片选信号。28接口中只有一个端口时可采用门电路构成。接口中只有一个端口时可采用门电路构成。 接口中有多个端口时一般采用译码器电路构成,常接口中有多个端口时一般采用译码器电路构成,常见的译码器有见的译码器有74LS138、74LS154等。等。G1=1,G2A # =G2B # =0。将复合的输入信号变为枚举的将复合的输入信号变为枚举的输出信号。输出信号。15Y0#Y7#ABCG2B#G2A#G11

19、4131211109712345674LS13829输输 入入输输 出出G G1 1G G2A2A#G#G2B2B# #C B AC B AY Y7 7 Y Y6 6 Y Y5 5 Y Y4 4 Y Y3 3 Y Y2 2 Y Y1 1 Y Y0 01 0 01 0 00 0 00 0 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 01 0 01 0 00 0 10 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 0 11 0 01 0 00 1 00 1 0 1 1 1 1 1 0 1 1 1 1 1 1 1 0 1 11 0 01 0 00 1 10 1

20、1 1 1 1 1 0 1 1 1 1 1 1 1 0 1 1 11 0 01 0 01 0 01 0 0 1 1 1 0 1 1 1 1 1 1 1 0 1 1 1 11 0 01 0 01 0 11 0 1 1 1 0 1 1 1 1 1 1 1 0 1 1 1 1 11 0 01 0 01 1 01 1 0 1 0 1 1 1 1 1 1 1 0 1 1 1 1 1 11 0 01 0 01 1 11 1 1 0 1 1 1 1 1 1 1 0 1 1 1 1 1 1 10 X X0 X XX X XX X X 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1X 1 XX

21、1 XX X XX X X 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1X X 1X X 1X X XX X X 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 130Y0#Y7#ABCG2B#G2A#G11514131211109712345674LS138A5A6A7A8A9AEN#DMACS#(8237)INTRCS#(8259)T/C CS#(8253)PPICS#(8255)WRTDMAPG#11WRTNMIREG#IOW#31DMA825982538255系统系统空闲空闲00H20H40H60H3FFH1FH3FH5FH7FH:数据总线数据总线地址总线

22、地址总线控制总线控制总线CPUCS#设设备备侧侧信信号号CS#设设备备侧侧信信号号82598253MEMY0Y71514131211109774LS13832当当P07Q07时,时, P=1,输出高电平。,输出高电平。当当P07=Q07时,时, P=0,输出低电平。,输出低电平。比较器和地址开关产生一个信号参与片选。比较器和地址开关产生一个信号参与片选。当系统时钟频率很高的时候,译码电路的延迟不能太大当系统时钟频率很高的时候,译码电路的延迟不能太大33用异或门代替比较器和地址开关比较。用异或门代替比较器和地址开关比较。=1=1=1=11 234 567891011121314VCCGND74LS136如用如用2片片74LS136代替代替74LS688。3=12;6=4 5; 8=9 10;11=12 13;异或门的输入端分别异或门的输入端分别接地址线和开关线。接地址线和开关线。各异或门的输出各异或门的输出“或或”的结果。的结果。34?35300H301H302H303H304H305H306H307H36Y0Y7ABCG2BG2AG11514131211109712345674LS138_AEN# 001FH 405FH 809FH_

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025年标准维修服务合同示范文本

- 世纪佳缘 合同样本

- 城镇房屋拆迁方案范本

- 2025年的装修施工合同样本

- 推动团队创新的策略计划

- 书印刷供货合同样本

- 养鸭租地合同样本

- 2025装饰材料供应合同范本

- 出售二手房贷款合同标准文本

- UPS采购合同标准文本

- 2025年的租房合同范本标准版

- 2025-2030中国眼药水和眼药膏行业市场发展趋势与前景展望战略研究报告

- 焊接知识培训课件模板

- 2022年陕西省普通高校职业教育单独招生统一考试模拟题

- 静脉药物调配中心PIVAS静脉用药配置中心静脉药物配置中心静配中心调配工作简介培训教学课件

- 常压热水锅炉产品质量证明书

- 出厂检验报告范本(共3页)

- 第三节 意大利现代设计

- 自体输血知情同意书

- 苏教版小学数学二年级下册单元测试题及答案(全册)

- 医疗卫生培训消毒知识培训PPT

评论

0/150

提交评论