版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

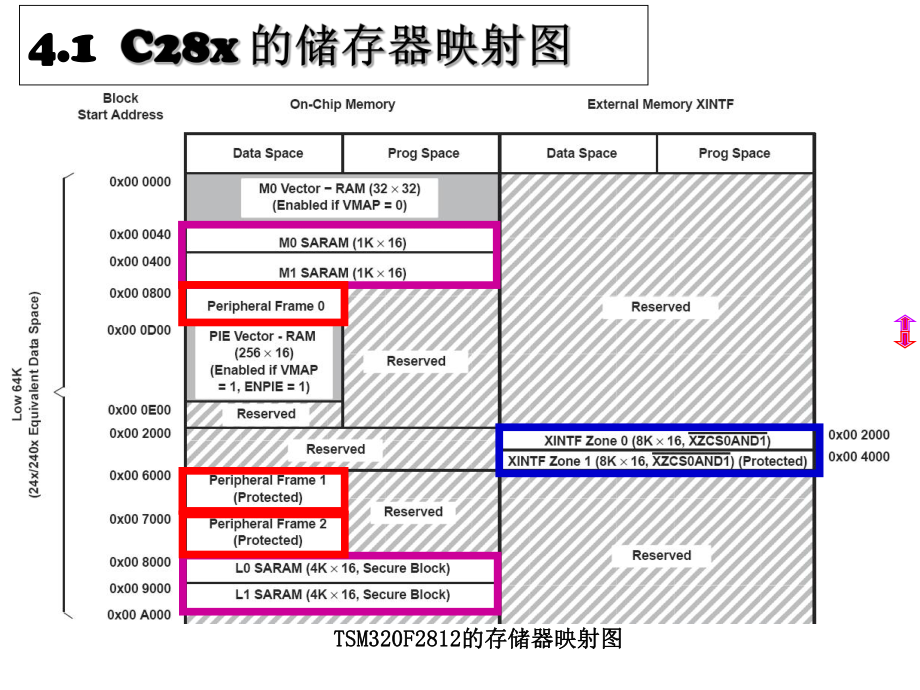

1、4 4 4.1 4.1 存储空间的映射存储空间的映射图图4.3 4.3 外部存储器接口(外部存储器接口(XINTFXINTF)4.14.1 TSM320F2812TSM320F2812的存储器映射图的存储器映射图4.14.1 TSM320F2812TSM320F2812的存储器映射图(续)的存储器映射图(续)4.1.14.1.1 PF04.1.24.1.2 PF14.1.34.1.3 PF24.24.2 (1 1) 特点特点(2 2)电源模式)电源模式(4 4)流水线模式)流水线模式(5 5) 相关寄存器相关寄存器(3 3)Flash/OTPFlash/OTP的访问的访问4.2.14.2.1

2、(1) (1) 多扇区多扇区(2) (2) 代码安全性代码安全性(3) (3) 低功耗模式低功耗模式(4) (4) 基于基于CPUCPU频率可进行调整的配置等待周期频率可进行调整的配置等待周期(5) (5) 可改善性能的可改善性能的FlashFlash流水线模式流水线模式(1)(1) 4.2.24.2.2 v CPUCPU的访问将自动初始化的访问将自动初始化Flash/OTPFlash/OTP的电源模式,使其转换到工作的电源模式,使其转换到工作状态或读状态。状态或读状态。 u这是这是DSCDSC复位后的状态复位后的状态u存储体及其驱动(激励)电路处于休眠状态(功耗最低)。存储体及其驱动(激励)

3、电路处于休眠状态(功耗最低)。u CPUCPU的读操作或对的读操作或对Flash/OTPFlash/OTP存储器的取指访问都将暂停存储器的取指访问都将暂停CPUCPU。v CPUCPU的访问将自动初始化的访问将自动初始化Flash/OTPFlash/OTP的电源模式,使其转换到工作状的电源模式,使其转换到工作状态或读状态。态或读状态。 u存储体及其驱动(激励)电路处于待机状态。存储体及其驱动(激励)电路处于待机状态。u CPUCPU的读操作或对的读操作或对Flash/OTPFlash/OTP存储器的取指访问都将暂停存储器的取指访问都将暂停CPUCPU。v FlashFlash流水线的预取机制可

4、以改善取指性能流水线的预取机制可以改善取指性能 。 u存储体及其驱动(激励)电路处于工作状态(功耗最大)。存储体及其驱动(激励)电路处于工作状态(功耗最大)。u CPUCPU的读操作或对的读操作或对FlashFlash或或OTPOTP存储器映像区的取指访问的等待状态均由存储器映像区的取指访问的等待状态均由FBANKWAITFBANKWAIT或或FOTPWAITFOTPWAIT寄存器控制寄存器控制 。u 读操作或从读操作或从Flash/OTPFlash/OTP中执行指令,中执行指令,Flash/OTPFlash/OTP存储体存储体及其驱动(激励)电及其驱动(激励)电路路处于相同的电源模式处于相同

5、的电源模式 。u 改变电源寄存器的改变电源寄存器的PWRPWR模式位模式位v 同时把同时把Flash/OTPFlash/OTP存储体变为低功耗状态存储体变为低功耗状态v 需要通过执行需要通过执行Flash/OTPFlash/OTP存储器之外的代码才能访问该寄存器。存储器之外的代码才能访问该寄存器。(1) 32(1) 32位取指位取指(2) 16(2) 16位或位或3232位数据空间读位数据空间读(3) 16(3) 16位程序空间读位程序空间读(1) Flash(1) Flash的随机访问的随机访问(2) Flash(2) Flash的页访问的页访问(3) OTP(3) OTP的访问的访问配置寄

6、存器配置寄存器等待等待8 8个周期个周期转移到或调用转移到或调用配置代码配置代码返回返回继续执行继续执行XINTF, SARAM,Flash, OTP, ROMXINTF, SARAMXINTF, SARAM,Flash, OTP, ROM由于CPU流水线造成的8个等待FSTATUSFSTATUSVDD3V Status Latch BitWhen set, this bit indicates that the 3 VSTAT signal from the pump module went to a high level. This signal indicates that the 3

7、V supply went out of allowable range. This bit is cleared by writing a 1, writes of 0 are ignored.FSTATUSFSTATUSBank and Pump Standby To Active Wait Counter Status BitIf the bit is set, then the counter is counting; If the bit is 0, then the counter is not counting.Bank and Pump Sleep To Standby Wai

8、t Counter Status BitPower Modes Status BitsFSTDBYWAITFSTDBYWAIT1Bank and Pump Sleep To Standby Wait CountBank and Pump Sleep To Standby Wait CountThe power mode for the bank and pump are set for standby mode. The counter then counts down to zero before the PWRS bits are set to standby mode. If a CPU

9、 read or fetch access to the Flash bank/OTP initiated the process, the CPU is stalled until the access completes.The STDBYWAIT bits specify the number of CPU clock cycles (0.511 SYSCLKOUT cycles) of delay. This register should be left in its default stateFACTIVEWAITFACTIVEWAITFBANKWAITFBANKWAIT1PAGE

10、WAIT PAGEWAIT Flash Paged Read Wait StatesFlash Paged Read Wait StatesThese register bits specify the number of wait states for a paged read operation in CPU clock cycles (0.15 SYSCLKOUT cycles) to the banks.1PAGEWAIT PAGEWAIT Flash Random Read Wait StatesFlash Random Read Wait StatesYou must set RA

11、NDWAIT to a value greater than or equal to the PAGEWAIT setting. No hardware is provided to detect a PAGEWAIT value that is greater then RANDWAIT.When enabling Flash pipeline mode, you must set PAGEWAIT and RANDWAIT to a value greater than zero.FOTPWAITFOTPWAIT1OTPWAIT OTPWAIT OTP Read Wait StatesOT

12、P Read Wait StatesThese register bits specify the number of wait states for a read operation in CPU clock cycles (0.31 SYSCLKOUT cycles) to the OTP. OTPWAIT must be set greater than 0. The device-specific data sheet for the minimum time required for an OTP or ROM access.4.3 4.3 外部外部存储器接口(存储器接口(XINTF

13、)(1 1) 外部存储器接口信号外部存储器接口信号(5 5)XINTFXINTF的时序图的时序图(2 2)XINTF XINTF 的配置的配置(3 3)XINTF XINTF 的配置寄存器的配置寄存器(4 4)XINTF XINTF 的配置小结的配置小结(6 6)XINTFXINTF的设计示例的设计示例u 在改变在改变XINTFXINTF的配置和时序的过程中,不允许对的配置和时序的过程中,不允许对XINTFXINTF进行存取;进行存取;u 堆栈也不能位于外部存储区。堆栈也不能位于外部存储区。uXINTF XINTF 的时序约束的时序约束X2TIMINGLEADDECN= XRDLEAD2,XR

14、DLEAD=13uXRDLEADXRDLEADp如果如果 XRDLEAD0XRDLEAD0p如果如果 XRDLEADXRDLEAD0 0, 无效无效X2TIMINGACTIVEDECN= XRDACTIVE2,XRDACTIVE=07uXRDACTIVEXRDACTIVEX2TIMINGTRAILDECN= XRDTRAIL2,XRDTRAIL=03uXRDTRAILXRDTRAILX2TIMINGLEADDECN= XWRLEAD2,XWRLEAD=13uXWRLEADXWRLEADp如果如果 XWRLEAD0XWRLEAD0p如果如果 XWRLEADXWRLEAD0 0, 无效无效X2TI

15、MINGACTIVEDECN= XWRACTIVE2,XWRACTIVE=07uXWRACTIVEXWRACTIVEX2TIMINGTRAILDECN= XWRTRAIL2,XWRTRAIL=03uXRDTRAILXRDTRAILTableTable.XTIMCLK XTIMCLK 和和 XCLKOUTXCLKOUT的关系图的关系图.一般的读时序图一般的读时序图.一般的写时序图一般的写时序图.XTIMCLK XTIMCLK 和和 XCLKOUTXCLKOUT的关系图的关系图.一般的读时序图一般的读时序图.一般的写时序图一般的写时序图Taking the CY7C1061AV33 for exa

16、mpleu 16-Mbit (1M x 16) Static RAM16-Mbit (1M x 16) Static RAMu High speed: tHigh speed: tAAAA = 10 ns = 10 nsu Low active power: 990 mW (max)Low active power: 990 mW (max)u Operating voltages of 3.3 Operating voltages of 3.3 0.3V 0.3Vu 2.0V data retention2.0V data retentionu Automatic power down wh

17、en deselectedAutomatic power down when deselectedu TTL compatible inputs and outputsTTL compatible inputs and outputsu Easy memory expansion with CE1 and CE2 Easy memory expansion with CE1 and CE2 featuresfeaturesu package :54-pin TSOP II and FBGApackage :54-pin TSOP II and FBGARead Waveform No.1 Read Waveform No.1 Read Waveform No

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 勘察合同范例 付款方式

- 公司有效合同范例

- 协调员 合同范例

- 厂区维修框架合同范例

- 卖旧货合同范例

- 口罩订购合同范例

- 参茸购销合同范例

- 发货送货合同范例

- 博罗网签合同范例

- 化粪池合作合同范本

- 2025年浙江省中考英语二轮题型突破讲义:选择型阅读

- 2025年皖西卫生职业学院单招职业倾向性测试题库及答案1套

- 颌面骨囊肿肿瘤和瘤样病变影像诊断讲解

- 逐梦青春共创未来

- 【物理】弹力 同步练习+2024-2025学年人教版物理八年级下册

- 口腔医学主治医师职称考试统考历年真题及答案

- 2025年中国中信集团招聘笔试参考题库含答案解析

- 部编版六年级语文下册基础知识专项练习(带答案)

- 2024-2030年中国除湿机行业发展现状及销售模式分析报告版

- 财经法规和会计职业道德试题库(含答案)

- 幼儿园教职员工健康监测方案

评论

0/150

提交评论