版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

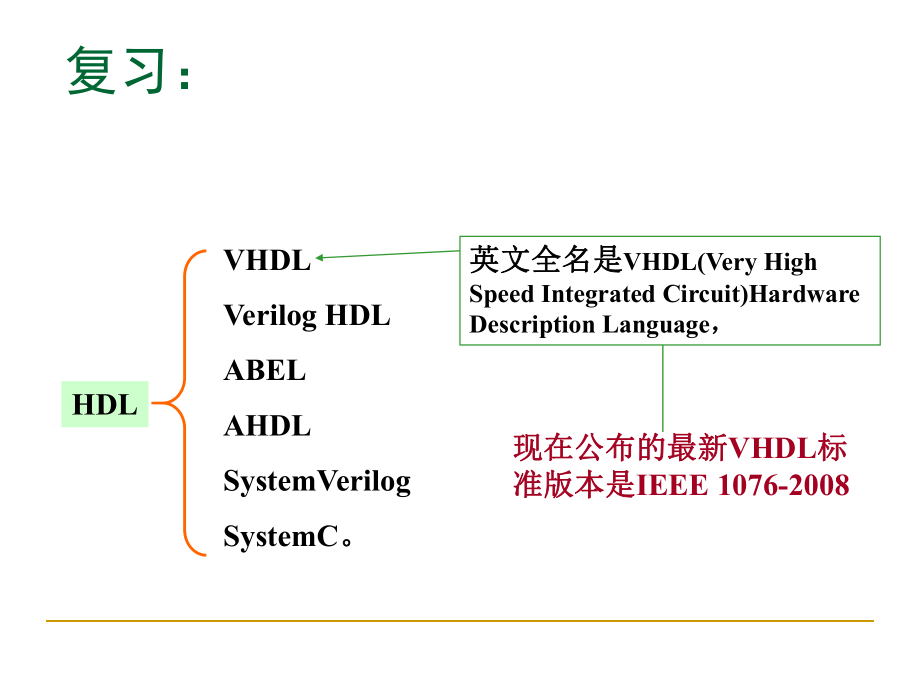

1、本章需要重点掌握的知识本章需要重点掌握的知识n熟悉熟悉EDA集成开发环境集成开发环境Quartus II的设计流程;的设计流程;n掌握硬件描述语言掌握硬件描述语言VHDL的基本模型机构;的基本模型机构;HDL VHDLVerilog HDLABELAHDLSystemVerilogSystemC。 英文全名是英文全名是VHDL(Very High Speed Integrated Circuit)Hardware Description Language, 现在公布的最新现在公布的最新VHDL标标准版本是准版本是IEEE 1076-2008 复习: VHDL语言的特点:n VHDL语言具有很强

2、的电路描述和建模能力,能从多个层次对数字系统进行建模和描述,从而大大简化了硬件设计任务,提高了设计效率和可靠性。n VHDL具有与具体硬件电路无关和与设计平台无关的特性,并且具有良好的电路行为描述和系统描述的能力,使设计者可以专心致力于其功能的实现,而不需要对不影响功能的与工艺有关的因素花费过多的时间和精力。原理图原理图/VHDL文本编辑文本编辑综合综合FPGA/CPLD适配适配FPGA/CPLD编程下载编程下载FPGA/CPLD器件和电路系统时序与功能时序与功能门级仿真门级仿真1、功能仿真、功能仿真2、时序仿真、时序仿真逻辑综合器逻辑综合器结构综合器结构综合器1、isp方式下载方式下载 2、

3、JTAG方式下载方式下载 3、针对、针对SRAM结构的配置结构的配置 4、OTP器件编程器件编程 功能仿真功能仿真FPGAFPGACPLDCPLD设计流程设计流程应用应用FPGA/CPLD的的EDA开发流程开发流程:HDL文本输入文本输入Step 1:设计输入:设计输入(原理图原理图HDL文本编辑文本编辑) 这种方式这种方式与传统的计算机软件语言编辑输入基本与传统的计算机软件语言编辑输入基本一致一致。就是将使用了某种硬件描述语言。就是将使用了某种硬件描述语言(HDL)(HDL)的电的电路设计文本,如路设计文本,如VHDLVHDL或或VerilogVerilog的源程序,进行编的源程序,进行编辑

4、输入。辑输入。 可以说,应用可以说,应用HDLHDL的文本输入方法克服了原理图的文本输入方法克服了原理图输入法存在的所有弊端,为输入法存在的所有弊端,为EDAEDA技术的应用和发展打技术的应用和发展打开了一个广阔的天地。开了一个广阔的天地。Step 2:综合 整个综合过程就是将设计者在整个综合过程就是将设计者在EDAEDA平台上编辑平台上编辑输入的输入的HDLHDL文本、原理图或状态图形描述,依据文本、原理图或状态图形描述,依据给定的硬件结构组件和约束控制条件进行给定的硬件结构组件和约束控制条件进行编译编译、优化、转换和综合优化、转换和综合,最终获得门级电路甚至更底,最终获得门级电路甚至更底层

5、的电路描述网表文件。层的电路描述网表文件。 它的功能就是将软件描述与给定的硬件结构它的功能就是将软件描述与给定的硬件结构用某种网表文件的方式对应起来,成为相应互的用某种网表文件的方式对应起来,成为相应互的映射关系。映射关系。Step 3:适配 适配器也称适配器也称结构综合器结构综合器,适配器就是将综合后,适配器就是将综合后网表文件针对某一具体的目标器件进行逻辑映射操网表文件针对某一具体的目标器件进行逻辑映射操作,其中包括底层器件配置、逻辑分割、优化、布作,其中包括底层器件配置、逻辑分割、优化、布局布线操作局布线操作, ,使之产生最终的下载文件,如使之产生最终的下载文件,如JEDECJEDEC、

6、JamJam格式的文件。格式的文件。 适配完成后可以利用适配所产生的仿真文件作适配完成后可以利用适配所产生的仿真文件作精确的时序仿真,同时产生可用于编程的文件。精确的时序仿真,同时产生可用于编程的文件。Step 4: 时序仿真与功能仿真时序仿真功能仿真 就是接近真实器件运行特性的仿真,就是接近真实器件运行特性的仿真,仿真文件中己包含了器件硬件特性参数,仿真文件中己包含了器件硬件特性参数,因而,仿真精度高。因而,仿真精度高。 是直接对是直接对VHDL、原理图描述或其他、原理图描述或其他描述形式的逻辑功能进行测试模拟,以了解描述形式的逻辑功能进行测试模拟,以了解其实现的功能是否满足原设计的要求的过

7、程,其实现的功能是否满足原设计的要求的过程,仿真过程不涉及任何具体器件的硬件特性。仿真过程不涉及任何具体器件的硬件特性。Step5: 编程下载 通 常 , 将 对通 常 , 将 对 C P L DC P L D 的 下 载 称 为 编 程的 下 载 称 为 编 程(Program)(Program),对,对FPGAFPGA中的中的SRAMSRAM进行直接下载进行直接下载的方式称为配置的方式称为配置(Configure)(Configure),但对于,但对于OTP OTP FPGAFPGA的下载和对的下载和对FPGAFPGA的专用配置的专用配置ROMROM的下载的下载仍称为编程。仍称为编程。St

8、ep 6: 硬件测试 最后是将含有载入了设计的最后是将含有载入了设计的FPGAFPGA或或CPLDCPLD的硬件系统进行统一测的硬件系统进行统一测试,以便最终验证设计项目在目标试,以便最终验证设计项目在目标系统上的实际工作情况,以排除错系统上的实际工作情况,以排除错误,改进设计。误,改进设计。Quartus II是是Altera提供的提供的FPGA/CPLD开发集成环境开发集成环境 Quartus II设计流程设计流程 VHDL VHDL 程序程序 库的调用库的调用 程序包的调用程序包的调用 实体描述实体描述 结构体描述结构体描述LIBRARY IEEE;LIBRARY IEEE;USE IE

9、EE.std_logic_1164.all;USE IEEE.std_logic_1164.all;ENTITYENTITY MUX2 IS MUX2 IS PORTPORT (d0,d1: (d0,d1:IN IN std_logic;std_logic; sel: sel:IN IN std_logic;std_logic; q: q:OUTOUT std_logic);std_logic);END END ENTITY;ENTITY;ARCHITECTUREARCHITECTURE behav OF MUX2 ISbehav OF MUX2 ISBEGINBEGIN PROCESS PR

10、OCESS (d0,d1,sel)(d0,d1,sel) BEGIN BEGIN IFIF sel=0 sel=0 THENTHEN q=d0; q=d0; ELSIFELSIF sel=1 sel=1 THENTHEN q=d1; q=d1; ELSEELSE q=Z;q=Z; END IF;END IF; END PROCESSEND PROCESS; ;END behav;END behav;用于说明设计系统用于说明设计系统的外部接口信息,的外部接口信息,具有唯一性具有唯一性描述相应实体的行描述相应实体的行为、功能或电路结为、功能或电路结构构本章内容:本章内容: 基本的基本的VHDL模型

11、结构模型结构实体(实体(ENTITYENTITY)包括)包括实体名实体名、类属参数说明类属参数说明、端端口说明口说明三部分组成。三部分组成。格式格式 :ENTITY ENTITY 实体名实体名 ISIS 类属参数说明类属参数说明 ; 端口说明端口说明 ;ENDENDENTITY ENTITY 实体名实体名 ;通常用于说明通常用于说明静态信息静态信息GENERIC(常数名:数据类型:设定值);(常数名:数据类型:设定值);提供外部接口信息提供外部接口信息PORT(端口名:端口方向端口名:端口方向 数据类型数据类型);5.1 实体 类属声明类属声明是设计者向设计实体传递的信息,包括数据通道宽度、信

12、号宽度、实体中子元件的数目、实体的延时特性和负载特性等静态信息: GENERICGENERIC(CONSTANTCONSTANT名称名称 :IN IN 类属类型类属类型 := := 缺省缺省值值 ; );); 端口声明端口声明是描述设计实体的输入和输出特性的定义部分,它包括端口的信号名称、信号模式、信号类型和仿真初始值等信息: PORTPORT(SIGNALSIGNAL名称名称 : 信号模式信号模式 信号类型信号类型BUS:= BUS:= 仿真初始值仿真初始值 ; );); 在例题中,给出了1位全加器的实体声明,实体中给出了该全加器的端口声明:例例 1 1位全加器位全加器ENTITY ENTI

13、TY full_adder IS IS - 实体声明 PORT PORT (a,b,c_in:ININ Bit; - 端口声明 sum,c_out:OUTOUT Bit);ENDEND full_adder; 上述实体声明与右图是相互对应的。可见已知一个电路的逻辑框图,就可以写出对应的实体声明,反之亦然。 full_adderabc_insumc_out 从下面的例子,我们来看端口声明和类属声明的作用,在该例中类属n是锁存器的位数,缺省值为8:例例 高电平锁存的高电平锁存的n n位锁存器位锁存器ENTITYENTITY latch ISIS GENERIC GENERIC(n:Positive

14、 := 8); PORT PORT (eg:ININ Bit; d:ININ Bit_Vector (n-1 DOWNTO 0DOWNTO 0); q:OUTOUT Bit_Vector(n-1 DOWNTO 0DOWNTO 0);ENDEND latch;ARCHITECTUREARCHITECTURE latch_eg OF OF latch ISISBEGINBEGIN PROCESSPROCESS(eg) BEGINBEGIN IFIF eg=1 THENTHEN q = d;ENDEND IFIF;ENDEND PROCESSPROCESS;ENDEND latch_eg; 端口方向

15、n IN :IN定义的通道为单向输入输入模式,规定数据只能通过此端口被读入实体中。n OUT :OUT定义的通道为单向输出输出模式,规定数据只能通过此端口从实体向外流出,或者说可以将实体中的数据向此端口赋值。端口方向nINOUT : INOUTINOUT为输入输出双向端口,即从端口内部为输入输出双向端口,即从端口内部看,可以对端口进行赋值,即输出数据。也可以从此看,可以对端口进行赋值,即输出数据。也可以从此端口读入数据,即输入。如端口读入数据,即输入。如RAMRAM的数据端口,单片机的数据端口,单片机的的I/OI/O口。口。n BUFFER :输出缓冲。输出缓冲。 BUFFERBUFFER的功

16、能与的功能与INOUTINOUT类似,区别在于当需要输入类似,区别在于当需要输入数据时,只允许内部回读北部产生的输出信号数据时,只允许内部回读北部产生的输出信号, ,即反即反馈。如计数器的设计,可将计数器输出的计数信号回馈。如计数器的设计,可将计数器输出的计数信号回读,以作下一计数值的初值。与读,以作下一计数值的初值。与INOUTINOUT模式相比,模式相比,BUFFERBUFFER回读(输入)的信号不是由外部输入的,而是回读(输入)的信号不是由外部输入的,而是由内部产生、向外输出的信号。由内部产生、向外输出的信号。就是说就是说buffer buffer 仅仅仅仅是一个数据缓存器,不能用于是一

17、个数据缓存器,不能用于IOIO输出!输出!ExampleExample:ENTITY ENTITY my_design my_design ISISPORTPORT(d:(d:ININ std_logic_vector(15 DOWNTO 0); std_logic_vector(15 DOWNTO 0); clk,reset,oe: clk,reset,oe:ININ std_logic; std_logic; q: q:OUTOUT std_logic_vector(15 DOWNTO 0); std_logic_vector(15 DOWNTO 0); ad: ad:INOUTINOUT

18、 std_logic_vector(15 DOWNTO 0); std_logic_vector(15 DOWNTO 0); int: int:BUFFER BUFFER std_logic;std_logic; as: as:OUTOUT std_logic); std_logic);END my_design;END my_design;结构体(结构体(ARCHITECTUREARCHITECTURE)是设计实体的具体描述,)是设计实体的具体描述,指明设计实体的具体行为、所用元件及连接关系。指明设计实体的具体行为、所用元件及连接关系。由由定义说明定义说明和和具体功能具体功能描述两部分组成。

19、描述两部分组成。格式格式 :ARCHITECTUREARCHITECTURE 结构体名结构体名 OF OF 实体号名实体号名 ISIS 定义语句定义语句 信号信号(signalsignal);); 常数常数(constantconstant);); 数据类型数据类型(typetype);); 函数函数(functionfunction);); 元件元件(componentcomponent)等;)等;BEGINBEGIN 并行处理语句并行处理语句 ;END END 结构体名;结构体名;注意:注意:定义语句定义语句只对本结构体有只对本结构体有效。效。结构体名应结构体名应有明确意义有明确意义并行处

20、理并行处理是是VHDL的特点的特点5.2 结构体ExampleExample:半加器:半加器LibraryLibrary IEEE; IEEE;Use ieee.std_logic_1164.all;Use ieee.std_logic_1164.all;EntityEntity half_adder is half_adder is port (X,Y: in bit; sum, carry: out port (X,Y: in bit; sum, carry: out bit);bit);end half_adder;end half_adder;ArchitectureArchitect

21、ure dataflow of half_adder is dataflow of half_adder isbegin begin - -并行处理语句并行处理语句 sum = X xor Y; sum = X xor Y; carry =X and Y; carry =X and Y;End dataflow;End dataflow;注意:仿真注意:仿真时波形考虑时波形考虑了延时。了延时。5.2 结构体传统描述方式传统描述方式用与门、非门、用与门、非门、或门等具体底层或门等具体底层器件来组成器件来组成LIBRARY IEEE;LIBRARY IEEE;USE IEEE.std_logic_

22、1164.all;USE IEEE.std_logic_1164.all;ENTITYENTITY MUX2 IS MUX2 IS PORTPORT (d0,d1: (d0,d1:IN IN std_logic;std_logic; sel: sel:IN IN std_logic;std_logic; q: q:OUT OUT std_logic);std_logic);END END ENTITY;ENTITY;ARCHITECTURE ARCHITECTURE behav OF MUX2 ISbehav OF MUX2 ISBEGINBEGIN PROCESSPROCESS (d0,d1

23、,sel) (d0,d1,sel) BEGIN BEGIN IFIF sel=0 THEN sel=0 THEN q=d0; q=d0; ELSIF ELSIF sel=1 THENsel=1 THEN q=d1; q=d1; ELSE ELSE q=Z;q=Z; END IF;END IF; END PROCESS END PROCESS; ;END behav;END behav;VHDLVHDL描述描述程序包调用程序包调用实体描述实体描述结构体描述结构体描述库的调用库的调用描述实例VHDLVHDL的结构体描述方式的结构体描述方式: :通常根据描述的对象把结构体命名为通常根据描述的对象把结

24、构体命名为 structstruct(structuralstructural)结构描述结构描述(逻辑图)(逻辑图)描述该设计实体中电路元件之间的连接关系描述该设计实体中电路元件之间的连接关系 behav(behavior behav(behavior)行为描述行为描述(真值表、状态(真值表、状态图)图)描述该设计实体中电路模块的行为功能描述该设计实体中电路模块的行为功能 rtl rtl寄存器传输描述寄存器传输描述(逻辑表达式、布尔方(逻辑表达式、布尔方程)程)描述数据在该设计实体中通过寄存器的传输和变换描述数据在该设计实体中通过寄存器的传输和变换图2.2 2选1多路选择器逻辑图 例:图2.2

25、所示的是2选1多路选择器的逻辑电路图,它含有1个非门(U0)、3个2输入端与非门(U1、U2、U3)和四个端口(a、b、c、out1) 例例2-4 22-4 2选选1 1多路选择器多路选择器 (课本(课本3535页)页) 描述风格:n 结构描述 nRTL描述n 行为描述 n 结构体mux_arch1:结构描述。 它描述了设计实体mux的硬件是如何构成的,即构成设计实体mux的各个元件之间的连接关系。n 结构体mux_arch2:RTL描述。 它描述了设计实体mux的数据从输入到输出的流向,同时也隐含了设计实体mux的另一种硬件结构。n 结构体mux_arch3:行为描述。 它描述了设计实体mu

26、x的输出端口与输入端口之间的行为关系,但不包含任何结构信息。 思考题: 1.例2-1中的1位全加器是什么描述风格? 2.试写出1位全加器的另外2种风格的描述。 留在实验课上验证!2.4 VHDL的标识符在数字系统的在数字系统的VHDLVHDL描述中,描述中,实实体、结构体、子程序、元件、对象、体、结构体、子程序、元件、对象、属性和语句标号等属性和语句标号等用户的定义项,用户的定义项,都必须用标识符来命名。都必须用标识符来命名。标识符n有效字符包括:有效字符包括:英文字母、数字、下划线英文字母、数字、下划线n必须是字母打头必须是字母打头n下划线的前后都必须有字母或数字下划线的前后都必须有字母或数

27、字n不区分大小写不区分大小写某些标识符,例如某些标识符,例如ARCHITECTUREARCHITECTURE、BEGINBEGIN、ENDEND和和ENTITYENTITY等等,在等等,在VHDLVHDL中有固定的含义,中有固定的含义,是是VHDLVHDL的保留字(列于附录的保留字(列于附录A A,并且在本书的,并且在本书的例子中用黑体字表示),不能用来命名用户的例子中用黑体字表示),不能用来命名用户的定义项。定义项。为了便于阅读为了便于阅读VHDLVHDL文档,建议文档,建议VHDLVHDL保留字保留字使用大写字母,而用户定义的标识符使用小写使用大写字母,而用户定义的标识符使用小写字母或者大

28、小写字母组合。字母或者大小写字母组合。建议用户在定义标识符时,应当采用建议用户在定义标识符时,应当采用有意义的有意义的名称名称来命名信号、变量、常量等对象,函数、过程来命名信号、变量、常量等对象,函数、过程等子程序,和元件、属性、语句标号等等。例如,等子程序,和元件、属性、语句标号等等。例如,命名存储器地址,用命名存储器地址,用mem_addr命名。命名。对于低电平有效的信号,以对于低电平有效的信号,以“_b”或者或者“_n”作作为结尾,并在整个设计中一直采用这种命名规则。为结尾,并在整个设计中一直采用这种命名规则。在整个设计中,采用统一的时钟信号和复位信在整个设计中,采用统一的时钟信号和复位

29、信号名称。例如号名称。例如“clk”和和“reset”或者或者“reset_n”。对。对于来自同一时钟源但频率不同的时钟(由同一时钟于来自同一时钟源但频率不同的时钟(由同一时钟源的不同分频得到),使用源的不同分频得到),使用“clk1”、“clk2”等命等命名。名。例: 合法的标示符nmy_counter nDeconder_1n FFTnSig_Nnstate0n注:不区分大小写n SAT,sat被认为是同一个标示符例: 非法的标示符n_my_counter n my_counternDeconder-1n 2FFTnSig#Nnentitynlibrary 为了免受为了免受VHDL87VH

30、DL87对定义标识符的限制,在对定义标识符的限制,在VHDL93VHDL93中引中引入了扩展标识符,使标识符的定义更为灵活。入了扩展标识符,使标识符的定义更为灵活。 扩展标识符由一对反斜线之间的任何字符序列构成。如果扩展标识符由一对反斜线之间的任何字符序列构成。如果字符序列中包含有反斜线字符序列中包含有反斜线,则用双写的反斜线,则用双写的反斜线作为一个作为一个字符。字符。 扩展标识符取消了基本标识符中的所有限制:扩展标识符扩展标识符取消了基本标识符中的所有限制:扩展标识符可以使用任何的字符;可以以任何字符开头;可以使用任何的字符;可以以任何字符开头;区分大小写等等。区分大小写等等。每一个扩展标

31、识符与任何的基本标识符都是不相同的,因此也每一个扩展标识符与任何的基本标识符都是不相同的,因此也不同于任何一个保留字。不同于任何一个保留字。 例如:例如: ENTITYENTITY和和entityentity是两个不同的标识符,而且也不是保是两个不同的标识符,而且也不是保留字;留字; MUXMUX、MUXMUX、muxmux和和MuxMux是四个不同的标识符;是四个不同的标识符; c:filec:file是由是由7 7个字符构成的扩展标识符个字符构成的扩展标识符c:filec:file。在在VHDLVHDL语言中,可以语言中,可以赋值赋值的客体称为的客体称为对象对象。要掌握好这三种要掌握好这三

32、种数据对象的区别数据对象的区别及其应用及其应用常量是指定义在设计描述中常量是指定义在设计描述中不变化不变化的值,是一个的值,是一个全局量全局量。格式格式 :CONSTANT CONSTANT 常数名常数名: :数据类型数据类型:=:=表达式表达式Example Example :CONSTANT CONSTANT VCCVCC: :realreal:=:=5.05.0CONSTANTCONSTANT delay delay: :timetime:=:=10ns10nsCONSTANTCONSTANT fbus fbus: :bit_vectorbit_vector:=:=“0101”“0101

33、”指定电源电压指定电源电压某信号的延迟某信号的延迟总线上的数据向量总线上的数据向量用途:用途:在实体、结构体、程序包、函数、过在实体、结构体、程序包、函数、过程、进程中程、进程中保持静态数据保持静态数据,以改善程,以改善程序的序的可读性可读性,使修改程序容易。,使修改程序容易。变量是定义在变量是定义在进程进程或或子程序子程序中的变化量。中的变化量。格式格式 :VARIABLE VARIABLE 变量名变量名: :数据类型数据类型:=:=初始值初始值用途:用途:在在PROCESSPROCESS、FUNCTIONFUNCTION、PROCEDUREPROCEDURE用用于计算或暂存中间数据,是一个

34、于计算或暂存中间数据,是一个局部局部量量。不能在进程外部定义使用。不能在进程外部定义使用注意:注意:变量的变量的赋值是立刻生效赋值是立刻生效的。的。信号对应着硬件内部实实在在的连线,在元件间起着信号对应着硬件内部实实在在的连线,在元件间起着互联互联作用作用,或作为一种,或作为一种数据容器数据容器,以保留,以保留历史值历史值和和当前值当前值。格式格式 :SIGNAL SIGNAL 信号名信号名: :数据类型数据类型:=:=表达式表达式注意:注意:“:=”“:=”表示对信号的赋初值,一般表示对信号的赋初值,一般不不产生延时产生延时。“=”=”表示信号的代入赋值,表示信号的代入赋值,有延时有延时。分

35、为分为外部端口信号外部端口信号和和内部信号内部信号。外部端口信号外部端口信号是设计单元电路中的引脚,在实体是设计单元电路中的引脚,在实体中定义,供整个设计单元使用,属于全局量。中定义,供整个设计单元使用,属于全局量。在结构体中,外部端口信号可以直接使用,不在结构体中,外部端口信号可以直接使用,不需要加以说明。需要加以说明。内部信号内部信号是用来描述设计单元内部的传输信号,是用来描述设计单元内部的传输信号,可在包体、结构体、块语句中定义。可在包体、结构体、块语句中定义。注意注意:信号不能在进程和子程序中定义信号不能在进程和子程序中定义!信号和变量的区别信号和变量的区别信号信号变量变量赋值符赋值符

36、号号=:=功能功能电路的内部连接电路的内部连接内部数据交换内部数据交换作用范作用范围围在结构体、包体、块在结构体、包体、块语句中定义。不能在语句中定义。不能在进程中定义进程中定义在进程、过程和在进程、过程和函数的内部定义函数的内部定义行为行为延迟一定时间后才赋延迟一定时间后才赋值值立即赋值立即赋值 下面的例子是D触发器的VHDL描述,注意比较结构体dff_1、dff_2和dff_3的差别:例例2-6 D2-6 D触发器触发器ENTITY dff_1 ISPORT (clk,d:IN Bit;q:OUT Bit);END dff_1;ARCHITECTURE bhv1 OF dff_1 ISBE

37、GINPROCESS (clk)VARIABLE a: Bit;BEGINIF clkEvent AND clk=1 THENa := d;q = a;END IF;END PROCESS;END bhv1;d qclkENTITY dff_2 ISPORT (clk,d:IN Bit;q:OUT Bit);END dff_2;ARCHITECTURE bhv2 OF dff_2 ISSIGNAL a: Bit;BEGINPROCESS (clk)BEGINIF clkEvent AND clk=1 THENa = d;END IF;END PROCESS;q = a;END bhv2;d a

38、clkqENTITY dff_3 ISPORT (clk,d:IN Bit;q:OUT Bit);END dff_3;ARCHITECTURE bhv3 OF dff_3 ISSIGNAL a: Bit;BEGINPROCESS (clk)BEGINIF clkEvent AND clk=1 THENa = d;q = a;END IF;END PROCESS;END bhv3;d aclka qclk dff_1、dff_2和dff_3在RTL电路上的差别如下: dff_1 dff_2 dff_3 在dff_1中,变量a在硬件上没有对应实物存在;但在dff_2和dff_3中,信号a在硬件上是

39、物理存在的。在dff_3中,因为信号a和q的值都被clk上升沿激活而改变,所以就变成两个D触发器的级联了,与dff_2相比,信号d在输出端q的反应要晚1个clk周期。d qclkd aclka qclkd aclkq2.6 VHDL的数据类型和子类型在对象声明格式中,有1项是对象的数据类型。VHDL含有很宽范围的数据类型,用它们可以建立从简单到复杂的各种数据类型的对象,使得VHDL能够在更高的抽象层次上描述对象和创建算法模型。在讨论这些数据类型之前,我们先讨论与数据类型有关的文字与数据类型有关的文字。2.6.1 文字 文字是一种具有“值”的符号,它既不同于标识符,也不同于运算符。VHDL有6类

40、文字:整数、实数(也称浮点数)、字符、字符串、位串和物理量。 整数与实数的差别在于整数中不含小数点,而实数中含有小数点。它们可以用2进制、4进制、8进制、10进制和16进制等任意进制来表示,而且可以在任意2个相邻的数字之间插入下划线,这大大增强了可读性,但并不影响数值的大小。 下面是整数和实数文字的例子:- 整数文字01234567810E5 - 表示10X1052E8 - 表示2X1082#11111111# - 等于2进制整数11111111B2#1111_1111# - 与上面1个文字等价8#777# - 等于8进制整数777O16#FF# -等于16进制整数FFH- 实数文字0.012

41、3456.999999123_456.999_999 - 与上面一行文字等价1.234E+2 - 等于10进制实数123.416#F.FFF# - 等于16进制整数F.FFFH 字符文字字符文字是用单引号括起来的单个是用单引号括起来的单个ASCIIASCII字符,例字符,例如如AA、/等。等。 字符串文字字符串文字则是用双引号括起来的一串则是用双引号括起来的一串ASCIIASCII字符,字符,例如例如abc、”1234”等。等。 位串字符位串字符是以进制声明符是以进制声明符B B或或O O或或X X为前导的、用双引为前导的、用双引号括起来的数字序列,但这些数字只限于号括起来的数字序列,但这些数

42、字只限于0-90-9和和a-fa-f(A-FA-F与之等价)。为了增强可与之等价)。为了增强可读性,可以在相邻的数字之间插入下划线。读性,可以在相邻的数字之间插入下划线。 下面是位串文字的例子:下面是位串文字的例子: B”1010_1010” - - 位串长度为位串长度为8 8 O”377” - - 位串长度为位串长度为9 9,等价于,等价于B”011_111_111” X”5F5” - - 位串长度为位串长度为12,12,等价于等价于B”0101_1111_0101” 物理文字物理文字是由整数或者实数文字与表示物理单位的是由整数或者实数文字与表示物理单位的标识符组成,例如:标识符组成,例如:

43、3.5 ns、20 pf、15 kohm等等。等等。整数类型实数类型枚举类型物理类型数组记录标量类型复合类型存取类型文件类型数据类型2.6.2 数 据 类 型标量类型的声明格式为: TYPE 类型名称 IS 值域;声明数组类型的一般格式为:TYPE 数组名称 IS ARRAY 下标范围 OF 元素类型;声明记录类型的一般格式为: TYPE 记录名称 IS RECORD 元素名称:元素类型; END RECORD;n标准定义的数据类型标准定义的数据类型(由由standard程序包定程序包定义义,在使用中不需再用在使用中不需再用USE语句以显示调用语句以显示调用)布尔量、字符、字符串、整数、实数、

44、位、布尔量、字符、字符串、整数、实数、位、时间、位向量、自然数、正整数时间、位向量、自然数、正整数nIEEE预定义标准逻辑位与向量预定义标准逻辑位与向量std_logic、std_logic_vectorn用户自定义的数据类型用户自定义的数据类型 枚举类型、物理类型、数组类型、记录类枚举类型、物理类型、数组类型、记录类型型整数类型整数类型n保留字:保留字:Integern范围为范围为-214783647到到214783647(231-1)n需要综合时,要对范围加以限制需要综合时,要对范围加以限制 TYPE code_in IS RANGE 15 DOWNTO 0;建议在描述整数类型或者整数类型

45、的数组下标时,采用由高位至低位的排列顺序:“xHigh DOWNTO xLow”。SINGAL a:STD_LOGIC_VECTOR(3 DOWNTO 0); 若若a=“1010”,则,则 a(3)=1;a(2)=0;a(1)=1;a(0)=0SINGAL b:STD_LOGIC_VECTOR(0 TO 3); 若若b=“1101” ,则,则 b(3)=1;b(2)=0;b(1)=1;b(0)=1实数类型实数类型n保留字:保留字:Realn范围为:范围为:-1.0E38到到1.0E38n很多综合器不支持该类型,仅在很多综合器不支持该类型,仅在VHDL 仿真器中使用仿真器中使用nTYPE ana

46、log IS RANGE 0.0 TO 5.0;布尔量n保留字:Booleann取值为FALSE和TRUE字 符n保留字:Charactern编程时用单引号括起来,如An字符文字区分大小写,Z与z是不相同的字符串n保留字:Stringn字符串在编程时用双引号括起,如“1111001101”位n保留字:Bitn取值只能是0和1位矢量n保留字:Bit_vectorn位矢量是基于Bit数据类型的数组,使用位向量必须注明宽度,即数组中的元件个数和排列n如: SIGNAL a: Bit_vector (7 DOWNTO 0);时 间n保留字:Timen时间类型值的范围-(231-1)到(231-1)n时

47、间类型的完整表达方法应包含整数和单位两部分n一般用于仿真,对于逻辑综合来说意义不大自然数和正整数n保留字:自然数(Natural) 、正整数(Positive)n自然数是整数的一个子类型,包括零和正整数n正整数也是整数的一个子类型,包括整数中非零和非负的数值Std_logic、Std_logic_vectorn工业标准的逻辑类型,取值0(强0)、1(强1)、Z(高阻态) 、-(无关) 、X(强未知的)、W(弱未知的)、L(弱0)、H(弱1) 、U(未初始化的),只有前四种取值具有实际物理意义,其他的为了与模拟环境相容才保留的。Std_logic、Std_logic_vectornStd_log

48、ic_vector 是std_logic的组合n使用时,在程序中必须声明库及程序包说明语句:LIBRARY ieee; USE ieee.std_logic_1164.ALL;Std_logic、Std_logic_vector 在下面的例子中,4位二进制计数器的输出端口q的数据类型被定义为Std_Logic类型。因为在赋值语句中有表达式q+1,所以q的信号模式不能为OUT,而是BUFFER,即带有内部反馈的输出端口。例例2-7 4位二进制加法计数器位二进制加法计数器LIBRARY IEEE;USE IEEE.Std_logic_1164.ALL;USE IEEE.Std_logic_Unsi

49、gned.ALL;ENTITY cnt4 IS PORT (clk:IN Bit; q:BUFFER Std_logic_Vector(3 DOWNTO 0) ;END cnt4;ARCHITECTURE bhv OF cnt4 ISBEGIN PROCESS (clk) BEGIN IF clkEvent AND clk=1 THEN - 上升沿 q = q+1; END IF; END PROCESS;END bhv; 在例2-7中,因为输出端口q具有内部反馈,因此信号模式为BUFFER。但BUFFER类型的输出端口的驱动能力往往不够强,因为一个端口的扇出系数是一定的,如果被内部反馈占用一

50、部分之后,其驱动能力必然下降。 在这种情况下,通常用增加一个驱动器的方法来解决:例2-7 4位二进制加法计数器的另一种描述LIBRARY IEEE;USE IEEE.Std_logic_1164.ALL;USE IEEE.Std_logic_Unsigned.ALL;ENTITY cnt4 IS PORT (clk:IN Std_logic; q:OUT Std_logic_Vector(3 DOWNTO 0);END cnt4;ARCHITECTURE bhv OF cnt4 IS SIGNAL q1:Std_logic_Vector(3 DOWNTO 0) ;BEGIN PROCESS (

51、clk) BEGIN IF clkEvent AND clk=1 THEN q1 = q1+1; END IF; END PROCESS; q = q1;END bhv;枚举类型枚举类型n定义语法定义语法: TYPE 数据类型名数据类型名 IS (枚举文字,枚举文字,枚举文字,枚举文字,)n如如 TYPE States IS (S1,S2,S3,S4); TYPE color IS ( red,green,yellow,blue);n枚举类型的定义及相应的变量和信号声明举例枚举类型的定义及相应的变量和信号声明举例 TYPE color IS (red,green,yellow,blue); T

52、YPE level IS(0,1,Z); VARIABLE a:color; SIGNAL v:level; a:=red; v=1;物理类型物理类型n物理类型的定义需规定一个取值范围、一个基本单位和若干个(0至多个)次级单位,次级单位需是基本单位的整数倍TYPE voltage IS RANGE 0 TO 10E15 - 物理类型物理类型 UNITS nv; - 基本单位 uv = 1000nv; - 次级单位,是基本单位的整数倍 mv = 1000 uv; v = 1000 mv; kv = 1000 v; END UNITS; 复合类型(数组类型和记录类型)复合类型(数组类型和记录类型)

53、 复合类型包括数组和记录复合类型包括数组和记录。数组是同构复合类。数组是同构复合类型,它所定义的是同一类型值的集合;记录是异构型,它所定义的是同一类型值的集合;记录是异构复合类型,它所定义的可以是不同类型值的集合。复合类型,它所定义的可以是不同类型值的集合。 数组可以是一维或者多维的数组可以是一维或者多维的,每一维下标的类,每一维下标的类型必须是离散类型(每一维下标的类型与数组元素型必须是离散类型(每一维下标的类型与数组元素的类型其意义是不同的)。如果指定每一维下标的的类型其意义是不同的)。如果指定每一维下标的范围和方向(即指定了数组的上下界),则为范围和方向(即指定了数组的上下界),则为限定

54、限定性数组性数组,否则为,否则为非限定性数组非限定性数组。 VHDL仿真器支持多维数组,但仿真器支持多维数组,但VHDL综合器综合器只支持一维数组。只支持一维数组。数组类型数组类型n定义语法 TYPE 数组名称 IS ARRAY 下标范围 OF 元素类型;n如: TYPE a IS ARRAY(integer 9 DOWNTO 0) OF std_logic; 数组类型数组类型TYPE Byte IS ARRAY (7 DOWNTO 0) OF Bit; - 限定性数组TYPE Address IS RANGE 65535 DOWNTO 0; -整数类型TYPE Element IS ARRA

55、Y(Address)OF Byte; - 限定性数组TYPE Colors IS ( Black,Blue,Green,Cyan,Red,Magenta,Brown,LightGray,DarkGray,LightBlue,LightGreen,LightCyan,LightRed,Light Magenta ,Yellow,White );TYPE Row IS RANGE 479 DOWNTO 0;TYPE Column IS RANGE 639 DOWNTO 0;TYPE Pixel IS ARRAY(Row,Column)OF Colors;- 其中Pixel 是Colors的类型,R

56、ow和Column分别是第一和第二维下标的类型-数组类型数组类型数组类型数组类型TYPE Bit_Vector IS ARRAY(Natural RANGE )OF Bit; - 非限定性数组,其中Bit_Vector的类型是Bit,下标的类型是自然数Natural,记录记录可以定义相同或者不同类型的元素,每个元素有不同的名称。声明记录类型的一般格式为: TYPE 记录名称 IS RECORD 元素名称:元素类型; END RECORD; 当记录类型中的每一个元素都为标量类型时,称当记录类型中的每一个元素都为标量类型时,称之为线性记录类型;否则为非线性记录类型。只有线之为线性记录类型;否则为非

57、线性记录类型。只有线性记录类型的对象才是可综合的。性记录类型的对象才是可综合的。记录类型记录类型 记录记录可以定义相同或者不同类型的元素,每个元素有不同的名称。声明记录类型的一般格式为: TYPE 记录名称 IS RECORD 元素名称:元素类型; END RECORD; 当记录类型中的每一个元素都为标量类型时,称之为线性记录类型;否则为非线性记录类型。只有线性记录类型的对象才是可综合的。 下面是记录类型定义的例子:TYPE Memory IS RECORD Address:Integer RANGE 16#FFFFF# DOWNTO 16#00000#; Data:Byte;END RECO

58、RD;TYPE Char IS RECORD Ascii:Character; Color:Colors; Row:Integer RANGE 23 DOWNTO 0; Col:Integer RANGE 79 DOWNTO 0;END RECORD;2.6.4 子类型 当某一对象的值域是某个类型声明所定义的值域的子集时,为了增加可重用性,而不定义太多的不定义太多的新类型新类型,VHDL提出了子类型的概念。 子类型只是对其基本类型(也称父类型)的值域加以限制,而并不是一种新的类型,因此 ,子类子类型和其父类型完全兼容,同一父类型的各子类型也型和其父类型完全兼容,同一父类型的各子类型也相互兼容相

59、互兼容。子类型的对象,可以将其值直接赋给父类型的对象;而父类型的对象,只要其值未超出子类型声明的范围,也可以将其值直接赋给子类型的对象。这一特性,可以类推到同一父类型的各子类型之间。 子类型声明的一般格式为:SUBTYPE 子类型名称 IS 基本类型值域的子集; 下面是两个子类型声明的例子:TYPE Integer IS RANGE 2147483647 TO +2147483647;SUBTYPE Natural IS Integer RANGE 0 TO IntegerHigh;SUBTYPE Positive IS Integer RANGE 1 TO IntegerHigh; 我们定义

60、下面的2个整数类型和2个信号:TYPE Int_1 IS RANGE 63 DOWNTO 0;TYPE Int_2 IS RANGE 15 DOWNTO 0;SIGNAL a:Int_1;SIGNAL b:Int_2;则如下的信号赋值是非法的: a = b;但如果将如果将Int_2定义为定义为Int_1的子类型的子类型:SUBTYPE Int_2 IS Int_1 RANGE 15 DOWNTO 0;则如下的信号赋值就是合法的: a 0, 1|H = 1, OTHERS = 0);BEGIN b = typeconv_con(s);END;2.7 属性VHDL中,下列项目可以具有属性:类型,子

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 园区供餐合同范本

- 音乐培训机构家长会

- 2023年湖南单招职业技能测试题库及答案(40题)

- 西游记每回知识点

- 指挥中心应急指挥调度解决方案

- 淄博师范高等专科学校《建筑工程信息建模课程设计》2023-2024学年第二学期期末试卷

- 安徽粮食工程职业学院《混凝土结构设计原理(含荷载与可靠度)》2023-2024学年第一学期期末试卷

- 2025年广东省河源市龙川县隆师中学高三5月月考(历史试题理)试卷含解析

- 安徽省安庆第二中学2024-2025学年高三下学期二调考试历史试题含解析

- 上海科学技术职业学院《就业与创业-校友的理论与实践》2023-2024学年第一学期期末试卷

- 单片机原理及应用期末考试题试卷大全(含答案)

- 镇村信访矛盾纠纷实施方案及计划信访矛盾大排查大化解实施方案

- 2024年燃气报警器市场分析:燃气报警器年均增长率保持在约6.5%

- DB34T 577-2021 葡萄炭疽病测报调查规范

- DB34T 4824-2024 地质标本登记著录规范

- 人教精通版四年级英语下册第二单元测试卷(含答案)

- 《电位的计算》教案

- (正式版)JTT 1497-2024 公路桥梁塔柱施工平台及通道安全技术要求

- 幕墙施工技术交底

- 《民宿文化与运营》课件-第八章 民宿经营与推广

- 能谱成像技术在放射治疗中的应用

评论

0/150

提交评论