版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、实验六程控交换时分交换实验一、实验目的1、掌握程控交换中时分交换基本原理与实现方法。2、通过对MT8980芯片的实验,熟悉时分交换网络的工作过程。3、通过自己动手连接实验线,增强对电话通信自动交换的感性认识,体会程控交换技术的优越性。二、预习要求认真预习程控交换原理教材中的相关内容。三、实验仪器仪表1、程控交换系统实验箱一台2、电话单机二台3、20MHz示波器一台4、万用表一台5、逻辑分析仪一台(选用四、实验电路工作过程电信系统中的程控交换机的时分交换网络是利用控制存储器存取的原理进行PCM各话路时隙间数字信息的交换,因此又将其称为数字交换网络或时隙交换器(TSI,time slot inte

2、rchanger。时分连接网络主要由话音存储器与控制存储器两部分组成。它首先将输入的PCM复用码流以时隙(8bit为单位按顺序写入话音存储器,然后根据呼叫的要求,将来自微处理器的接续命令存入控制存储器,这样,控制存储器按要求的顺序从话音存储器中读出有关时隙信息,并构成输出复用码流。这种方式一般称为“顺序写入、控制输出”或者“顺序写入、随机读出”,简称为“输出控制”方式。当然,若改为“控制写入、顺序读出”或“输入控制”方式,也可以实现同样的时隙交换功能。由于输入、输出复用码流与各实际用户有固定的时隙关系,因而通过上述的时隙信息转移的过程,可以完成呼叫用户间话音信息的交换。目前除小容量程控数字交换

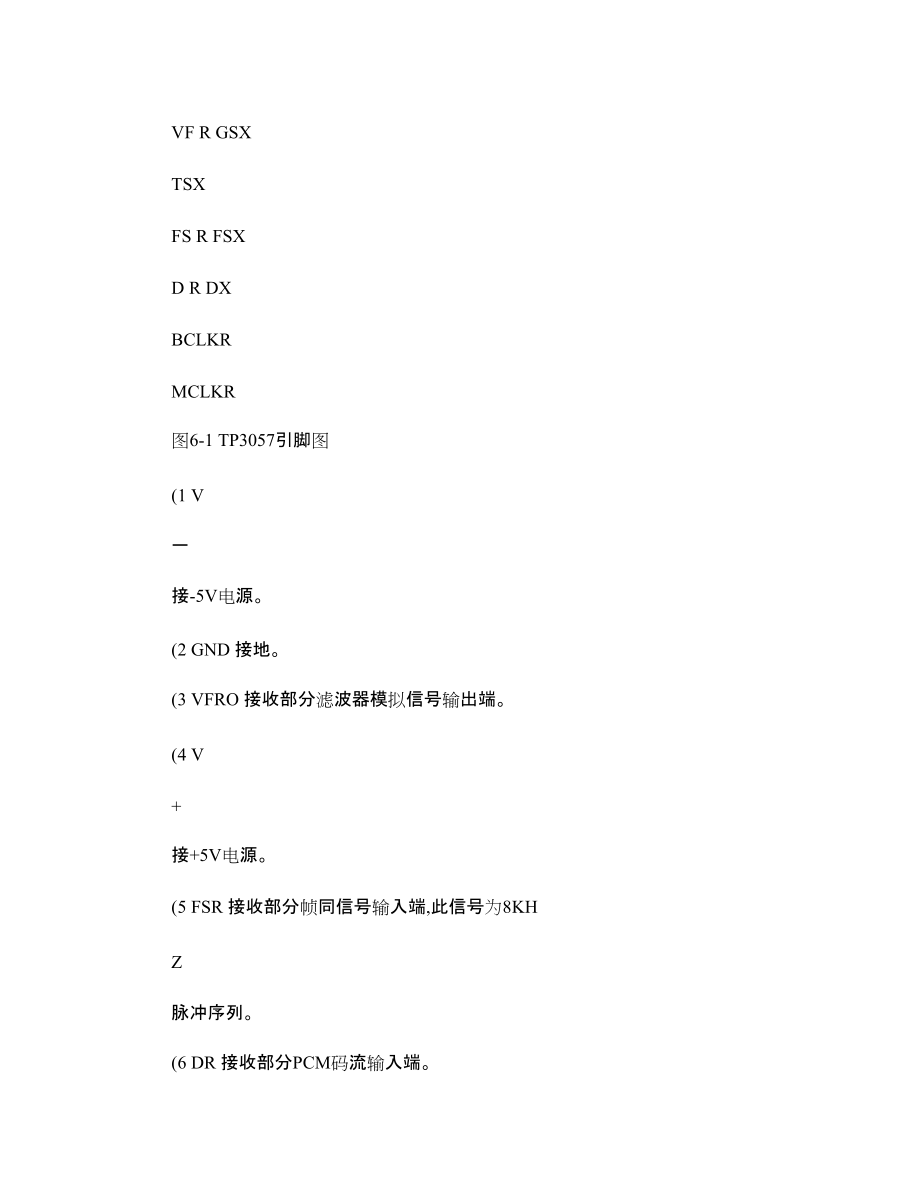

3、机可能采用一般的RAM构成数字交换网络外,中大容量的程控数字交换机一般都已利用专用数字交换集成电路或模块,以扩大容量、提高效率、增强可靠性与降低成本。例如,Mitel公司的MT8980D与SGS THOMSON公司的M3488数字交换集成电路,可以实现8条输入PCM基群码流与8条输出PCM基群码流(各256个时隙间任两路信息的无阻塞交换。在本实验系统中用户话机的信号音(拨号音、回铃音、忙音、空号音、拥塞音是通过空分交换网络送达的,与前面实验的相同,在此不再介绍。PCM编译码器才用的是TP3057。它是CMOS工艺制造的专用大规模集成电路,片内带有输出输入话路滤波器,其引脚及内部框图如图6-1、

4、图6-2所示。引脚功能如下:33 VF X i+VF X i_VF R GSXTSXFS R FSXD R DXBCLKRMCLKR图6-1 TP3057引脚图(1 V一接-5V电源。(2 GND 接地。(3 VFRO 接收部分滤波器模拟信号输出端。(4 V+接+5V电源。(5 FSR 接收部分帧同信号输入端,此信号为8KHZ脉冲序列。(6 DR 接收部分PCM码流输入端。(7 BCLK/CLKSEL 接收部分位时钟(同步信号输入端,此信号将PCM码流在FSR上升沿后逐位移入DR端。位时钟可以为64KHZ到2.048MHZ的任意频率,或者输入逻辑“1”用作同步模式的主时钟,此时发时钟信号BCL

5、KX同时作为发时钟和收时钟。(8 MCLKR/PDN 接收部分主时钟信号输入端,此信号频率必须为1.536MHZ、1.544MHZ或2.048MHZ。可以和MCLKX异步,但是同步工作时可达到最佳状态。当此端接低电平时,所有的内部定时信号都选择MCLKX信号,当此端接高电平时,器件处于省电状态。(9 MCLKX发送部分主时钟信号输入端,此信号频率必须为1.536MHZ、1.544MHZ或2.048MHZ。可以和MCLKR异步,但是同步工作时可达到最佳状态。(10 BCLKX 发送部分位时钟输入端,此信号将PCM码流在FSX信号上升沿后逐位移出DX端,频率可以为64KHZ到2.04MHZ的任意频

6、率,但必须与MCLKX同步。(11 DX发送部分PCM码流三态门输出端。(12 FSX发送部分帧同步信号输入端,此信号为8KHZ脉冲序列。(13 TSX漏极开路输出端,在编码时隙输出低电平。(14 GSX发送部分增益调整信号输入端。15 VFX i-发送部分放大器反向输入端。34(16 VFX i+发送部分放大器正向输入端。 VF RR/PDNR/CLKSEL 图6-2 TP3057内部方框图TP3057由发送和接收两部分组成,其功能简述如下。发送部分:包括可调增益放大器、抗混淆滤波器、低通滤波器、高通滤波器、压缩A/D 转换器。抗混淆滤波器对采样频率提供30dB以上的衰减从而避免了任何片外滤

7、波器的加入。低通滤波器是5阶的、时钟频率为128MHZ。高通滤波器是3阶的、时钟频率为32KHZ。高通滤波器的输出信号送给阶梯波产生器(采样频率为8KHZ。阶梯波产生器、逐次逼近寄存器(S·A·R、比较器以及符号比特提取单元等4个部分共同组成一个压缩式A/D转换器。S·A·R输出的并行码经并/串转换后成PCM信号。参考信号源提供各种精确的基准电压,允许编码输入电压最大幅度为5VP-P。发帧同步信号FSX为采样信号。每个采样脉冲都使编码器进行两项工作:在8比特位同步信号BCLKX的作用下,将采样值进行8位编码并存入逐次逼近寄存器;将前一采样值的编码结果通过

8、输出端DX输出。在8比特位同步信号以后,DX端处于高阻状态。接收部分:包括扩张D/A转换器和低通滤波器。低通滤波器符合AT&T D3/D4标准和CCITT建议。D/A转换器由串/并变换、D/A寄存器组成、D/A阶梯波形成等部分3536构成。在收帧同步脉冲FSR 上升沿及其之后的8个位同步脉冲BCLKR 作用下,8比特PCM 数据进入接收数据寄存器(即D/A 寄存器,D/A 阶梯波单元对8比特PCM 数据进行D/A 变换并保持变换后的信号形成阶梯波信号。此信号被送到时钟频率为128KHZ 的开关电容低通滤波器,此低通滤波器对阶梯波进行平滑滤波并对孔径失真(sin x/x 进行补尝。在通信

9、工程中,主要用动态范围和频率特性来说明PCM 编译码器的性能。 动态范围的定义是译码器输出信噪比大于25dB 时允许编码器输入信号幅度的变化范围。PCM 编译码器的动态范围应大于图6-3所示的CCITT 建议框架(样板值。当编码器输入信号幅度超过其动态范围时,出现过载噪声,故编码输入信号幅度过大时量化信噪比急剧下降。TP3057编译码系统不过载输入信号的最大幅度为5V P-P 。由于采用对数压扩技术,PCM 编译码系统可以改善小信号的量化信噪比,TP3057采用A 律13折线对信号进行压扩。当信号处于某一段落时,量化噪声不变(因在此段落内对信号进行均匀量化,因此在同一段落内量化信噪比随信号幅度

10、减小而下降。13折线压扩特性曲线将正负信号各分为8段,第1段信号最小,第8段信号最大。当信号处于第一、二段时,量化噪声不随信号幅度变化,因此当信号太小时,量化信噪比会小于25dB ,这就是动态范围的下限。TP3057编译码系统动态范围内的输入信号最小幅度约为0.025V p-p 。-10 0 -20 -30 -40 -50 图6-3 PCM 编译码系统动态范围样板值常用1KHZ 的正弦信号作为输入信号来测量PCM 编译码器的动态范围。语音信号的抽样信号频率为8KH Z ,为了不发生频谱混叠,常将语音信号经截止频率为3.4KH Z 的低通滤波器处理后再进行A/D 处理。语音信号的最低频率一般为3

11、00H Z 。TP3057编码器的低通滤波器和高通滤波器决定了编译码系统的频率特性,当输入信号频率超过这两个滤波器的频率范围时,译码输出信号幅度迅速下降。这就是PCM 编译码系统频率特性的含义。图6-4为其原理框图,图6-5为本实验系统中的电路原理图 图6-4 PCM编译码原理方框图 其中U1和和晶振构成分频器为四个PCM编译码器提供2.048MHZ的时钟信号和8KHZ的时隙同步信号。在实际通信系统中,译码器的时钟信号(即位同步信号及时隙同步信号(即帧同步信号应从接收到的数据流中提取。此处将同步器产生的时钟信号及时隙同步信号直接送给译码器。由于时钟频率为2.048MHZ,抽样信号频率为8KHZ

12、,故PCM的输出DX(SFAX2的码速率是2.048MB,一帧中有32个时隙,其中1个时隙为PCM编码数据,另外31个时隙都是空时隙。PCM信号码速率也是2.048MB,一帧中的32个时隙中有29个是空时隙,第0时隙为帧同步码(×1110010时隙,第2时隙为信号的时隙。实验系统中的时分交换网络采用的是Mitel公司的MT8980D,图6-6是其内部功能框图。它可以在控制信号的作用下,实现8条PCM基群(30/32路各37时隙话音或数据的无阻塞数字交换。次电路的供电电压为+5V,采用 CMOS 工 艺。电路由串并转换器、数据存储器、帧计数器、控制寄存器、控制接口单元、 接续存储器、输

13、出复用器与并串转换器等部分构成。串行 PCM 数据流以 2.048Mbit/s 速率(共 32 个 64kbit/s、8bit 数字时隙分 8 路由 Sti0Sti7 输入,经 串并转换,根据码流信号和信道(时隙)号依次存入 256*8bit 数据存储器的相应 单元内。控制存储器通过控制接口,接收来自微处理器的指令,并将此指令写到 接续存储器。这样,数据存储器中各信道的数据按照接续存储器的内容(即接续 指令) ,以某种顺序从中读出,再经复用、缓存、并串转换,变为时隙交换后的 8 路 2.048Mbit/s 串行码流,从而达到数字交换的目的。如果不再对控制存储器 发出命令, 则电路内部维持现有的

14、状态,刚才交换过的两时隙将一直处于交换过 程,直到接收新命令为止。 图 6-6 MT8980D 的内部功能框图 接续存储器的容量为 256*11bit,分为高 3bit 和低 8 bit 两部分,前者决定 本输出时隙的状态,后者决定本输出时隙所对应的输入时隙。另外,由于输出多 路开关的作用,电路还可以工作于消息或报文模式,以使接续存储器低 8 bit 的 内容作为数据直接输出到相应的时隙中去。 电路内部的全部动作均由控制系统通 过控制接口控制,可以读取数据存储器、控制存储器和接续存储器的内容,并可 以向控制寄存器和接续存储器写入指令。此外,还可置电路于分离方式,即微处 理器的所有读操作均读自于

15、数据存储器,所有写操作均写至接续存储器的低 8 位。微处理器对该交换电路的控制主要体现在输入控制接口信号(如地址线 A5 A0、数据线 D7D0、片选信号 CS 、读/写信号 R/ W 、数据输入选通信号 DS 等)对控制寄存器、数据存储器和接续存储器状态的设置,以确定工作方式、 码流地址和信道寻址等。 图 6-7 是 MT8980 的两种封装形式,本实验系统所采用的是 44 脚的 PLCC 封装。表 6-1 对其管脚功能作了简单的说明。MT8980D 的控制时序图如图 6-8 所示。电路原理图如图 6-9 所示。 38 图 6-7 MT8980D 管脚排列图 表 6-1 MT8980D 引脚

16、介绍 引出端号 符号 PLCC 控制 ST 总线输入 CSTO 1 DTA 说明 2 3-5 7-11 12 13 14 15-17 19-21 22 23 24 25-27 29-33 34 35-39 41-43 44 6、18、28、40 数据确认,接到微处理器接口 ST 总线输入 ST 总线输入 +5V 电压 帧同步信号输入,接 8K 信号 4.096M 信号输入 地址线 地址线 数据输入选通信号 读写信号 片选信号 三态数据线 三态数据线 接地 ST 总线输出 ST 总线输出 输出使能端,接高电平 空脚,不连接 STI0STI2 STI3STI7 VDD F0I C4I A0A2 A3A5 DS R/ W CS D7D5 D4D0 VSS STO7STO3 STO2STO0 ODE 39 图 6-8 MT8980D 的控制时序图 图 6-9 时分模块电路

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025煤炭购销合同2

- 井队员工合同样本

- 铁路护栏搬运方案范本

- 修补水沟合同样本

- 农村改造项目合同样本

- 公路牌安装合同样本

- 万科咨询合同样本

- 出售自用冷库合同样本

- 冲压配件订购合同样本

- 代理办证机构合同样本

- 2024年新人教版六年级数学上册《教材练习2练习二 附答案》教学课件

- 【核心素养目标】六年级科学下册(苏教版)4.13 洁净的水域(教案)

- 设备吊装作业施工方案

- 小学语文“的、地、得”专项练习(附答案)

- 2024至2030年中国去中心化标识符(DID)市场现状研究分析与发展前景预测报告

- 《建筑施工测量标准》JGJT408-2017

- 2024-2030年中国社区医院行业市场发展分析及前景趋势与投资研究报告

- 2024年四川省成都市郫都区五年级数学第二学期期末学业质量监测模拟试题含解析

- 黑龙江省齐齐哈尔市2024年中考数学试卷【附真题答案】

- 脱硫技术方案钠碱法脱硫

- 2024年广东省中考生物试卷附答案

评论

0/150

提交评论