版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、第四章第四章 时序逻辑电路时序逻辑电路时序逻辑电路时序逻辑电路本章内容概述锁存器的设计触发器的设计寄存器的设计计数器的设计乘法器的设计时序逻辑电路时序逻辑电路时序逻辑电路时序逻辑电路时序逻辑电路是一种输出不仅与时序逻辑电路是一种输出不仅与当前的输入有关,而且与其输出当前的输入有关,而且与其输出状态的原始状态有关的电路。相状态的原始状态有关的电路。相当于在组合逻辑的输入端加上了当于在组合逻辑的输入端加上了一个反馈输入,在其电路中有一一个反馈输入,在其电路中有一个存储电路,可以将输出的状态个存储电路,可以将输出的状态保持住。保持住。数字电路按其完成逻辑功能的不同特点,划分为数字电路按其完成逻辑功能

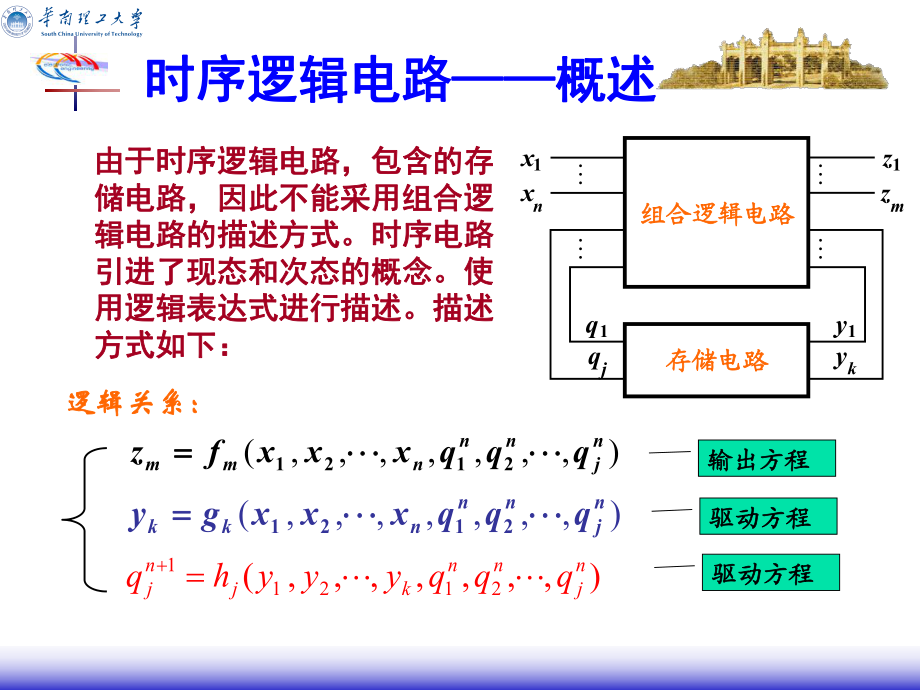

2、的不同特点,划分为组合组合逻辑电路逻辑电路和和时序逻辑电路时序逻辑电路两大类。两大类。存储电路存储电路组合逻辑电路组合逻辑电路x1xnz1zmq1qjy1yk结构框图结构框图时序逻辑电路时序逻辑电路概述概述时序逻辑电路时序逻辑电路有记忆功能有记忆功能从逻辑上讲,时序电路在任一时刻的输出不仅取决于该时刻的输入,而且还和电路原来的状态有关从结构上讲,时序电路不仅仅由逻辑门组成,还包含有存储信息的有记忆能力的电路:触发器、寄存器等时序逻辑电路时序逻辑电路概述概述由于时序逻辑电路,包含的存由于时序逻辑电路,包含的存储电路,因此不能采用组合逻储电路,因此不能采用组合逻辑电路的描述方式。时序电路辑电路的描

3、述方式。时序电路引进了现态和次态的概念。使引进了现态和次态的概念。使用逻辑表达式进行描述。描述用逻辑表达式进行描述。描述方式如下:方式如下:存储电路存储电路组合逻辑电路组合逻辑电路x1xnz1zmq1qjy1yk逻辑关系:逻辑关系:),(njnnnmmqqqxxxfz 2121),(njnnnkkqqqxxxgy 2121),(21211njnnkjnjqqqyyyhq 输出方程输出方程驱动方程驱动方程驱动方程驱动方程时序逻辑电路时序逻辑电路概述概述 没有统一的时钟脉冲信号,各触发器状态的变化不是同没有统一的时钟脉冲信号,各触发器状态的变化不是同时发生,而是有先有后。时发生,而是有先有后。按照

4、按照触发触发器的器的动作动作特点特点同步时序逻辑电路同步时序逻辑电路异步时序逻辑电路异步时序逻辑电路 所有触发器的状态变化都是在同一时钟信号作用下同时所有触发器的状态变化都是在同一时钟信号作用下同时发生的。发生的。 输出状态仅与存储电路的状态输出状态仅与存储电路的状态QQ有关,而与输入有关,而与输入X X无直无直接关系。或者没有单独的输出。接关系。或者没有单独的输出。按照按照输出输出信号信号的特的特点点米里(米里(MealyMealy)型)型摩尔(摩尔(MooreMoore)型)型 输出状态不仅与存储电路的状态输出状态不仅与存储电路的状态QQ有关,而且与外部输有关,而且与外部输入入X X也有关

5、。也有关。时序逻辑电路时序逻辑电路概述概述同步时序逻辑电路同步时序逻辑电路所有的存储元件都在时钟脉冲所有的存储元件都在时钟脉冲CPCP统一控制下,用触统一控制下,用触发器作为存储元件。只有一个发器作为存储元件。只有一个“时钟信号时钟信号”,所有,所有的内部存储器,只会在时钟的边沿时候改变。的内部存储器,只会在时钟的边沿时候改变。1JC11K1JC11K1JC11K&FF1FF0FF2ZCPQ2Q1Q0所有的所有的CPCP是接在一起是接在一起的,所以同时动作的,所以同时动作时序逻辑电路时序逻辑电路概述概述几乎现在所有的时序逻辑都是“同步逻辑”优点:简单。每个电路里的运算必须要在时钟的两个

6、脉冲之间固定的间隔内完成,称为一个时钟周期。满足该条件下的电路是可靠的。同步时序逻辑电路同步时序逻辑电路缺点: 功耗大,时钟是高频率信号,而时钟必须分布到各个触发器而不管触发器是否要工作 频率低,最大的时钟频率是由电路中最慢的逻辑路径(关键路径)决定的,因此限制了工作的最高频率(Pipelining流水线)时序逻辑电路时序逻辑电路概述概述异步时序逻辑电路异步时序逻辑电路异步时序逻辑是设计上困难度最高的。最基本的储存元件是锁存器。锁存器可以在任何时间改变它的状态,依照其它的锁存器信号的变动,它们新的状态就会被产生出来。异步电路的复杂度随着逻辑门的增加,而复杂性也快速的增加,因此他们大部分仅仅使用

7、在小的应用。CP1JC11K1JC11K1JC11K&FF1FF0FF2ZQ2Q1Q0时序脉冲只接入了第一时序脉冲只接入了第一块触发器,异步动作块触发器,异步动作时序逻辑电路时序逻辑电路概述概述锁存器的设计锁存器的设计时序逻辑电路时序逻辑电路锁存器锁存器锁存器为了与触发器相类比,我们先介绍锁存器。锁存器是一种电平敏感的寄存器,典型的例子有RS锁存器与D锁存器。RS锁存器:锁存器: 真值表:真值表: 电路结构图:电路结构图:时序逻辑电路时序逻辑电路锁存器锁存器Library ieee;Use ieee.std_logic_1164.all;Entity SR_latch2 is port

8、 ( S, R: in std_logic ; Q, Qbar :out std_logic);End SR_latch2;Architecture behav of R_latch2 isBegin process ( R , S ) variable rs: std_logic_vector(1 downto 0);begin rs:=R&S; case rs is when 00 = Q=1; Qbar Q=1; Qbar Q=0; Qbarnull; end case; end process;end behav;注意:注意:顺序结构中的顺序结构中的Null状态等同于并行结状态

9、等同于并行结构中的构中的Unaffected。时序逻辑电路时序逻辑电路锁存器锁存器由图可见,由于在时序仿真中有器件的延时,锁存器由图可见,由于在时序仿真中有器件的延时,锁存器的状态变化迟于输入信号的变化的状态变化迟于输入信号的变化RS锁存器的仿真波形如下:锁存器的仿真波形如下:时序逻辑电路时序逻辑电路锁存器锁存器D锁存器锁存器D锁存器与锁存器与RS锁存器类似,只是在功能上实现的目的不同。锁存器类似,只是在功能上实现的目的不同。VHDLVHDL描述描述: :Library ieee;Use ieee.std_logic_1164.all;Entity D_latch is port ( D, E

10、nable: in std_logic ; Q: out std_logic );End D_latch;Architecture behav of D_latch isBegin process(D, Enable) begin if (Enable=1) then Q=D; end if; end process;End behav;点评:点评:l D锁存器通过条件涵盖不完整的锁存器通过条件涵盖不完整的if语句语句 产生寄存器;产生寄存器;l 敏感参数表包含敏感参数表包含D、Enable,综,综合后合后 形成一个电平触发的锁存形成一个电平触发的锁存器器时序逻辑电路时序逻辑电路锁存器锁存器D

11、锁存器的仿真波形如下:锁存器的仿真波形如下:当当ENABLE=1时,时,Q输出为输出为D的输入值,否则的输入值,否则Q保持不变。保持不变。时序逻辑电路时序逻辑电路锁存器锁存器触发器触发器触发器是指边沿触发的寄存器,常见的有触发器是指边沿触发的寄存器,常见的有D型,型,JK型,型,T型。型。在描述触发器前要注意时钟上升沿的描述在描述触发器前要注意时钟上升沿的描述 D触发器是最常用的触发器,几乎所有的逻辑电路都可以描触发器是最常用的触发器,几乎所有的逻辑电路都可以描述成述成D触发器与组合逻辑电路触发器与组合逻辑电路 D触发器:触发器:时序逻辑电路时序逻辑电路触发器触发器触发器的触发器的VHDL描述

12、(上升沿)描述(上升沿)Library ieee;Use ieee.std_logic_1164.all;Entity D_FF1 is port ( D, clk: in std_logic; Q: out std_logic);End D_FF1; Architecture behav of D_FF1 isBegin -方法一方法一process(clk) begin if ( clks event and clk=1) then Q=D; end if; end process;End behav; -方法二process begin wait until (clk=1) ; -等同于

13、等同于 wait until clkevent and clk=1; Q=D; end process;End behav;方法二 process(clk) begin if (clk=1) then Q=D; -利用进程启动特性产生对利用进程启动特性产生对clk的边沿检测的边沿检测 end if ; end process; end behav;时序逻辑电路时序逻辑电路触发器触发器触发器的仿真波形如下触发器的仿真波形如下当时钟上升沿到来时,把当时钟上升沿到来时,把D的值赋给的值赋给Q,之后保持不变。,之后保持不变。到下一个时钟上升沿到来时,再次把到下一个时钟上升沿到来时,再次把D的值赋给的值

14、赋给Q。时序逻辑电路时序逻辑电路触发器触发器时钟边沿检测的三种方法时钟边沿检测的三种方法方法一方法一: 上升沿:上升沿:clock event and clock=1 下降沿:下降沿:clock event and clock=0;注意:if clock event and clock=1语句后面不存在else分支。当clock为std_logic类型时,也可以利用 if rising_edge(clk)或If falling_edge(clk)进行时钟边沿检测。方法二:方法二: 利用利用WAITWAIT语句启动进程,检测语句启动进程,检测colckcolck的上升沿。的上升沿。方法三:方法三

15、:使用使用PROCESSPROCESS语句和语句和IFIF语句相结合实现语句相结合实现。当。当colckcolck发生跳变的时候发生跳变的时候启动启动PROCESSPROCESS进程,而在执行进程,而在执行IFIF语句时,满足语句时,满足clock=1clock=1时才对时才对Q Q进行赋值更新,所以相当于进行赋值更新,所以相当于clockclock发生跳变且跳变为发生跳变且跳变为11时,将时,将D D赋给赋给Q Q,实际上就是,实际上就是D D触触发器的描述。发器的描述。时序逻辑电路时序逻辑电路触发器触发器带有带有Q非的非的D触发器触发器由下图可知,与由下图可知,与D触发器相比,该触发器多了

16、触发器相比,该触发器多了Qbar与低电平与低电平有效的异步复位信号有效的异步复位信号带有带有Q非的非的D触发器触发器带有带有Qbar的的D触发器触发器D触发器触发器时序逻辑电路时序逻辑电路触发器触发器带有带有Q非的非的D触发器应该如何描述?触发器应该如何描述?ENTITY D_FF IS PORT(D,clock:IN std_logic; Q,Qbar:OUT std_logic;)END D_FF;ARCHIECHTURE behav OF D_FF ISBAGIN PROCESS(clock) IF rising_edge(clock) THEN Q= D; Qbar= NOT D; E

17、ND IF; END PROCESS;END behav; 错误错误:在时钟上升沿在时钟上升沿下有两个赋值,这样就会下有两个赋值,这样就会引入两个引入两个D触发器而不是一触发器而不是一个触发器。个触发器。时序逻辑电路时序逻辑电路触发器触发器带有带有Q非的非的D触发器应该如何描述?触发器应该如何描述?正确描述一正确描述一(信号法信号法)Architecture sig of D_FF is signal state: std_logic ;Begin process( clock, reset) begin if (reset=0) then state=0; else if rising_ed

18、ge(clock) then state=D; end if; end process; Q=state; Qbar=not state ; End sig;时序逻辑电路时序逻辑电路触发器触发器带有带有Q非的非的D触发器应该如何描述?触发器应该如何描述?正确描述二正确描述二(变量法变量法)Architecture var of D_FF is Begin process(clock, reset) variable state: std_logic ; begin if (reset=0) then state:=0; elsif rising_edge(clock) then state:=

19、D; end if; Q=state; Qbar=not state; end process;End var;点评:点评:当当state定义为定义为变变量量时,其时,其有效范围在有效范围在process内。内。因此,因此,Q和和Q非的非的赋值语句只能放在赋值语句只能放在process里面。里面。时序逻辑电路时序逻辑电路触发器触发器带有带有Q非的非的D触发器的仿真触发器的仿真信号法的仿真波形:信号法的仿真波形:变量法的仿真波形:变量法的仿真波形:时序逻辑电路时序逻辑电路触发器触发器JK触发器触发器 真值表真值表:JK触发器:时序逻辑电路时序逻辑电路触发器触发器JK触发器的触发器的VHDL描述描

20、述Entity JK_FF is port ( J, K: in std_logic; clock,reset:in std_logic; Q, Qbar : out std_logic );End JK_FF; Architecture behav of JK_FF is signal state : std_logic ;Begin process( clock, reset) variable jk: std_logic_vector(1 downto 0); begin jk:=J&K; if (reset=0) then state state state state nul

21、l; end case; end if;end process; Q=state; Qbarnull;时序逻辑电路时序逻辑电路触发器触发器JK触发器的仿真触发器的仿真可见仿真波形与真值表一致。可见仿真波形与真值表一致。时序逻辑电路时序逻辑电路触发器触发器T触发器触发器 真值表真值表: T触发器触发器:时序逻辑电路时序逻辑电路触发器触发器Entity T_FF is port ( T, clock, reset : in std_logic ; Q, Qbar : out std_logic );End T_FF;Architecture behav of T_FF isBegin proces

22、s(clock, reset) variable state: std_logic ; begin if (reset =0) then state:=0; elsif rising_edge(clock) then if T=1then state := not state; end if; end if ; Q=state; Qbar= not state; end process;End behav ; T T触发器的触发器的VHDLVHDL描述描述: :时序逻辑电路时序逻辑电路触发器触发器T触发器的仿真波形如下:触发器的仿真波形如下:可见仿真波形与真值表一致。可见仿真波形与真值表一致。

23、时序逻辑电路时序逻辑电路触发器触发器寄存器的设计寄存器的设计时序逻辑电路时序逻辑电路寄存器寄存器多位寄存器:多位寄存器: 一个一个D触发器就是一位触发器就是一位寄存器寄存器,如果需要多位寄存器,就要用,如果需要多位寄存器,就要用多个多个D触发器构成。触发器构成。时序逻辑电路时序逻辑电路寄存器寄存器Entity reg is generic( n: natural :=4 ); -实体类属中的常数实体类属中的常数 port ( D: in std_logic_vector(n-1 downto 0); clock, reset : in std_logic; Q: out std_logic_v

24、ector (n-1 downto 0) );End reg ;Architecture behav of reg isBegin process(clock, reset) begin if (reset=0) then Q0); -表示表示Q赋全赋全0 elsif rising_edge(clock) then Q=D; end if; end process;End behav ;多位寄存器的多位寄存器的VHDLVHDL描述描述: :时序逻辑电路时序逻辑电路寄存器寄存器移位寄存器:移位寄存器:我们这里讨论的是串进并出的移位寄存器,即串行输入,我们这里讨论的是串进并出的移位寄存器,即串行输

25、入,在时钟的边沿移位进寄存器,形成并行输出在时钟的边沿移位进寄存器,形成并行输出- - - - - - - - - - - - 原来的数据+- - - - -要移走的数据和要加入的数据- - - - - - - - - - - - -移位后的数据时序逻辑电路时序逻辑电路寄存器寄存器串进并出的移位寄存器的串进并出的移位寄存器的VHDLVHDL描述描述: : Entity sipo is generic( n : natural :=8); port ( a : in std_logic ; q: out std_logic_vector(n-1 downto 0); clk : in std_l

26、ogic );End sipo;Architecture behav of sipo isBegin process(clk) variable reg : std_logic_vector(n-1 downto 0); begin if rising_edge(clk) then reg : = reg ( n-2 downto 0) & a ; -左移移位寄存器;左移移位寄存器; - reg : = a & reg (n-1 downto 1); 右移移位寄存器右移移位寄存器 end if ; q= reg ; end process;End behav;时序逻辑电路时序逻

27、辑电路寄存器寄存器串进并出的位寄存器的仿真串进并出的位寄存器的仿真 输入输入8位数据位数据11100100,从仿真波形可以看出,从仿真波形可以看出,8位数据是从低位左位数据是从低位左移存储到寄存器中的。移存储到寄存器中的。时序逻辑电路时序逻辑电路寄存器寄存器 计数器的设计数器的设计计时序逻辑电路时序逻辑电路计数器计数器计数器的作用计数器的作用主要是对脉冲的个数进行计数,以实主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时现测量、计数和控制的功能,同时兼有分频功能。比如七位计数器,兼有分频功能。比如七位计数器,可对输入时钟进行七分频。可对输入时钟进行七分频。时序逻辑电路时序逻辑电路

28、计数器计数器计数器计数器计数是一种最简单基本的运算,计数器就是实现这种计数是一种最简单基本的运算,计数器就是实现这种运算的逻辑电路运算的逻辑电路计数器的实现计数器的实现 Library ieee ;Library ieee ;Use ieee.std_logic_1164.all;Use ieee.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use ieee.std_logic_unsigned.all;Entity counter is Entity counter is generic( n: natural :=4);generi

29、c( n: natural :=4); port ( clk : in std_logic; port ( clk : in std_logic; reset : in std_logic ; reset : in std_logic ; count : out std_logic_vector(n-1 downto 0) ); count : out std_logic_vector(n-1 downto 0) );End counter;End counter;1 1、用、用“+”+”函数描述:函数描述:时序逻辑电路时序逻辑电路计数器计数器计数器的实现计数器的实现 architecture

30、 ripple of counter is component T_FF is port( T : in std_logic ; clk:in std_logic; reset:in std_logic; Q : out std_logic; Qbar:out std_logic); end component ; -将前面描述好的将前面描述好的T触发器定义为元件;触发器定义为元件; signal carry: std_logic_vector( n downto 0);Begin carry(0)=clk; g0: for i in 0 to n-1 generate -循环循环 T1: T

31、_FF port map ( 1, carry( i ), reset, count( i ), carry( i+1 ) ); end generate g0;End ripple ;时序逻辑电路时序逻辑电路计数器计数器计数器的实现计数器的实现 g0: for i in 0 to n-1 generate -循环循环 T1: T_FF port map ( 1, carry( i ), reset, count( i ), carry( i+1 ) );可以分解成:可以分解成: T0: T_FF port map ( 1, carry( 0 ), reset, count( 0 ), carry(1 ) ); T1: T_FF port map ( 1, carry( 1 ), reset, count( 1 ), carry( 2 ) );T2: T_FF port map ( 1, carry( 2 ), reset, count( 2 ), carry( 3 ) );T3: T_FF port map ( 1, carry( 3 ), reset, count( 3 ), carry( 4 ) );Tn-1: T_FF port map ( 1, carry( n-1 ), reset, count( n-1 ), co );上例程序中的循环:上例程序中的循环:

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 性教育:如何保护自己

- 关于对外投资合同样本

- 损耗基础知识

- 2024年份第四季度行政文书智能校对系统整合古典语法规则

- epc框架合同范例

- 保险赔付合同标准文本

- ups维修合同标准文本

- 人才引进劳务合同标准文本

- 与设计合作合同标准文本

- 公寓车位出租合同标准文本

- 《线面平行的判定》课件

- 《电力工程电缆设计规范》

- 与发包人、监理及设计人的配合

- 2022-2023学年北京市怀柔区八年级下学期期末语文试题及答案

- 腹腔压力监测演示文稿

- 《匆匆》朱自清ppt课件-小学语文六年级

- 高中生读后续写现状调查报告1 论文

- 汽油机振动棒安全操作规程

- 认证咨询机构设立审批须知

- 项目式学习 知甜味百剂 享“甜蜜”人生 阿斯巴甜合成路线的设计 上课课件

- GB/T 7971-2007半导电电缆纸

评论

0/150

提交评论