版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

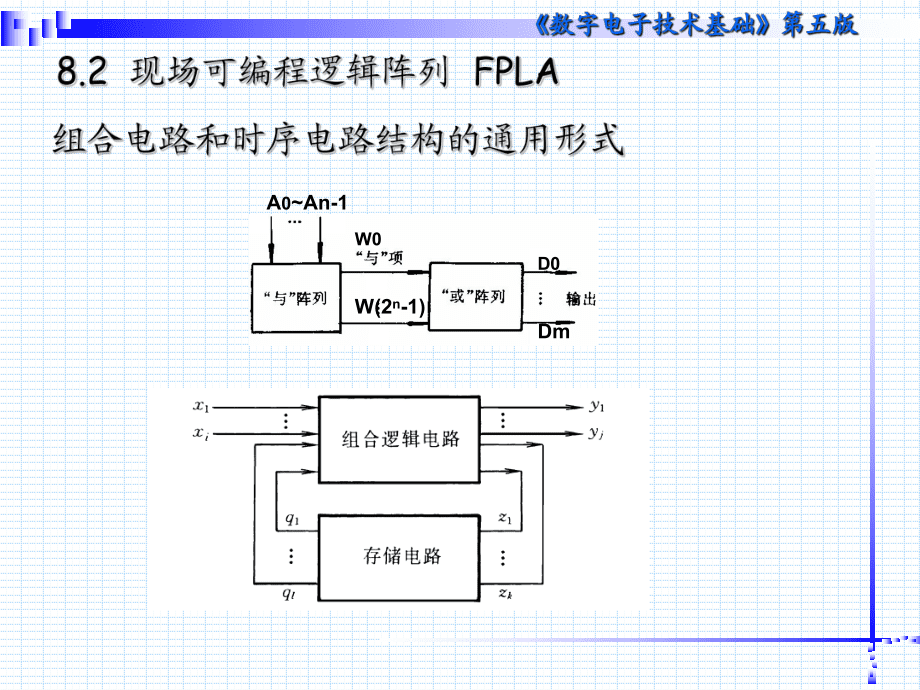

1、数字系统A0An-1W0W(2n-1)D0Dm可可编编程程的的“或或”阵阵列列可可编编程程的的“与与”阵阵列列 用途:产生组合逻辑电路用途:产生组合逻辑电路用途:组合逻辑电路,用途:组合逻辑电路,有三态控制可实现总线连接有三态控制可实现总线连接可将输出作输入用可将输出作输入用用途:产生时序逻辑电路用途:产生时序逻辑电路时序逻辑电路时序逻辑电路还可便于对还可便于对“与与- -或或”输出求反输出求反时序逻辑电路时序逻辑电路可产生可产生A、B的十六种算术、逻辑运算的十六种算术、逻辑运算2、输出结构类型太多,给设计和使用带来不便。、输出结构类型太多,给设计和使用带来不便。2、输出端设置了可编程的输出逻

2、辑宏单元(、输出端设置了可编程的输出逻辑宏单元(OLMC)通过)通过编程可将编程可将OLMC设置成不同的工作状态,即一片设置成不同的工作状态,即一片GAL便可实便可实现现PAL 的的5种输出工作模式。器件的通用性强;种输出工作模式。器件的通用性强; GAL的优点:的优点:1、由于采用的是双极型熔丝工艺,一旦编程后不能修改;、由于采用的是双极型熔丝工艺,一旦编程后不能修改; PAL的不足:的不足:1、采用电可擦除的、采用电可擦除的E2CMOS工艺可以多次编程;工艺可以多次编程;3、GAL工作速度快,功耗小工作速度快,功耗小 GAL的电路结构与的电路结构与PAL类似,由可编程的与逻辑阵列、类似,由

3、可编程的与逻辑阵列、固定的或逻辑阵列和输出电路组成,但固定的或逻辑阵列和输出电路组成,但GAL的输出端增设了的输出端增设了可编程的的输出逻辑宏单元(可编程的的输出逻辑宏单元(OLMC)。通过编程可将)。通过编程可将OLMC设置为不同的工作状态,可实现设置为不同的工作状态,可实现PAL的所有输出结构,的所有输出结构,产生组合、时序逻辑电路输出。产生组合、时序逻辑电路输出。可编程与阵列可编程与阵列(32X64位)位)2、GAL举例举例GAL16V8的电路结构图的电路结构图8个个输输入入缓缓冲冲器器298个反馈个反馈/输入输入缓冲器缓冲器8个三态个三态输出缓冲输出缓冲器器12198个输出逻辑宏单个输

4、出逻辑宏单元元OLMC输出使能缓输出使能缓冲器冲器可编程逻辑器件中的宏单元可编程逻辑器件中的宏单元 D Q Q 输输出出 C OE CLK 输输入入 数据选择器数据选择器数据选择器乘积项数据选乘积项数据选择器择器(2(2选选1)1)输出数据选择输出数据选择器器(2(2选选1)1)三态数据选择器三态数据选择器(4(4选选1)1)反馈数据选择反馈数据选择器器(4(4选选1)1)4 4个数据选择器:用不同的控制字实现不同的输出电路结构形式个数据选择器:用不同的控制字实现不同的输出电路结构形式乘积项数据选择器:乘积项数据选择器:根据根据AC0和和AC1(n)决定与逻辑阵列的第一乘决定与逻辑阵列的第一乘

5、积项是否作为或门的一个输入端。只有在积项是否作为或门的一个输入端。只有在G1的输出为的输出为1时,第一时,第一乘积项是或门的一个输入端。乘积项是或门的一个输入端。乘积项数据选择器乘积项数据选择器( (2选选1)OMUX:根据:根据AC0和和AC1(n)决定决定OLMC是组合输出还是寄存器是组合输出还是寄存器输出模式输出模式输出数据选择器输出数据选择器(2选选1)OMUX三态数据选择器三态数据选择器(4(4选选1)1) 三态数据选择器受三态数据选择器受AC0和和AC1(n)的控制,用于选择的控制,用于选择输出三态缓冲器的选通信输出三态缓冲器的选通信号。可分别选择号。可分别选择VCC、地、地、OE

6、和第一乘积项。和第一乘积项。工作AC0 AC1(n)TX(输出)(输出)0 1地电平地电平0 0VCC1 0OE1 1第一乘积项第一乘积项工作工作高阻高阻OE=1,工作,工作OE=0,高阻,高阻1,工作,工作0,高阻,高阻三态缓冲器三态缓冲器的工作状态的工作状态FMUX:根据根据AC0和和AC1(n)的不同编码,使反向传输的电信号也对应不同的不同编码,使反向传输的电信号也对应不同。反馈数据选择器反馈数据选择器(4选选1)OMUX1. 通用阵列逻辑(通用阵列逻辑(GAL)在在PLA和和PAL基础上发展起来的增强型器件基础上发展起来的增强型器件.电路设计者可根据电路设计者可根据需要编程,对宏单元的

7、内部电路进行不同模式的组合,从而使输需要编程,对宏单元的内部电路进行不同模式的组合,从而使输出功能具有一定的灵活性和通用性。出功能具有一定的灵活性和通用性。2. 复杂可编程逻辑器件(复杂可编程逻辑器件(CPLD)集成了多个逻辑单元块,每个逻辑块就相当于一个集成了多个逻辑单元块,每个逻辑块就相当于一个GAL器件。器件。这些逻辑块可以通过共享可编程开关阵列组成的互连资源,实现这些逻辑块可以通过共享可编程开关阵列组成的互连资源,实现它们之间的信息交换,也可以与周围的它们之间的信息交换,也可以与周围的I/O模块相连,实现与芯片模块相连,实现与芯片外部交换信息。外部交换信息。5. GAL的编程与开发的编

8、程与开发 H HD DL L描描述述电电路路功功能能 验验证证、仿仿真真 排排错错、优优化化 编编译译 熔熔丝丝图图 文文件件 编编程程器器 GAL 器器件件 输输入入 状状态态表表 状状态态图图 逻逻辑辑方方程程 原原始始 设设计计要要求求 软件工具软件工具硬件工具硬件工具1. IOB2. CLB3. 互连资源4. SRAM可以设置为输入可以设置为输入/ /输出;输出;输入时可设置为:同步(经触发器)输入时可设置为:同步(经触发器) 异步(不经触发器)异步(不经触发器)本身包含了组合电路和触发器,可构成小的时序电路本身包含了组合电路和触发器,可构成小的时序电路将许多将许多CLB组合起来,可形成大系统组合起来,可形成大系统数据可先放在数据可先放在EPROM或或PC机中机中通电后,自行启动通电后,自行启动FPGA内部

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 厦门非制式合同模板

- 会议签署战略合同模板

- 买卖树合同模板

- 小型土建包工合同模板

- 公司与法人合伙合同模板

- 保山代理记账合同模板

- 合伙生意内部合同模板

- 买按揭车合同模板

- 建设个施工合同模板

- 乡镇招商引资协议合同模板

- DL∕T 5210.6-2019 电力建设施工质量验收规程 第6部分:调整试验

- 一例登革热合并凝血功能障碍患者的个案护理20190-7

- 门诊病历书写模板全

- 《图形创意设计》PPT课件(完整版)

- 全国医疗服务价格项目规范(2012版)

- 二年级乘除法口算题大全500题(可直接打印)

- EJA技术交流会资料

- 输变电工程基础工程施工工艺(附实景图)

- 江苏如东LNG接收站使用协议

- 教师如何加强自身修养

- 高等医学院校临床教学基地设置条件与认定程序

评论

0/150

提交评论