版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、8英寸晶圆0.18微米逻辑制程工艺晶圆(Wafer)的生产主要分为前中后段,前段主要是针对器件的生产工艺. 包括扩散、离子注入、微影、蚀刻.快速热处理、化学气相沉积等工艺,通常所 说的。,18微米是对于栅极的尺寸而言的,而器件主要是出场效应管(MOS),二 极管,三极管.电阻和电容等构成中段是从作为欧姆搂触的硅化金属(Salicide)沉租到内层电介随ILD(L】tM Layer Dick diic)沉枳的完成.这段主要目的是形成电阻值较低的Saliciilc, 目的是 使后面的在线装前面的器件的连接形成较低的表面接触电阻;ILD个主夏作用 是灯前面器件的保护,使后面的布线工艺和外界不会对器件

2、的工作性能形成干 扰,另一个作用就是运用其良好的消充性能有效地填补了栅极或电容在物理上与 村底之间的高度容,便后面的化学机械就磨CMP (Chemical Mechanical Polish 工艺得以更好的发挥.对F后段工艺的界定上要是从ILD之后的接触孔(Con丽t)到最后的保护会 它起到了从捌件的生产到打线(Bonding)之间的桥梁的作用,随着工艺的先进 程度和电路的复杂程度小同,金属布线的层数也会越来越多,0.18微米逻箱产品 若采用66层的金属布2.1 双阱CMOS器件形成工艺流程苜先大概介绍辞片的准备,逻辑产品一般采用轩掺杂p型硅片晶向为 1001在进入真正相关的曙件形成匚艺之前,

3、还有一道我们称之为零层的工艺 由F集成电路是由很多层电路老赵组成的,需要用到二卜几层掩模版,因此必须 保证每一层掩模版的光刻在机件里有可以作为对齐的基淮J零层工艺会产生两个 对准结构,其在晶圆上的位置及结构组图2-1所示u晶圆前期准备工作完成后, 开始进入其正的揩件形成工艺一雷卡6sHMElm FrtiiL Mrl桔 i明事S 1-1 MH零层标志位置及造构示意图2L1场区隔离及平坦化0.18微米逻辑产品采用的场区隔离为浅槽隔离STI Shallow TnncliIsolation);苜先热粒化,形成缓冲层.从而减少下一步淀积氮化硅在硅表面造 成的用力,随后化学气相流枳氮化壮,作为浅沟隔离的平

4、坦化厚止层,在进行第 一次光刻前,还要淀枳一层氮氧化比,其主要作用是降低氮化畦的反射率,在光 刻时有效控制关键尺寸.接下来以有源区AA (ActiveA的掩模版.通过光 刻把有源区的图案.林移到枯阿匕接着以干式蚀刻把无光刻胶保护的轨家化硅. 篦化硅及热氧化形成的辑冲层从拈片表面除去,形成隔离用的沟槽由,如图2-2 所示.图2-2 STJ附岗小点图在挖开隔离的沟槽之后,算是第一个阶段的作完成 接卜来送行浅沟槽隔 离的第二个阶段,也是重头戏,即二氧化硅的沟填。在沟填之前,通常先把晶片 送入热炉管内,以高温氧化的方式在沟栗的表面上生长成 层二氧化硅,并称之 为衬底氧化层(Liner Oxide),如

5、图2 J所示这一东工艺的目的主要行两个; 一是修补因为干式饨刻所造成的沟槽表面的损伤;二是借助硅的热氧化把沟槽上 端的角落予以国化.我们称之为角缘圆化(CcrnRoimding) .W2-3牛K衬底雷化层后ST1隔离示意图完成沟槽村底氧化层的应氏之后,接下来进行彻槽的埴无。这个我骤都是使 用化学气相淀枳CVD (Chemioil Vapor Depositinii)来完成.对F 0 18用米逻辑 产品,我门采用渴埴能力良好的奇密度等:离子体HDP (High Density Pl asma 方法.通过沉积/蚀发明fi枳的原理完成沟槽的填充风接着遴行一次高温回火的 处理,把CVD沉积的SiO?(

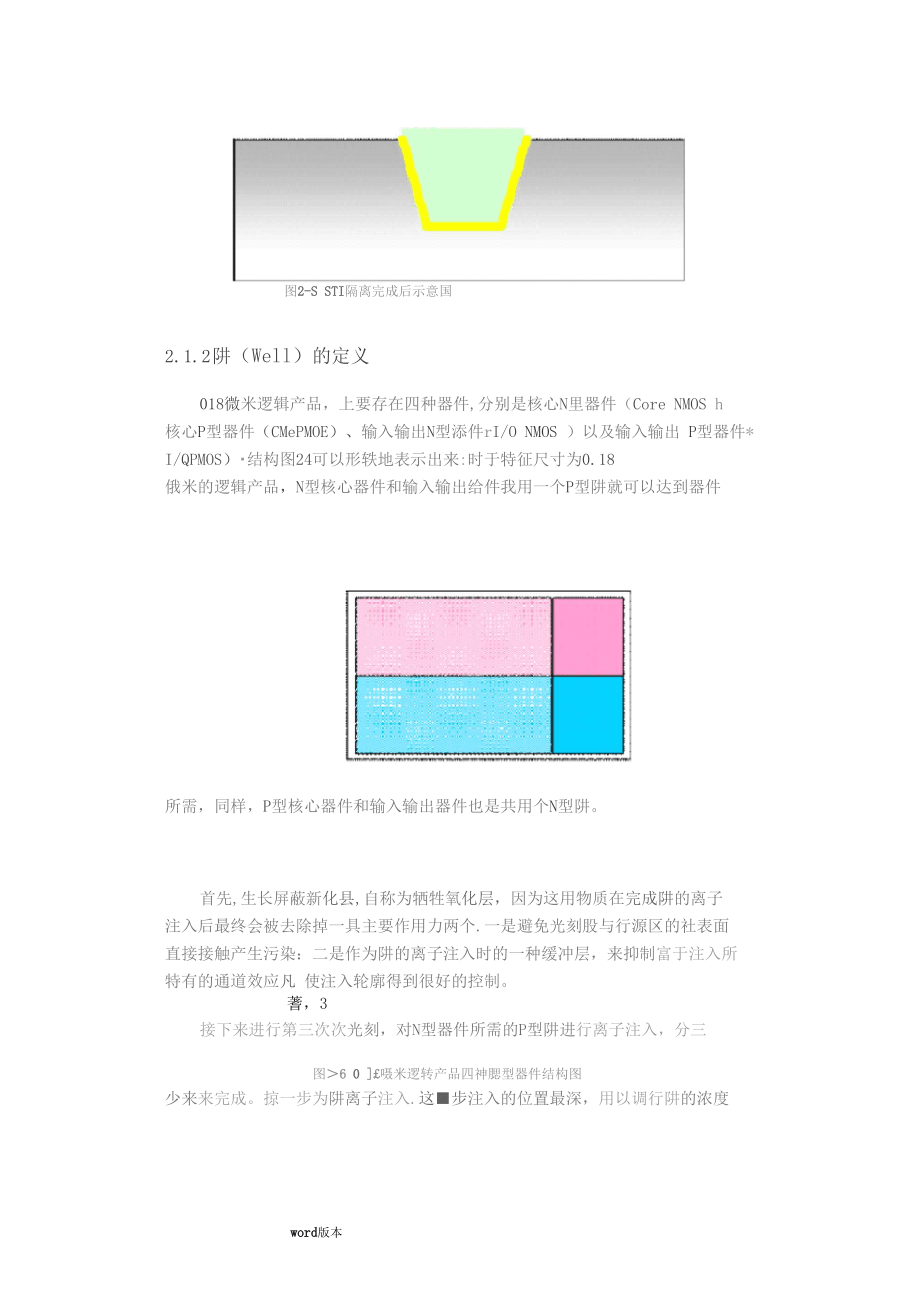

6、二氧化碎)的密度以及像沉积膜的质晨提升,以易 后续工艺的进行。沟梢填充完毕后,后同的有源区之上会上有不同面积的Si6,而面枳越大 越不容易被后姨的平坦化工艺研磨掉.对于上述问题,主要增加一层掩模版工艺 流程,栗用蚀刻泣来解决.其主旨是,在有源区面积较大的地方,光刻工艺后会 被曝光显影而露出来,然后以馍刻方式把大块的图6去除掉,示意图如“.而 后进行平坦化.平坦化制程会把氯化硅之上的Sig彻底的清除干净,否则会给 接下来的篦化碎的湿式清除带来很大麻般,但是也不能为把阖0父疗除干净而 执仃太久的过度研磨,使贰化硅的厚度太低.此外,STICMP常见的一些缺陷问 题.如造成氮化硅层的微细刮伤,及研磨液

7、残招等风 也要小心的应付,留?尺新地撞模层蚀剌后市花圈最后,采用湿式刻蚀,在不会时硅材质表面造成损伤的方式下,把构成硬式 罩幕层结构的氨化硅与热氧化生成的缓冲层Si6予以清除阅囿,从而完成如图 2-5示的整个$11的制程.图2-S STI隔离完成后示意国2.1.2 阱(Well)的定义018微米逻辑产品,上要存在四种器件,分别是核心N里器件(Core NMOS h 核心P型器件(CMePMOE)、输入输出N型添件rI/O NMOS )以及输入输出 P型器件* I/QPMOS)结构图24可以形轶地表示出来:时于特征尺寸为0.18 俄米的逻辑产品,N型核心器件和输入输出给件我用一个P型阱就可以达到

8、器件 所需,同样,P型核心器件和输入输出器件也是共用个N型阱。蓍,3图6 0 嗫米逻转产品四神腮型器件结构图首先,生长屏蔽新化县,自称为牺牲氧化层,因为这用物质在完成阱的离子 注入后最终会被去除掉一具主要作用力两个.一是避免光刻股与行源区的社表面 直接接触产生污染:二是作为阱的离子注入时的一种缓冲层,来抑制富于注入所 特有的通道效应凡 使注入轮廓得到很好的控制。接下来进行第三次次光刻,对N型器件所需的P型阱进行离子注入,分三 少来来完成。掠一步为阱离子注入.这步注入的位置最深,用以调行阱的浓度防止闩锁粒成(Lfltclwip)叫 第二步为索道离子注入,其位置较注些,主盥届为了加大源漏区域之下部

9、位的冰浓度,使器件工徨时该位置的耗用层更察,防 止器件的源漏因为耗尽区相接而发生的穿通现象.第二:步为阈值调整注入.离于 注入深度最浅.靠近需件衣面.调节器件的开启电三步离了注入完成后去除 光刻胶,完成P型阱的制备.同样流程进仃第四次光刻米制备P型器件所需的N型阱,所不同的只是注 入离子的类型,所以这里不再做电豆描述。示意图如图2-7图a与图b所示。离子注入技术的最大优点是可以精确地控制掺杂杂质的浓度和深度。但是 在离f注入的过程中,村底的品体结构受到强伪*小川避免的,这种损伤会对材 料的电学性质产生重要的影响。例如,由于散射中心的增加,便载流子迁移率下 降:缺陷中心的增加,会使非平衡少数载流

10、子的殍命减少. p4l结的漏电流也会 因此而增加,另外,离子注入射入的杂质原子大多数都存在于晶格间隙位置,起 不到施主或受主的作用.所以在阱的离子注入制程完成后,会再做一步热退火处 理,消除品珞损伤,并使注入的的杂施转入替位位段以比现电激活口最后采用湿代刻蚀方式去除牺牲氧化层,完成整个阱的制备工作.2.1.3 栅极形成上一小节提到,逻辑产品有用到核心器件和输入输出聘件.核心器件供底电 1k:为L8伏,输入输出镭件供应电压为33伏。所以需要制备两种不同厚度栅氧 化层来满足不同的取值电年所霰。首先进行预氧化清洗.硅清洗的工艺基本准则是消除表面有机物,过渡金属 和碱性离子以及颗粒。如果在氧化前不将晶

11、片的玷污除尽,必将影响栅氧化层的 侦量,从何会U接改变产品的器件特性,清洗工艺由两步组成.第步为了除去 M表面的行机物玷污,第二步为了通过形成金属络合的除去金属培污一为了除去 在第一步清洗中生成的二氧化硅,常常坤输 个中间步,用稀释的HF1策毓) 酸漂洗.晶片清洗完后,即进行第一层楣氧化层的制备.0.1S微米逻辑制程里已经使 用较薄的册氧化层,所以通常采用低温(8000 亚氮氧化的方法,生长的氧化 层质曷较好 第一层棚氧化层生长完成后.接着进行第五次光刻,用湖式刻蚀的 方式把核心器件区域的棚耳化层去除,输入输出器件区域的桩家化层保留,然后 再进行晶片的清洗,制备第一层较薄的棚氧化层.这样,两次

12、热氧化的制备完成 输入输出器件的栅轨化层.用.次热氧化的制备完成核心器件的热同化层,结果 小意如图2s不 需要注意的是,输入输出器件的栅质化层的厚度,井小是两次 热曩化生成的氧化层厚度的总和。这是因为,徘的热氧优是珪与氧或水汽等氧化 剂,在高温条件下经过化学反应生成栅氧化层,当硅表面上生成一定厚度的二氧 化硅层,氧化剂必缅以扩散方式运动到硅-二氧化硅界面,再与硅反应生成二氧 化硅切口叫因此,随着二氧化硅厚度的增加,生长速率将逐渐下降,所以,输入 输出器件的抑氧化层厚度比两次热氧化生成的厚度总和要薄一些FYE加 IT 巾;Jiii.rTnrtF、1图38两次热氧比形成棚彷化尽后的小近囱接下来.在

13、整个晶片上生成一层名品徒.利用第六次光刻.盘成器件棚板及 多晶硅作为相关也阻所需的图案,然后用干式蚀刻的方式把不需要的多晶硅去 除,这一步的关键是控制好关键尺寸.闺为它会直接影响特征罂件的沟道长度.在蚀刻去胶完成后,会对多晶砧栅进行再氧化(Ro-Oxi&tiou),以修补多晶硅 地刻时栅氧化层造成的损伤.栅极制备完成后的结构如图工囚所示.2.L4 轻掺杂漏极 LDD (Lighllj Doped Drain)舱宿集成电路将征尺寸不断缩小,器件的沟道氏度缩短之后,热敦流效应 会对蹲件特性产生很大的影响口为降低热载流子效应,Q18微米逻辑制程采用轻 掺杂艺.以加强型NMOS为例,即在原来的MO乱的

14、源极和海极抠近通道的地 方,再增加一组掺杂程度较原来口型源极与漏极为低的n型!/.如图210所示 我们称这种设计为44轻掺杂漏极(LigMyDopDaiii) *简称为LDD图2-1。用LDD设计的NMCI电晶体外观很明显的,仃LDD设”的NMOS的通道电场分布,将往漏极移动,且电场 的大小也会变低口明 因此,*热载流子效应谢影响力便可以减轻口此外,热就 流广效应用对MCS还有另一个影响,因热电撞击所产生的电子,除大多数被溷 极所吸收以为,也有一部分电子跄越H氮化层界面而往那极移支,这些电子大多I 棚氧化层内,使灵化层内的电荷改变,从而导致阅值电3 Vt产 生.变化LDD的谩计,也会减少这美问

15、题的发生,但是,LDD的使用也有一些缺点。首先,它将使得MOS的制作变得复杂: 其次,因为LDD的掺杂程度较低,电阻也就比发高,使得漏极到源极的用以电 阻增加,这将导致元件的操作速度肆低,且电力的消耗上升:不M,因为LDD 的诸多优点,它己经被广泛应用,短通道的CMOS的元件设计当中.0.18微米逻辑产品会有四道光刻流程,在所需位置完成四种不同器件的轻掺 泉工艺。2.1,5 侧墙(SPACERSictewalD 形成LDD流程之后是便|墙SPACER的形成,Q1S微米逻辑产品的侧墙采用ONO 结构,即Orick-Niti加Qxidc.先用热辄化法生长一层150埃左右的氧化物Lining TEO

16、S (TcUactliyl Oithosilicate)作为恻墙蚀刻氮化硅(Nitri加)的停止层,也作 为氮化硅的缓冲层,减少氮化硅对硅的应力。然后再生长一层氮化硅,这是主要 的,但不能太厚,太用会对下层Lini隼TEOS造成损伤.导致其支撑不住.但是 侧墙乂要求有一定的厚度,所以在氤化硅的上面还要再生长一层硅轲化物TEOS. 这样就形成了 0N0培构-.I: i X? I.nmisTEOS 上停TEOS,但是并没有完全去掉,最后还会留有很薄一层作为后续源漏重掺杂的掩 蔽层。恻墙形成后的器件示意图如图2-11所示,图11 墙SPACER地则后的器件示意图2.16源漏形成接下来进行第十一次光刻

17、,即N-注入区光刻,并对NMOS进行源漏重搀生 注入,同时形成N+彩晶硅棚和PMOS的用体区引出:然后是用注入区光刻. 并对PMOS进仃源漏电物朵注入.同时形成NMUS管的体区引出源潮形成 后器件剖面示意如图2-12所示.eg22源漏滋成后状伴剖面水.盘图以上就完成了上脏针对器件的前段生产工艺,接卜来的第二行内容会对中段 的欧姆接触以及作为器件保护的ILD层工艺流程做介绢.Z2欧姆接触以及ILD工艺流程2.2.1欧姆接触形成隹集成电路芝中,格成良好的欧姆接触,以减少串联电阻也是关键的一环, H前城常采用硅化物形成良好的接触,睢化物(Salitide)城常是指硅与难熔金 属形成的化合物:这种材料

18、能够有效地降低接触区的接触电阻和掺杂多晶硅的串 联电阻.用于硅化物的常见金属fh Ti, Co, M, W等叼,而。.18微米逻辑产 品选用金属Co (钻i与珪反应生产相应的硅化物。笈工来做欧姆接触.苜先淀积一层富含硅的二祝化硅SRO (Silicon Ri h Oxide).然后进行第十 三次掩模和光刻作用,把需要做低阻欧姆接触的源漏区以及引出区显现出来,这 样就保证了在不需要硅化物的地方防止生成琏化物做电阻.另外,SRO比较致 密.n以防:卜源漏报成时注入的杂竭从表由1折出、为保证界面干净和平整.预清洗后尽快淀积一层C。薄膜,然比进行第一次 高翻热退火,会属Co与硅或多晶硅接触的地方发生反

19、附生成金属桂化物(CoSiJ 而在金博4 H蛙的接触区域则不会发t反忌 期;上除未反卮的方氽金属,子是 多晶仁棚,源漏1M等露出硅层的区域完全俄硅化物所曾蛊,而其他没宥露出硅层 的区域则不存在硅化物。然后进行第二次高温退火以进步降低硅化物的薄层电 阳.欧姆接触形成后的器件冽面示意如图243所示.CO SBlCd02.2.2 ILD工艺流程ILD的结构为期乳化M SION/硼磷BP-TEOS/等嘀了怵强PEEiilianced) TEOS首先在晶圆表面淀积一层氮氧化硅,其作川一是保护下面的器件,防止后续 他磷睢破瑁BPSG BoronPhohoms Silicon Glass)中的硼析田渗透到下

20、面而影 响器件的特性,二是作为接触孔独刻的停止层.在ILD中不用HDPTEOS是因为I1D自器件的去而太近容易产生损伤,斫 以用BPSG来埴汴棚极或电容在物理卜与衬底之间的高度差,而BFSG的研磨速 率较慢,因此乂淀积一层PETEOS,以减小由于BPSG慢度过小布后一步干坦化 时造成的划伤.下图2-14洽出了 ILDCMP之后的截面不意图:图114 ILD E M P之后的他所不1意图2.3后段多层金属互连工艺流程随着集成度的犷大.互连线所占面积已经成为决定芯片面积的主要因素.互 连线导致的涎迟已经可以与篙件门延迟相比较gJ多层金属互连技术对超大规模 集成电路的苣义&百先.使川参层金属互连技术

21、可以使VLSI的集成密度大大增加,从而可使 集成度进一步提高二互连线的数廿是随器件的数目增加而增加的,而单位面积上 可以实现的连线数是有限的.使用弟层互连,可以使单位芯片面积上可用的五连 线面积成倍增加,从而可以允许有更多的互连线口其次,使用多层金属互连可以 降低互连线导致的延退时间.此外,由卜多层互连技术的使用,可以在更小的芯 片面积上丈现相同功能,这样在单个硅片上可制作出更多芯片,从而可以降低单 个芯片的成本.当然互连线每增加一层.需要增加两块掩模版,而且还可能导致 总产品率的下降,互连线层数也不是越多越好.23.1接触孔(Contact)的形成连接下层器件9第一层金属导线的孔称之为接触孔

22、( Contacts .首先在前段ILD层表而沉积 层氮氧化硅件为防反射层,它可有效地减弱 反射对分辨率的影响,使后面的接触孔显影得以正常进行.在后续金属连战层以 及中介孔施模光刻工艺前都会沉积一层氮氧化硅作为防反射层接下来进行第十 四次光刻流程,把接触孔掩模版上的图形转移到晶圆之上,运用干法蚀刻的方法 使接触孔孔成型匚应当注意的是为了保证各处蚀刻没有氧化膜残留在作为欧如接 触的硬化物_L,防止断蹄的情况发生,工艺会在他刻到硅化物后再加上定的过 独刻,这样之前形成的硅化物就会有定量的厚度损失,这个量应当掌握好.因 为砧化物的厚度宜接影响到了以后PCM测试的衣面接触电阻的人小二在光刻胶去除后是接

23、触孔粘合层沉枳,在接触孔内沉积Ti8k)和TiN (氨化 钛)作为粘合层.Ti的粘连性好,但Ti与WFE (加化鸿)反应会发生爆炸,所 以会加上-ETiNc TiN作为限挡层,能有N防止各层间的化学相互作用以及原 子扩散口然后进行接触孔铝塞沉根,在接触孔孔内沉积金属铝,作为插塞(plugi 连接卜层器件和金属层。最后进行接触孔铝塞的化学机械研磨,目的是将接触孔之外的铝研磨掉.图 2-15为工艺完成后的剖面结构图。这层的重点是确保二氧化硅表面不会有任何未 被磨除的鸦金属残留,只留下接触孔中的部分川作金闻导线的连接.防止产生短 路现象。考虑到晶圆表面研磨的均匀性差别,所以要磨到使二氧化硅表面略低于

24、铝插塞,从而可确保表面各个位置没T:鸨金属残留.如下图316以0一2蔻米制 程为例,可以看到通常二氧化硅表面会被磨到低于铅插塞10040。埃。1 2-15接触扎CMF之后的剖面结构图图21 (5铛研厝后的TEM照片忤2,3.2第一层金属连线以及内层金属电介质隔离形成由于本身电阻率低为在3a om左右),且刈:氧化硅层的附看R好,)- 旦容易以BCh (氯化硼),Ck (氯气)的干法讪刻加以加工成形,金属铝已为半 导体普遍用来作为元件的主要导电材料,以降低RC时间延迟.并提升元件的开 友频率小工艺上运用物理气相沉积戢镀PYD (Pliysical Vapm DepositiMi) Sputter

25、ing法完成金属层采用了三明治结构.即结构为TiBN/AlQwTi/nN,即钛/氟化钛/铝铜 /钛/颊化钛,如下面示意图2-17所示,第一层置作为粘结层是金属铝例(A1CU:I 更容易沉积,TiN作为夹层防止上下层的材料交互犷散,第 =11根据实除工艺 需要决定其存在与否,最上面的TiN作用除了防止胃互扩散外,还可作为后面中 介孔蚀刻的停止层。m2-i7金属层的三明治结构小意图以多元形式存在的铝.吊线存在电迁移现象.为铝厚丁沿看刊的晶粒边界移动 所致,它会使某些铝线版成空洞甚至断开导致断路口皿而在铝层的另些区域生 氏品须,导致电极短路,极大地影响电性和可靠性-如图18所示.12-13制2线L江

26、科现象为更好的解决这个问题.通常在金属靶材里面加入少量的铜(含量约在 0.5d%之间)口匀来抵制它的发生。加入铜后,将使部分铝的M粒边界为铝铜合金 所塞入,以至于使铝产生电1移所需能量上升,来抑制其发生.金属县淀枳X成,通二第一层金属他模版的掩模和九刻作用正晶圆上再成所 需金属连线图案,运用干法蚀刻使铝身线成形.反应机理上主要包括化学和物理 蚀刻两个方面。氯气为其主要反应气体.物理上主要是靠Ar (fc)的表上来区 现“处外还需焚在反应时通入CIIF3(二鬣甲烷)口叫 它的f七用是减小刻蚀率来 对铝筏侧壁形成保护,使其免于遭受横向的侧面蚀刻,使蚀刻之后的关犍尺寸等 同于光刻狡尺、h这三方面会同

27、时进行要做到它修之间的相互平贲才能得到最 终合格的金属导线.对于金属导线的标准大体上包括以下几个方面:1.足够的光 刻脱残留.目的是为了防止对余属线顶部的损伤.2.足够的氧化物损耗(Oxide 】sQ目的是为了防止晶附表面蚀刻不均匀而带来的局部氧化物表面金属残留, 排除地路现象的发生,3一良好的金属轮廓外彬 图2-19为金属线蚀刻后的切片和 外形图口.余,导线与旧用现归:-SEMLM- |jS2-B金属线但刻后的切片和外彩图运用湿式去光刻胶法,去除光刻胶和聚合物Polymer金属蚀刻时的副产物. 饨刻时起到对金属道线恻雅保护的作用).武卜兴是内匚金属电介房1MD (, kit er Metal

28、 Di dec tri。)建成首先沉积一层台RO在金属导线之上包含健壁),防止作为IMD的版化硅 戢璃FSG iMuoriiie Silicon CHass)宜接与肋面的金鸡导线接触而导致翘曲fxliag)的产生.由于氧化硅玻璃中的氟与金属层中的Ti反应,生成Ti取(氟 化软),该物质狎发性好,体机眼眠,会导致金属层LFSG膜粘合不牢,引起金 属层局FSG之问的翘曲,这会造成器件的可书件不良.在FG馍叼金属之间加 一层SRO材质的氧化膜便可解决这个问题.接着利用具有很好的阶梯覆盖能力的HDPFSG沉枳做同层金属连线之间的 隔离.然后淀积FSG火充当金属绝缘HIMD,它的引入带来了更低的介电常数

29、. 降低了金属5金属间的电容,减少了 RC延迟,从山提高器件的辽竹速度n 一般 氟含量控制在35原了百分比之间,氟含量太高的FSG膜非常不稳定,对水分 的抵挡能力很差容易因吸水而造成FSG 15J介电常数上升一K的介电常数而达 80!)叫然后进行金属绝税层的化学机械研磨,IMDCMP,目的是通过化学机械 钏磨将向面的IMD足回到软足R堆,血且使表面更加平粗,便于后续L艺的加 I,最后进仃W掺杂的红玻璃讥枳 USG(Un-iopecl SiliconGlffijs ) Depositioii 沉双层PECVD宣化FKm来防止下层领对后面余屈导戌的影响:以上的HDPFSG. PEFSG fll U

30、SG的阻合共I司形成了 MD1.1.1 同金属层之间中介孔的形成连接上下层金属导线的孔称之为中介和(VIA) . VIA1连接的就是金属1 (Metal 1J 与M属 Z (Mwl21 .以此类推&中介孔的形成流程与接用孔大致相同,所不同是,中介孔的蚀刻会停在前 层金属导城的TiNk,然后同样也会TT 一定量的TiN呼度损失.H的也是为广 保证连接的质量.图24。和图241为完成所有工艺的截面示意图及晶圆切片, 从中可以ft到VIA孔和下层之间的相互关系.图2-20 VIA1 CMP后截而不意图图2-21 VIA SEM切片图第一层中介孔的匚艺完成后,依次是第二层金属连线、第二层中介乱、第三 层金属连线等的制作.直到最后一层中介孔的完成一中同这些步为前面所述步骤 的重复,它们会随着实际金属导线层数的多少而增减,一般情况下内层金属连线 的层数为15层.2.3.4 J页部金属导线形成顶部全属层是最卜层的金属导线,它与之前的金属导线层在结构上有的点匕 要的差别,其一,厚度上需要较附层导线用(妁为前层的3倍),因为上层的导 线比较稀疏,所承受的电流比较大,到了下面的金属层电流由于分流作用会减小, 其:,三明治结构也仃所不同,上层和AlCu连接的用TiN取

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 励志诗歌合集

- 秘书年终工作总结

- 微软软件购买合同

- 学校供餐服务合同

- 2024年份2月份装修合同石膏板吊顶接缝处防开裂工艺

- 广告拍摄合同范本

- 山东省猪肉入市场厂挂钩合同

- 2025【英文合同】英文租赁合同范本

- 90代土地出让合同标准文本

- 增强财务创新能力的工作安排计划

- 2024版影视作品授权配音服务合同3篇

- 2024年北京大学强基计划物理试题(附答案)

- 《多变的镜头》课件 2024-2025学年人美版(2024)初中美术七年级上册

- Oracle数据库维保服务方案

- 2024智慧园区系统建设规范

- 传感器技术-武汉大学

- GB/T 44413-2024城市轨道交通分类

- PC信息系统运行维护服务方案

- 四川长虹电子控股集团有限公司招聘笔试题库2024

- 基于单元主题的小学英语跨学科学习活动的实践与研究

- 新生儿肺炎课件

评论

0/150

提交评论