版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

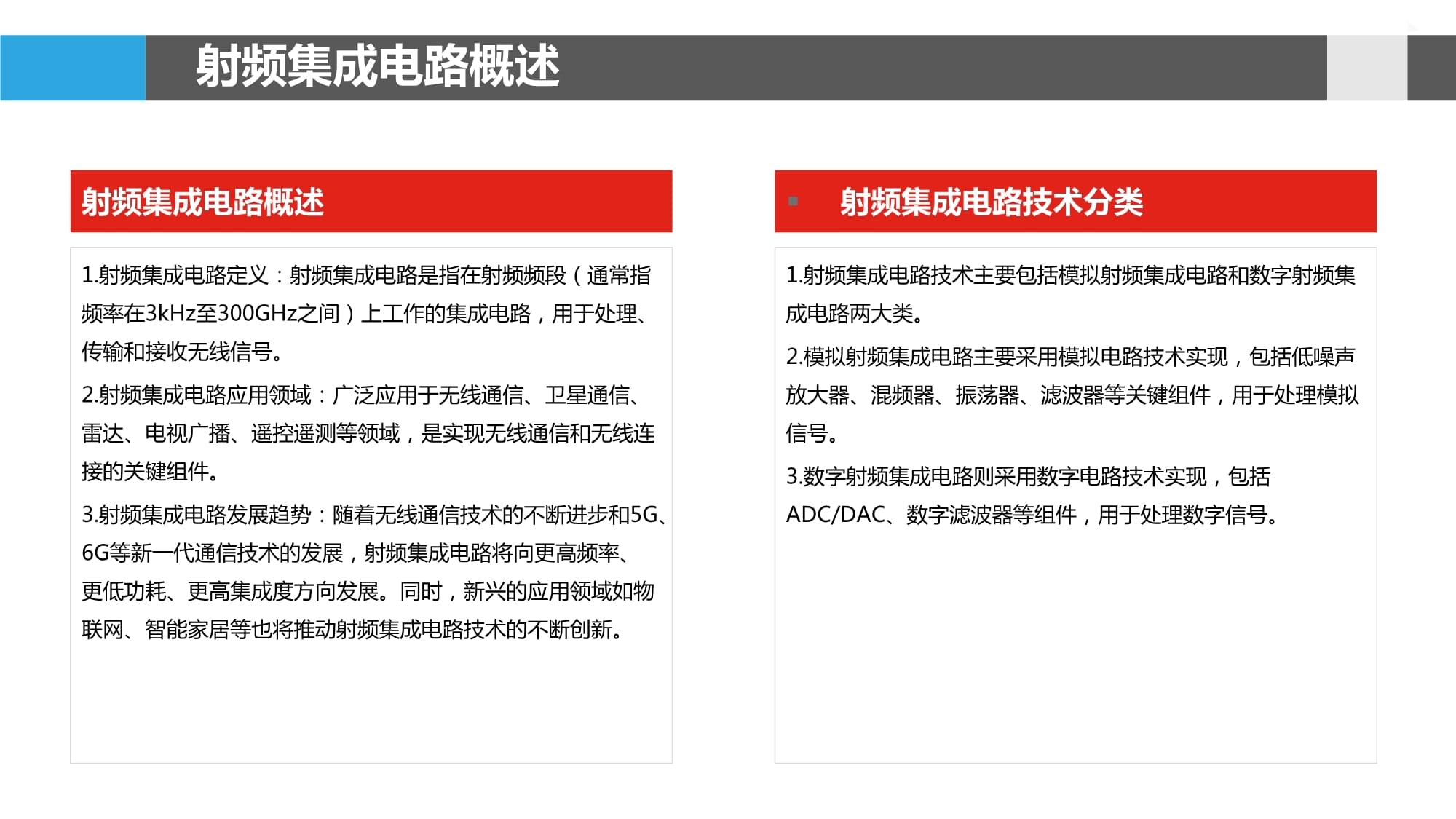

CMOS射频集成电路数智创新变革未来以下是一个《CMOS射频集成电路》PPT的8个提纲:射频集成电路概述CMOS射频电路基本原理射频电路关键性能指标CMOS射频电路设计技术射频收发器结构与系统射频电路版图设计与优化CMOS射频集成电路测试射频集成电路应用案例目录射频集成电路概述CMOS射频集成电路射频集成电路概述射频集成电路概述1.射频集成电路定义:射频集成电路是指在射频频段(通常指频率在3kHz至300GHz之间)上工作的集成电路,用于处理、传输和接收无线信号。2.射频集成电路应用领域:广泛应用于无线通信、卫星通信、雷达、电视广播、遥控遥测等领域,是实现无线通信和无线连接的关键组件。3.射频集成电路发展趋势:随着无线通信技术的不断进步和5G、6G等新一代通信技术的发展,射频集成电路将向更高频率、更低功耗、更高集成度方向发展。同时,新兴的应用领域如物联网、智能家居等也将推动射频集成电路技术的不断创新。射频集成电路技术分类1.射频集成电路技术主要包括模拟射频集成电路和数字射频集成电路两大类。2.模拟射频集成电路主要采用模拟电路技术实现,包括低噪声放大器、混频器、振荡器、滤波器等关键组件,用于处理模拟信号。3.数字射频集成电路则采用数字电路技术实现,包括ADC/DAC、数字滤波器等组件,用于处理数字信号。射频集成电路概述射频集成电路核心技术1.低噪声技术:射频集成电路需要具有极低的噪声水平,以保证接收到的信号质量。2.高线性度技术:线性度是衡量射频集成电路性能的重要指标,高线性度能够保证信号传输的准确性和稳定性。3.高集成度技术:随着系统集成度的不断提高,射频集成电路需要实现更高的集成度,以满足小型化和低功耗的需求。CMOS射频电路基本原理CMOS射频集成电路CMOS射频电路基本原理CMOS射频电路基本原理1.CMOS工艺优势:CMOS射频电路采用标准的CMOS工艺,具有成本低、集成度高、功耗低等优点,适用于大规模集成和商业化生产。2.射频信号特性:射频信号具有高频、高速、高功率等特点,需要特殊的电路设计和处理技术,以保证信号的完整性和稳定性。3.电路模型与仿真:CMOS射频电路需要建立准确的电路模型和进行充分的仿真测试,以确保电路的性能和可靠性。CMOS射频电路关键技术1.低噪声放大技术:CMOS射频电路需要具备低噪声放大技术,以提高接收机的灵敏度和抗干扰能力。2.混频技术:混频技术是实现频率转换的关键技术,需要保证转换效率和线性度。3.滤波技术:滤波技术是滤除无用信号和干扰的关键技术,需要提高滤波器的性能和稳定性。CMOS射频电路基本原理CMOS射频电路发展趋势1.集成化:随着工艺技术的不断进步,CMOS射频电路的集成化程度会不断提高,实现更加小型化和高效化的电路设计。2.毫米波技术:毫米波技术将成为未来CMOS射频电路的重要发展方向,能够实现更高的数据传输速率和更精细的分辨率。3.智能化:随着人工智能和物联网技术的不断发展,CMOS射频电路的智能化程度会不断提高,实现更加智能化和自适应的电路设计。射频电路关键性能指标CMOS射频集成电路射频电路关键性能指标噪声系数(NoiseFigure)1.噪声系数是衡量射频电路性能的重要指标,它代表了电路引入的额外噪声量。2.噪声系数越低,表示电路的噪声性能越好,对提高系统的信噪比有利。3.优化射频电路的设计,降低噪声系数,可以提高接收机的灵敏度和通信质量。增益(Gain)1.增益是射频电路的重要性能指标,表示电路对信号的放大能力。2.高增益可以提高输出信号的幅度,但同时可能引入更多的噪声和非线性失真。3.在设计时需权衡增益和其他性能指标的关系,以实现最佳的系统性能。射频电路关键性能指标线性度(Linearity)1.线性度是衡量射频电路对输入信号进行线性放大的能力。2.良好的线性度可以避免信号失真和交调产物,提高通信系统的可靠性。3.通过采用线性化技术和优化电路设计,可以改善射频电路的线性度性能。匹配性(Matching)1.匹配性是指射频电路输入输出端口与传输线的匹配程度。2.良好的匹配可以减少反射和损耗,提高能量的传输效率。3.在设计过程中,需根据实际应用场景选择合适的匹配网络和优化方法。射频电路关键性能指标1.稳定性是射频电路正常工作的重要前提,表示电路在各种工作条件下保持稳定的能力。2.不稳定的电路可能导致振荡和自激等现象,影响系统的正常工作。3.在设计过程中,需要进行稳定性分析和采取措施保证电路的稳定工作。功耗(PowerConsumption)1.功耗是射频电路的一个重要指标,尤其在移动和便携式设备中更为关键。2.降低功耗可以提高设备的续航能力,减少热量产生,有利于设备的小型化和便携化。3.通过采用低功耗设计技术和优化电源管理,可以降低射频电路的功耗。稳定性(Stability)CMOS射频电路设计技术CMOS射频集成电路CMOS射频电路设计技术CMOS射频电路设计技术概述1.CMOS射频集成电路的重要性及应用领域。2.CMOS射频电路设计技术的发展趋势及前沿技术。3.CMOS射频电路的基本构成及工作原理。CMOS射频集成电路是一种利用CMOS工艺制造的用于处理射频信号的集成电路。随着无线通信技术的飞速发展,CMOS射频集成电路已成为现代通信系统的重要组成部分。由于其具有低功耗、高集成度等优势,被广泛应用于手机、卫星通信、雷达等领域。CMOS射频电路设计技术的发展趋势主要包括更高的工作频率、更低的功耗、更高的集成度等。同时,新兴技术如人工智能、5G等也将对CMOS射频电路设计技术产生重要影响。CMOS射频电路的关键技术1.噪声分析与优化技术。2.匹配网络设计技术。3.线性度提升技术。在CMOS射频电路设计中,噪声、匹配网络和线性度是影响电路性能的关键因素。因此,噪声分析与优化技术、匹配网络设计技术和线性度提升技术是CMOS射频电路的关键技术。这些技术的发展对于提高CMOS射频电路的性能具有重要意义。CMOS射频电路设计技术CMOS射频电路的设计方法1.拓扑结构设计。2.版图优化技术。3.寄生参数提取与建模技术。CMOS射频电路的设计方法主要包括拓扑结构设计、版图优化技术和寄生参数提取与建模技术。拓扑结构设计是电路设计的核心,它决定了电路的功能和性能。版图优化技术则是将电路拓扑结构转化为可制造的版图的关键技术。寄生参数提取与建模技术则是用于分析和优化版图中的寄生参数,以提高电路性能。CMOS射频电路的测试与调试1.测试方案设计。2.测试数据分析与处理。3.调试与优化技术。为了确保CMOS射频电路的性能和可靠性,需要进行严格的测试和调试。测试方案设计需要考虑电路的特点和应用场景,以确保测试的准确性和有效性。测试数据分析与处理则需要运用专业的数据处理和分析方法,以提取有用的信息用于调试和优化电路。调试与优化技术则是根据测试结果对电路进行优化,以提高电路的性能和可靠性。CMOS射频电路设计技术CMOS射频电路的应用案例1.在5G通信系统中的应用。2.在物联网中的应用。3.在雷达和卫星通信中的应用。CMOS射频电路在5G通信系统、物联网、雷达和卫星通信等领域有着广泛的应用。在这些应用中,CMOS射频电路发挥着关键作用,为系统的正常运行提供了重要的支持。同时,这些应用案例也展示了CMOS射频电路的广阔应用前景和发展潜力。CMOS射频电路的发展展望1.新技术的发展与应用。2.绿色环保和可持续发展。3.产业链协同与创新。随着新技术的不断发展,CMOS射频电路将有更多的发展机遇和挑战。未来,CMOS射频电路将更加注重绿色环保和可持续发展,推动产业链的协同和创新。同时,新技术的发展也将为CMOS射频电路带来更多的可能性,为未来的无线通信系统提供更加高效、可靠的支持。射频收发器结构与系统CMOS射频集成电路射频收发器结构与系统射频收发器的基本结构1.射频收发器的主要功能是在射频频段上进行信号的接收和发送。2.收发器结构通常包括天线、低噪声放大器、混频器、中频放大器、解调器等部分。3.收发器的设计需考虑到噪声、干扰、失真等因素,以提高接收和发送信号的质量。射频收发器的系统架构1.射频收发器的系统架构通常采用超外差结构或零中频结构。2.超外差结构具有较好的抗干扰能力和接收灵敏度,而零中频结构具有较低的功耗和简化的设计。3.选择合适的系统架构需根据具体应用场景和需求进行权衡。射频收发器结构与系统射频收发器中的关键技术1.射频收发器中需要用到许多关键技术,如低噪声放大技术、混频技术、滤波技术等。2.这些技术的性能直接影响到收发器的性能,因此需要进行深入研究和优化。3.随着工艺和技术的不断进步,射频收发器的性能也在不断提高。射频收发器的应用场景1.射频收发器广泛应用于无线通信、雷达、卫星通信等领域。2.在不同的应用场景下,收发器的设计需求也会有所不同,需要根据具体需求进行优化设计。3.随着物联网、5G等技术的快速发展,射频收发器的应用场景也在不断扩展。射频收发器结构与系统1.随着工艺和技术的不断进步,射频收发器正朝着小型化、低功耗、高性能的方向发展。2.同时,集成化和多功能化也成为收发器发展的重要趋势。3.未来,随着新技术的应用,射频收发器的性能和功能将得到进一步提升。射频收发器的挑战与机遇1.射频收发器的发展面临着许多挑战,如噪声、干扰、功耗等问题。2.同时,随着新技术的不断涌现,射频收发器也面临着新的机遇和挑战。3.未来,需要继续加强研究和创新,提高收发器的性能和可靠性,以满足不断增长的应用需求。射频收发器的发展趋势射频电路版图设计与优化CMOS射频集成电路射频电路版图设计与优化射频电路版图设计基础1.版图设计需要考虑电磁波传播、干扰和噪声等因素。2.合理布局元器件,减少不必要的电磁干扰。3.利用电磁仿真软件进行版图优化,提高电路性能。版图布局优化1.元器件布局应考虑信号流向,减少交叉干扰。2.充分利用版图空间,提高集成度。3.布局优化需要考虑电路性能和可靠性。射频电路版图设计与优化射频电路布线优化1.布线长度和宽度需要满足电磁波传播要求。2.考虑布线阻抗匹配,提高信号传输效率。3.利用布线层次和过孔进行优化,减少干扰。版图寄生参数优化1.减小寄生电容和电感对电路性能的影响。2.利用版图对称性进行优化。3.考虑版图地线的布局和优化。射频电路版图设计与优化版图可靠性设计1.考虑版图耐热性、耐电压性和耐腐蚀性等因素。2.对关键元器件进行加固和保护。3.通过版图设计提高电路的抗干扰能力。前沿技术和趋势1.随着工艺技术的进步,射频电路版图设计将更加精细和复杂。2.人工智能和机器学习在射频电路版图优化中的应用将逐渐普及。3.可持续发展和绿色环保将成为射频电路版图设计的重要考虑因素。CMOS射频集成电路测试CMOS射频集成电路CMOS射频集成电路测试1.测试目的:确保CMOS射频集成电路的性能和功能符合设计要求。2.测试方法:基于晶圆测试、最终测试等不同阶段采用不同的测试方法。3.测试重要性:提高产品质量、可靠性和竞争力。测试环境设置1.屏蔽环境:减少外部干扰,提高测试准确性。2.温度控制:确保测试环境温度稳定,模拟实际工作条件。3.测试设备校准:定期校准测试设备,确保测试数据准确性。CMOS射频集成电路测试概述CMOS射频集成电路测试直流特性测试1.电流电压测试:测量集成电路的电流电压特性,确保其正常工作。2.功耗测试:测量集成电路功耗,评估其能效。3.阈值电压测试:测量晶体管的阈值电压,评估其性能。交流特性测试1.频率响应测试:测量集成电路在不同频率下的响应,评估其频率特性。2.噪声测试:测量集成电路的噪声水平,评估其信噪比。3.线性度测试:测量集成电路的线性度,评估其失真性能。CMOS射频集成电路测试可靠性测试1.温度循环测试:模拟温度变化,评估集成电路的可靠性。2.高温工作寿命测试:在高温条件下长时间工作,评估集成电路的寿命。3.机械应力测试:模拟机械应力,评估集成电路的抗机械损伤能力。自动化测试与数据分析1.自动化测试:提高测试效率,降低人工成本。2.数据分析与处理:对测试数据进行深入分析,提取有用信息。3.测试优化:根据数据分析结果优化测试方案,提高测试准确性和效率。射频集成电路应用案例CMOS射频集成电路射频集成电路应用案例移动通信1.CMOS射频集成电路在移动通信领域广泛应用,包括手机、基站等设备。随着5G、6G等通信技术的发展,对射频集成电路的性能要求不断提高。2.高性能CMOS工艺不断提升,使得射频集成电路能够实现更高的工作频率、更低的功耗和更小的体积,满足移动通信设备的需求。3.未来趋势是继续提高射频集成电路的集成度和性能,同时降低成本,以适应更广泛的移动通信应用场景。物联网1.物联网技术需要大量连接设备,而射频集成电路是实现设备间无线通信的关键组件。2.射频集成电路需要满足低功耗、长距离、抗

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 驾驶员体检报销流程

- 2024年特许金融分析师考试财务分析题试题及答案

- 第八章 作业38 功能关系及其应用-2025版高一物理必修二

- 陕西省西安市长安区2024-2025学年高三上学期一模语文试题

- 老年人口腔保健知识宣教

- 地产广告画面规范

- 卷1-2025年中考地理高频考题(广东专用)(解析版)

- 2025年广东省初中学业水平考试仿真卷(三)(解析版)

- 目标明确的2024年特许金融分析师考试试题及答案

- 法律环境对投资的影响试题及答案

- 可信数据空间建设及应用参考指南1.0

- 酸及其性质(第一课时)课件九年级化学(2024)下册

- 《高速公路服务区开放设置技术要求》

- 新思想引领新征程新青年建功新时代-(第二版)

- 【MOOC】中国传统艺术-篆刻、书法、水墨画体验与欣赏-哈尔滨工业大学 中国大学慕课MOOC答案

- 【MOOC】游戏引擎原理及应用-中国传媒大学 中国大学慕课MOOC答案

- 2024年江西省公务员录用考试《行测》真题及答案解析

- 国家安全教育高教-第六章坚持以经济安全为基础

- 提取句子主干和划分句子成分专项练习

- 信息检索与利用课件 第7章 网络信息检索(上)

- 2025新译林版英语七年级下单词默写表

评论

0/150

提交评论