版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

第二章

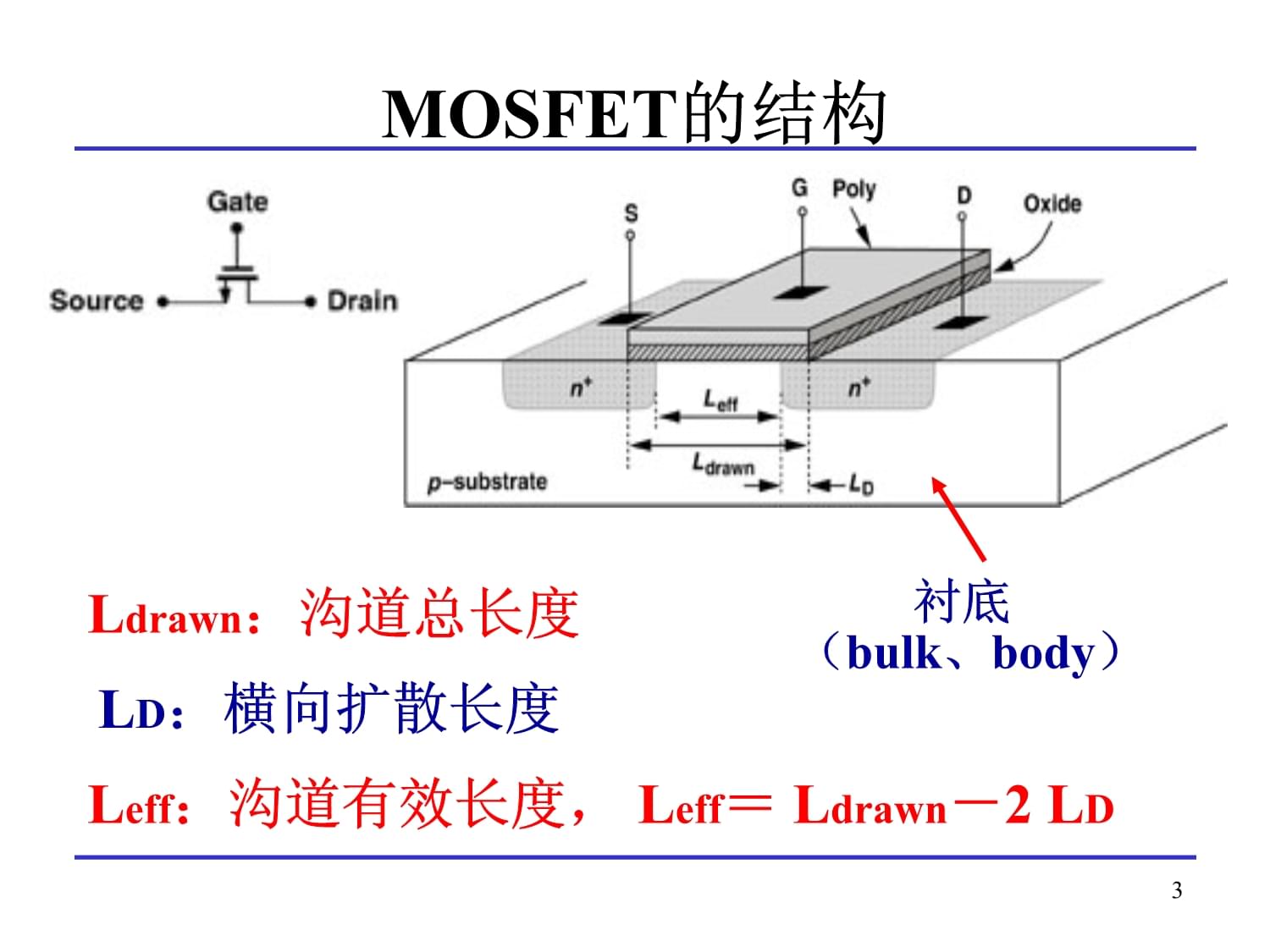

MOS器件物理基础1MOSFET的结构2衬底Ldrawn:沟道总长度Leff:沟道有效长度,Leff=Ldrawn-2LDMOSFET的结构LD:横向扩散长度(bulk、body)3MOS管正常工作的基本条件MOS管正常工作的基本条件是:所有衬源(B、S)、衬漏(B、D)pn结必须反偏!寄生二极管4同一衬底上的NMOS和PMOS器件寄生二极管*N-SUB必须接最高电位VDD!*P-SUB必须接最低电位VSS!*阱中MOSFET衬底常接源极SMOS管所有pn结必须反偏:5例:判断制造下列电路的衬底类型6NMOS器件的阈值电压VTH(a)栅压控制的MOSFET(b)耗尽区的形成(c)反型的开始(d)反型层的形成7以NMOS为例:D和S接地①VG<0,空穴在硅表面积积累②0<VG<VTH硅表面耗尽:表面只有固定的负电荷③VG>VTH

硅表面反型:自由电子吸引到硅表面强反型条件:

栅极下硅表面反型层的载流子浓度=

衬底掺杂浓度8这里是多晶硅栅和硅衬底的函数,=,Nsub是衬底的掺杂浓度,Qdep是耗尽层的电荷,Cox是单位面积的栅极电容。由pn结的原理,,这里εsi是硅的介电常数。因为Cox经常出现在器件的计算公式中,一般认为tox=50A,Cox=6.9fF/,Cox的值可以来估其他厚度的氧化层面积。=为体效应系数,为源-体之间的电势差9NMOS管VGS>VT、VDS=0时的示意图10NMOS管VGS>VT、0<VDS<VGS-VT时的示意图沟道夹断条件Vds≥Vgs-Vth11NMOS沟道电势示意图(0<VDS<VGS-VT)边界条件:V(x)|x=0=0,V(x)|x=L=VDS12Qd:沟道电荷密度Cox:单位面积栅电容沟道单位长度电荷(C/m)WCox:MOSFET单位长度的总电容Qd(x):沿沟道点x处的电荷密度V(x):沟道x点处的电势I/V特性的推导(1)电荷移动速度(m/s)V(x)|x=0=0,V(x)|x=L=VDS13I/V特性的推导(2)对于半导体:且14三极管区的MOSFET(0<VDS<

VGS-VT)等效为一个压控电阻15I/V特性的推导(3)三极管区(线性区)每条曲线在VDS=VGS-VTH时取最大值,且大小为:VDS=VGS-VTH时沟道刚好被夹断16饱和区的MOSFET(VDS≥

VGS-VT)当V(x)接近VGS-VT,Qd(x)接近于0,即反型层将在X≤L处终止,沟道被夹断。17NMOS管VGS>VT、VDS>VGS-VT时的示意图电子耗尽区18NMOS管的电流公式截至区,Vgs<VTH线性区,Vgs

>VTHVDS<Vgs

-VTH饱和区,Vgs

>VTHVDS>Vgs

-VTH19MOSFET的I/V特性TriodeRegionVDS>VGS-VT沟道电阻随VDS增加而增加导致曲线弯曲曲线开始斜率正比于VGS-VTVDS<VGS-VT用作恒流源条件:工作在饱和区且VGS=const!20例2.1:在图2.14a中,表示M1是受VG控制的电阻。假设Cox=50uA/V,W/L=10,VTH=0.7V。漏端开路解:因为漏端开路,ID=0,VDS=0。因此,假如器件导通,它就工作在深线性区。如果VG<1V+VTH,M1截止,Ron=无穷大。如果VG>1V+VTH我们有21MOSFET的跨导gm22例2.2:如图2.19,画出跨导与的函数曲线当从无穷大减小到零时来研究的变化,会使这个问题变的简单。只要,晶体管就工作在饱和区,和就保持相对恒定,这可从式得到。当它工作在线性区时,此时有=因此,如图2.19曲线所示,一旦器件进入线性区,跨导将下降。因此,在放大应用时,我们通常使MOSFET工作在饱和区23MOS管饱和的判断条件NMOS饱和条件:Vgs>VTN;Vds≥Vgs-VTHNPMOS饱和条件:Vgs<VTP;Vds≤Vgs-VTP

gdgd判断MOS管是否工作在饱和区时,不必考虑Vs24MOS模拟开关MOS管为什么可用作模拟开关?MOS管D、S可互换,电流可以双向流动。可通过栅源电源(Vgs)方便控制MOS管的导通与关断。关断后Id≈025NMOS模拟开关传送高电平的阈值损失特性假定“1”电平为3V,“0”电平为0V,VTN=0.5V,试确定C1、C2的终值电压。26PMOS模拟开关传送低电平的阈值损失特性假定“1”电平为3V,“0”电平为0V,VTP=-0.5V,试确定C1、C2的终值电压。27MOS管的开启电压VT及体效应ΦMS:多晶硅栅与硅衬底功函数之差Qdep耗尽区的电荷,是衬源电压VBS的函数Cox:单位面积栅氧化层电容28MOS管的开启电压VT及体效应无体效应源极跟随器

有体效应体效应系数,VBS=0时,=0一般,体效应使设计复杂化29MOS管体效应的Pspice仿真结果Vb=0.5vVb=0vVb=-0.5vIdVg体效应的应用:利用衬底作为MOS管的第3个输入端利用VT减小用于低压电源电路设计30衬底跨导gmb31例2.3在图2.23(a)图中。假设,,。如果从到0变化,画出漏电流的曲线解:如果足够负,的阈值电压将超过1.2V,器件处于关断,即1.2v=0.6+0.4

解得:又由下式可知,当时,增加,如图b所示32MOSFET的沟道调制效应33MOSFET的沟道调制效应LL’34MOS管沟道调制效应的Pspice仿真结果VGS-VT=0.15V,W=100µ∂ID/∂VDS∝λ/L∝1/L2L=2µL=6µL=4µ35MOS管跨导gm不同表示法比较跨导gm123上式中:36亚阈值导电性当下降到低于时管子会突然关断。事实上,时,一个弱的反型层仍然存在,还是有电流从D流向S。甚至当,也并非无限小,而是与成指数关系。这种效应称为“亚阈值导电”

图2.27MOS亚阈值导特性对于的典型值,在室温下,要使下降一个数量级,必须下降约80mV。产生漏电,对静态功耗、动态电路不利。37亚阈值导电特性(ζ>1,是一个非理想因子)38MOS管亚阈值导电特性的Pspice仿真结果VgSlogID仿真条件:VT=0.6VW/L=100µ/2µMOS管亚阈值电流ID一般为几十~几百nA,常用于低功耗放大器、带隙基准设计。39MOS器件版图40MOS器件电容在许多模拟电路中,器件电容也必须加以考虑以便预测其交流特性。我们认为电容存在于MOSFET的四个端子中任意两个之间。(1)基本的覆盖电容(线性的)(2)沟道电容(非线性的,值与晶体管的工作区域有关。(3)结电容,也是非线性的。41TheGateCapacitancetoxn+n+CrosssectionLGateoxidexdxdLdPolysilicon

gateTopviewGate-bulkoverlapSourcen+Drainn+W42GateCapacitanceCut-offResistiveSaturationMostimportantregionsindigitaldesign:saturationandcut-off43GateCapacitanceCapacitanceasafunctionofVGS(withVDS=0)Capacitanceasafunctionofthe

degreeofsaturation44MeasuringtheGateCap45DiffusionCapacitanceBottomSidewallSidewallChannelSourceNDChannel-stopimplant

NA1SubstrateNAWxjLS46JunctionCapacitance47LinearizingtheJunctionCapacitanceReplacenon-linearcapacitancebylarge-signalequivalentlinearcapacitancewhichdisplacesequalchargeovervoltageswingofinterest48Capacitancesin0.25mmCMOSprocess49MOS电容电容存在于MOS管的任意二极点之间电容可分为:①栅-沟道电容:②栅-源漏交叠电容:==是单位长度电容③沟道-衬底耗尽层电容:④结电容:C5,C6底板电容Cj0、侧壁电容Cjsw50不同工作区的MOS电容①关断:②线性区:③饱和区:SDGB如果栅压发生变化,电荷是由源和漏提供,而不是由衬底提供。P27最后一段51栅源、栅漏电容随VGS的变化曲线C3=C4=COVWCov:每单位宽度的交叠电容MOS管关断时:CGD=CGS=CovW,CGB=C1//C2C1=WLCoxMOS管深线性区时:CGD=CGS=C1/2+CovW,CGB=0,C2被沟道屏蔽MOS管饱和时:CGS=2C1/3+CovW

,蔼CGD=CovW,CGB=0,C2被沟道屏蔽52MOS电容器的结构。53MOS器件电容54减小MOS器件电容的版图结构对于图a:CDB=CSB=WECj

+2(W+E)Cjsw对于图b:CDB=(W/2)ECj+2((W/2)+E)CjswCSB=2((W/2)ECj+2((W/2)+E)Cjsw=WECj

+2(W+2E)Cjsw55栅极电阻56MOS小信号模型漏电流公式和与电压有关的电容构成了MOS的大信号模型。当信号显著影响偏置工作点时,应考虑非线性效应。若信号对偏置影响小时,则可以用小信号模型简化计算。小信号模型是工作点附近的大信号模型的近似由于模拟电路中MOS偏置在饱和区,可以导出其相应的小信号模型。57(1)由于漏电流是栅-源电压的函数,因此我们可以引入一个值为gmVGS的压控电流源。(a)(2)由于沟长调制,漏电流也随着漏-源电压变化。这一效应也可用一个压控电流源模拟。但是,如果一个电流源的电流值与它两端的电压成线性关系,则该电流源等效于一个线性阻抗。(b)(c)58连接于D和S之间的输出电阻可由下式得到:输出电阻ro影响模拟电路的许多特性。例如,它限定着大多数放大器的最大电压增益。59(3)衬底电势影响阈值电压,因而也影响栅-源过驱动电压,在所有其他端子保持恒定电压的情况下,漏电流是衬底电压的函数。也就是说,衬底相当于另一个栅。用连接于B和S之间的电流源模拟这一关系,其电流值为gmbVbs,其中gmb=60在饱和区:因此我们又有gmbVBS和gmVGS有相同的极性,也就是说,增大栅电压与增大衬底电压效果相同。61完整的MOS小信号模型也包括器件电容MOS小信号模型中的电容图2.38完整的MOS小信号模型62例:求下列电路的低频小信号输出电阻(γ=0)63例:求下列电路的低频小信号输出电阻(γ=0)64例:求下列电路的低频小信号输出电阻(γ=0)65小信号电阻总结(γ=0)对于图(A):对于图(B):对于图(C):66NMOS器件的电容--电压特性积累区强反型67例:若W/L=50/0.5,|ID|=500uA,分别求:

NMOS、PMOS的跨导及输出阻抗以及本征增益gmr0

(tox=9e-9λn

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2026届浙江省杭州市示范名校生物高一下期末考试试题含解析

- 2026届河南省联盟高一数学第二学期期末经典模拟试题含解析

- 2025年阿里巴巴审核员面试题库及答案

- 2025年国企干部笔试题目及答案

- 2025年欧莱雅代言人面试题库及答案

- 2025年恩捷维修技术员面试题库及答案

- 2025年信阳光山县事业编考试及答案

- 2025年饶阳县幼儿园教师招教考试备考题库含答案解析(必刷)

- 2025年上海政法学院马克思主义基本原理概论期末考试模拟题附答案解析(必刷)

- 2025年怀化师范高等专科学校单招职业适应性测试题库带答案解析

- 2026年及未来5年市场数据中国机械式停车设备行业市场全景分析及投资战略规划报告

- 泥浆压滤施工方案(3篇)

- 李时珍存世墨迹初探──《李濒湖抄医书》的考察

- 肺源性心脏病诊疗指南(2025年版)

- 医院行风建设培训会课件

- 非药品类易制毒化学品经营企业年度自查细则

- 太阳能建筑一体化原理与应 课件 第5章 太阳能集热器

- 住院患者节前安全宣教

- 2026春人教版英语八下单词表(先鸟版)

- 汽车装潢贴膜合同范本

- 签字版离婚协议书范本

评论

0/150

提交评论