版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、FTU硬件详细设计说明书产品线:配电终端产品类别:产品型号:产品版本:文件状态文档版本作者完成日期编制部门硬件开发部批准:审核:初审:编写:1.引言1.1.前言1.2.文档术语1.3.参考文档2开发环境入硬件详细设计系统架构主板板硬件框图模块2:时钟模块错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签模块1:CPU亥心板错误!未指定书签。模块3:无线通讯错误!未指定书签模块6以太网接口错误!未指定书签RS232/RS48加路错误!未指定书签SD#模块电路错误!未指定书签直流量采集模块

2、错误!未指定书签USBHOST口错误!未指定书签遥控遥信板错误!未指定书签硬件框图错误!未指定书签遥信电路模块错误!未指定书签遥控电路模块错误!未指定书签遥测板错误!未指定书签遥测板框图错误!未指定书签谣测电路模块错误!未指定书签电源模块错误!未指定书签错误!未指定书签亓器件总成本:错误!未指定书签硬件测试方法错误!未指定书签LFPGAM辑I计错误!未指定书签1.1.子板逻辑错误!未指定书签架构概述错误!未指定书签1.2.主板逻辑错误!未指定书签外观设计外形结构铭牌终端内部结构组屏方案其他错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签错误!未指定书签错误!未指

3、定书签1.引言前言文档术语参考文档4.%2.%3.%4.开发环境硬件设施:普通个人PC软件:protel99seCadence16.35.%2.%3.%4.硬件详细设计5.系统架构5.主板5.4.主板硬件框图5.4.CPU核心板5.4.5.功能:保存各种数据,参数设置等其他需要保存的数据及给各功能模块提供逻辑接5.4.5.接口描述:32位RISC嵌入式ARM9+DS内核CPUOMAPL138ZW!过内置DDR2/mDDR制器接口外扩1片32M/16位或64M/16位DDR2SDRAMMT47H32M16HR/MT47H64M1;6HR通过内置外部存储器接口(EMIFA)外扩1片128MByte

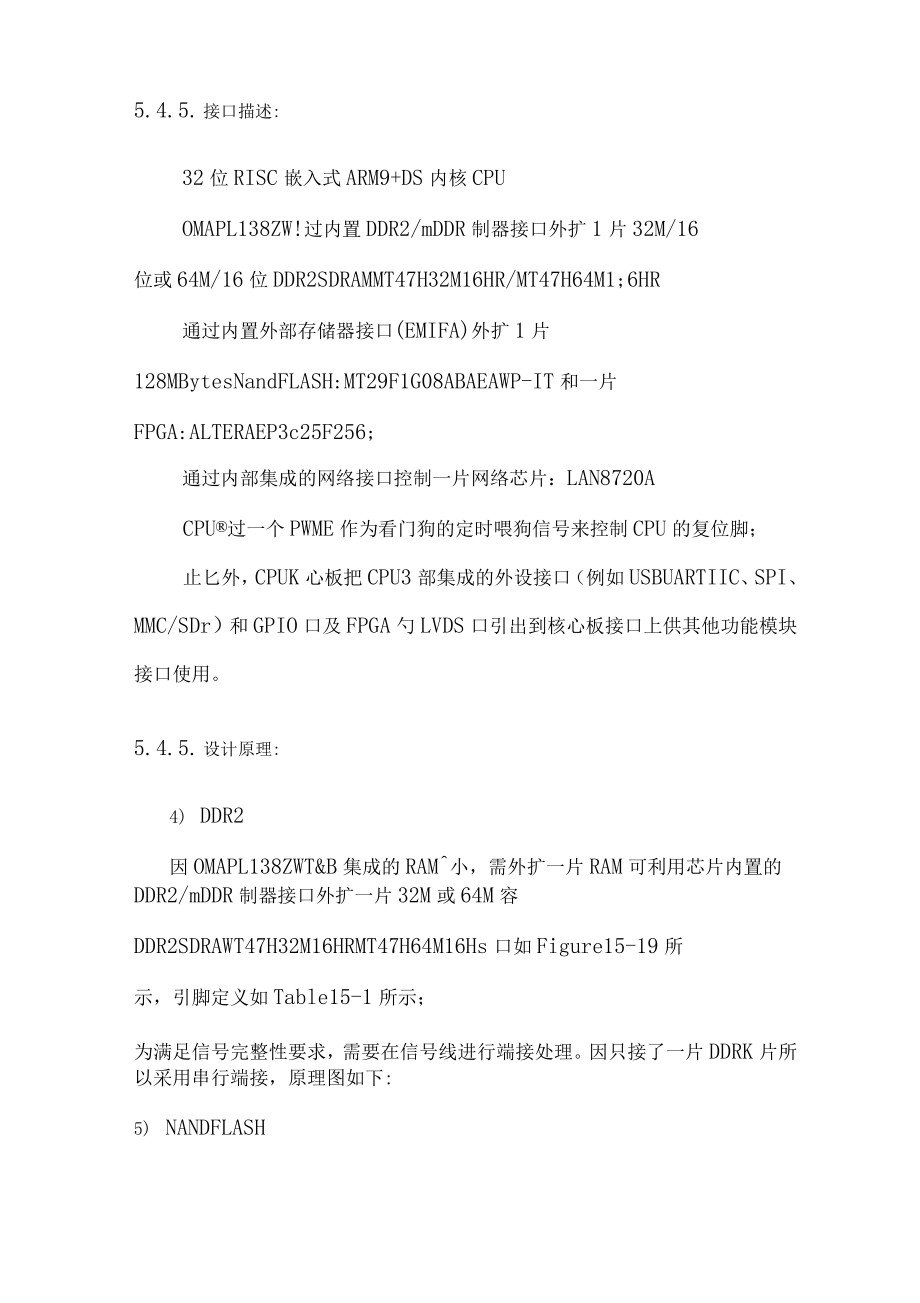

4、sNandFLASH:MT29F1G08ABAEAWP-IT和一片FPGA:ALTERAEP3c25F256;通过内部集成的网络接口控制一片网络芯片:LAN8720ACPU过一个PWME作为看门狗的定时喂狗信号来控制CPU的复位脚;止匕外,CPUK心板把CPU3部集成的外设接口 (例如USBUARTIIC、SPI、MMC/SDr)和GPIO口及FPGA勺LVDS口引出到核心板接口上供其他功能模块接口使用。5.4.5.设计原理:4)DDR2因OMAPL138ZWT&B集成的RAM小,需外扩一片RAM可利用芯片内置的DDR2/mDDR制器接口外扩一片32M或64M容DDR2SDRAWT47

5、H32M16HRMT47H64M16Hs口如Figure15-19所示,引脚定义如Table15-1所示;为满足信号完整性要求,需要在信号线进行端接处理。因只接了一片DDRK片所以采用串行端接,原理图如下:5)NANDFLASH因OMAPL138ZWT&B集成的RO就小,需外扩一片NANDFLASH可利用芯片内置的EMIFAg口外扩一片1Gb或2G喀量的NANDFLASHMT29F1G08ABAEAWP-TMT29F2G08ABAEAWP-IT卜部存储器接口如Figure20-1所示,弓|脚定义如Table20-1、Table20-2、Table20-3所示;外扩NANDFLASHFi

6、gure20-14所示为了减少R/B#脚的延时时间,R/B#脚上接1K的上拉电阻。原理图如6)FPGA因FTU需要采集的交流信号及遥信信号和控制的遥控信号众多,可利用EMIFA接口接一片FPGAS行预处理。核心板上的FPGAf功能板上的FPGA1过LVDS进行点对点通讯, 将得到数据存放在各功能板相对应的存储区里供CPU卖取。 从而提高系统的实时性和简化电路设计。 将FPGA乍为SRAM?储器挂在CPU勺EMIFA口上,其接口示意图如Figure20-18的红圈部分所示;Figure20-10ExampleConfigurationInterfflteFigure20-10ExampleCon

7、figurationInterfflteLVDS口需外加端接电阻,参数见FPG徽据手册,其原理图如下。注:因所用FPGAK片的真实的LVDS口不足,需使用一路仿真LVDS口。其端接电阻与真实的LVDSg口的不同。4)以太网EMIEMIPAEMA_C5tPEMA_C5tPMAQASEVIMAQASEVIA A而EMA_GLEMASDCKEMA_GLEMASDCKE EEUA_iAiE_OCM-|EUA_iAiE_OCM-|三应口【1515刈EWA_EWA_;YAITYAITCECEQASQAS/.fECLCLKCKEBA1KCKEBA1SAUSAUAT1LOJKlMUDJKlMUDQMDQQMD

8、Q:15.0|15.0|SDRAMiMxSDRAMiMx10 x4tiii10 x4tiiinknkTC5S15100FT-115100FT-1以太网芯片采用RMII接口的LAN8720ACPU过内部集成的EMAC(RMII)和MDIO与LAN8720Al连,来建立以太网的物理层连接,其接口下意图如Figure19-3所示,引脚定义如Table19-2所示外围电路见数据手册,其原理图如下:5)看门狗看门狗电路选用的是Sipex公司的SP706REN-L复位周期1.6S,持续时间200ms采用软硬件控制,软件方式:CPU过才$制PWMC的输出来控制看门狗电路;硬件方式:通过按键控制/MR的电平来

9、控制看门狗电路,原理图如下:6)供电电路为了防止输入电压过高保护后级的电源管理芯片,在+5V电源输入端加一保护电路,当输入高于5.8V是输出关断,外加一个LED用以指示。当5V_IN5.8V时,LED亮。8)CPU)!庙:CPUft电为一多电源供电系统,其供电电流和上电顺序要求如下:电源管理芯片采用TI公司的TPS650250RHBR过控制DC-DC使能端来控制各电平的上电顺序。外围电路参数见数据手册。原理图如下:上电顺序逻辑电路如下,上电逻辑,+5V输入时_DCDC拉高-VDCDC3输出VCC_1V3D拉高EN_DCDC2VDCDC输出VCC_1V8D拉高EN_DCDC1VDCDC1出VCC

10、_3V3D.9)FPG缺电FPGA隹荐供电电源参数如下表:VCCIO采用两种电平供电, 为LVDS口供电的Bank1,2,3,5,6采用2.5V供电;其他Bank采用3.3V供电。电源芯片使用AS1301内核供电LVDS总线供电可靠性设计(性能,EMC):a)静电防护:无b)快速脉冲群防护:无c)浪涌防护:无成本估计:约380元时钟模块功能:为系统提供实时时钟。断电情况下该时钟能保持3年以上。接口描述:时钟芯片通过SPI总线与CPU相连。设计原理:断电时钟保持时间T=1200mAh*30%/(550nA)=654545小时=74年注:假设电池容量下降到70%寸时钟芯片不能正常工作,1200mA

11、h为电池容量。系统上电时,(3.3-0.6)(3.6-0.6-0.6),VCC_3.3V给时钟芯片供电,仅当系统失电时3.6V电池才会给时钟芯片供电,D3为了防止3.6V给3.3V系统供电。可靠性设计本部分在公司以往各产品中使用效果良好,时钟精确度高。成本估计10元无线通讯功能1、GPRS/CDMA通讯:在终端与主站之间通过公网或者专网建立无线通讯,进行数据交换;2、GPS通讯:通过GPS进行终端定位;3、短距离无线通讯:本地调试用。接口描述1、GPRS/CDMA模块:CPU通过UART与GPRS/CDMA模块进行数据通讯, 通过4个GPIO控制GPRS/CDMA模块的运行及网络灯指示。2、G

12、PS通讯模块接口:因主CPU串口有限 (只有3路,2路用作232/485通讯、 剩下1路用作GPRS/CDMA通讯) ,故用软串口与GPS模块进行通讯,外加两个GPIO控制GPS模块的复位及唤醒。下图为软串口框图。3、短距离无线通讯:因主CPU串口有限 (只有3路,2路用作232/485通讯、 剩下1路用作GPRS/CDMA通讯) ,故用软串口与短距离无线模块进行通讯, 外加两个GPIO控制短距离无线模块的复位及睡眠。原理硬件采用插板结构,与主板分离,保持主板不动更换不同通讯模块,支持cdma,gprs通信模块。各模块对主板的接口统一定义。由于该模块I/O口允许的输入最大电压是VEXT即2.9

13、3V,所以输入信号需添加分压电路,这样输入信号大概被调整至2.7V附近,保证正常工作,另外,电阻R725按照数据手册看,由于该引脚内部已经上拉,所以该电阻可以省略,而且最好不要焊接,因为该脚允许的外接电压最大为VDDEXT但以往产品设计的时候,都加了该电阻,尚未发现问题。模块原理图电平转换电路Sim卡接口需要注意的是,图中D1D4四个静电防护器必须添加,替代以往该处使用的是集成TVS芯片UCLAMP0504,节约成本。2、GPS模块:GPSS块选用SKG16A通过CPU勺软用口将GPS&息传输给CPU外加收发指示灯便于观察与调试。3、短距离无线模块:短距离无线通讯采用上海桑锐电子科技有

14、限公司的成品模块SRWF-1022,其提供透明数据接口,能适应任何标准或非标准的用户协议,自动过滤掉空中产生的假数据,用户无需编制多余的程序,实现所收即所发。标准配置提供8个信道,可扩展到16/32信道。满足用户多种通信组合方式。提供2个串口三种接口方式,COM1为TTL电平UART接口。COM2为硬件的RS-232/RS-485接口,相对于软口的RS-232/RS-485接口,其带载 能 力 更 强 ( 是 软 口 的6到8倍 ) , 工 作 更 加 稳 定 。 接 口 波 特 率 为1200/2400/4800/9600/19200bp列选,格式为8N1/8O1/8E1用户自定义,可传输无

15、限长的数据帧,用户编程灵活。接口图如下;串口使用软串口。因短距离无线通讯采用的是成品模块,故只需在电路上加一相应的接口。可靠性设计1、基于无线公网模块的应用已经积累了一定经验,总得来说仍然是驱动层及应用程序层双重保护,驱动层通过查询模块,获取链路状态;应用程序通过与上位机的通信超时机制判断链路状态;一旦发现链路异常,即通过重启链路方式修复通信。210元以太网接口功能通过以太网,建立CPU和主站的连接。接口描述通过hpauto-mdix(交叉线自动侦测及切换) 经过网络变压器连接到标准RJ45接头。设计原理网口电路主要是根据网络芯片LAN8720A的数据手册的网口推荐电路。 网络连接和传输指示灯

16、采用独立的LED灯指示。可靠性以往产品在实验中偶发发生以太网通讯时浪涌实验引起终端损坏或者重启等现象,随后改用独立网络变压器模式,大大降低出故障概率。成本估计8元RS232RS485电路功能将UART信号转化成RS232信号或RS485信号,用于RS232或RS485通讯。接口RS232或RS485电路用过UART口与CPU相连。设计原理因RS232和RS485外接端子是共用的,故需一个双刀双掷开关进行切换。RS232电路和RS485电路沿用其他产品的成熟电路。可靠性该部分电路比较成熟,尚未发现问题成本估计44.6元SD卡模块电路功能存储数据及参数。接口SD卡模块通过CPU的内置SD卡控制器接

17、口与CPU相连。设计原理所有数据线上都加个47K的上拉电阻用来防止振荡输入将引起非期望的高电流损耗和进行卡侦测。各数据线上外加一静电防护器件防止插拔SD卡时产生的静电干扰。可靠性成本估计8元直流量采集模块功能用以采集外接电压型(048V)/电流型(420mA)传感器信号。接口外部传感器信号通过直流量采集模块的信号转换后经AD芯片的IIC总线传输给CPU。设计原理直流采样部分比较关键的是AD的隔离输入电路,现采用的是线性光耦电路,在有效隔离的条件下保证输入输出的线性度。应用线性光耦合器组成的模拟信号隔离电路的线性度好,电路简单,有效地解决了模拟信号与单片机应用系统的电气隔离问题。驱动级、缓冲级采

18、用组合型运算放大器,可使线性度提高。如下图:电路主要由HCNR200型线性光耦和配套外围电路组成。HCNR200型线性光耦由发光二极管D1、反馈光电二极管D2、输出光电二极管D3组成。当D1通过驱动电流If时,发出红外光(伺服光通量)。该光分别照射在D2、D3上,反馈光电二极管吸收D2光通量的一部分,从而产生控制电流II。该电流用来调节If以补偿D1的非线性。输出光电二极管D3产生的输出电流I2与D1发出的伺服光通量成线性比例。 令伺服电流增益K1=I1/If,正向增益K2=I2/If,则传输增益K3=K2/K1=I2/I1,K3的典型值为1。然后通过运放将I2转化成电压,供AD采集。此电路中

19、K1=I1/IFR180/R181=20/10000=0.2%,I2弋I1=0.2%IF,VAD_DC2=R184*I2=136*IF136*IDC2。稳压管D55用于提供5.1V电压供运放工作。VCC通过R185、R186分压后给运放U35提供一个偏置电压,以补偿U37,D55损耗的电流。当输入为电压时,通过拨码开关使输入信号接到电压转电流电路,I=(DCV1*R65/(R65+R63)/R52=0.377*DCV1(mA),DCV1=048V,故I=018.1mA。可靠性成本估计25元USBHOS根口功能用于本地程序升级及调试接口USBHOST接口通过CPU内置的USB2.0接口与CPU相

20、连,支持USB2.0高速(480Mbps)全速(12Mbps)/低速(1.5Mbps)三种模式。3.2.9.3,设计原理1原理图如下:因CPU内部集成了USB2.0控制器,所以只需在电路上加一接口电路。此电路沿用其他产品的成熟电路。可靠性该电路经过之前的产品反复验证,已经基本成熟,风险较低。成本估计1.5元遥控遥信板硬件框图遥信电路模块功能用于外部24V直流开入信息的可靠采集,并通过FPAG实现的LVDS总线上送信息到主板。接口提供给外部开入信号的为无源24V共负极接口方式,物理接口端子为间距3.5mm的插拔式接线端子;与主板交换信息给的接口方式为LVDS高速差分总线,物理接口端子为哈丁板卡连

21、接端子。原理设计1、模块由信号处理电路部分和采集上传部分组成。单路信号处理电路原理如下图:2、采集上送功能电路在FPGA芯片EP4CE6E22C8内部实现。96路经上述信号处理电路传输过来的信号输入到FPGA的I/O口, 芯片把I/O口信息直接采集存储到内部寄存器,在接受到主板通过LVDS发送过来的查寻要求时,再把内部寄存器的信息调理成LVDS信号发送到主板上的FPGA信息处理芯片上。3、考虑到系统机械结构和信号的实际分布情况,把信号设计成6路一组,4组信号分布在一块系统插板上,最多4块插板能实现采集96路外部信号,4块插板通过LVDS与主板实现点对点通讯式信息交换。可靠性1、信号处理电路经过

22、前期的FTU产品反复验证,成熟,可靠。EMC性能达标。2、采集上送功能电路由可编程芯片实现,且LVDS模块基本成熟,风险较低。成本估计单路材料成本包含光耦、电阻、电容、二极管、发光管等。批量采购估计为:1.2元/路。遥控电路模块功能通过FPAG实现的LVDS总线接受主板的遥跳、遥合命令信息,并通过I/O口控制驱动板载功率继电器动作,从而实现对外部开关装置的控制功能。接口提供给外部开关装置的接口为继电器无源空触点,带载能力为:10A220VAC或10A30VDC,物理接口端子为间距5.08mm的插拔式接线端子; 与主板的接口方式为LVDS高速差分总线,物理接口端子为哈丁板卡连接端子。原理设计1、

23、模块的驱动输出部分原理图如下:2、设计思路是:主板信息通过LVDS总线传输过来,FPGA芯片EP4CE6E22C8内部实现LVDS差分信号的接收解析,确认需控制的对应I/O管脚,把对应管脚由默认的高电平输出,转换成低电平输出,对应的管脚连接到如上图中的YK1标识处驱动光耦,通过光耦实现隔离驱动功率继电器。4、考虑到系统机械结构和信号的实际分布情况,把信号设计成2路(遥跳、遥合)一组,4组信号分布在一块系统插板上,最多4块插板能实现采集16组32路外部开关设备的控制,4块插板通过LVDS与主板实现点对点通讯式信息交换。5、继电器的选型要考虑触点负荷,继电器的体积及价格。1、驱动电路经过前期的FT

24、U产品反复验证,成熟,可靠。EMC性能达标。2、信息接收处理功能电路由可编程芯片实现,且LVDS模块基本成熟,风险较低。成本估计单路材料成本包含光耦、电阻、二极管、继电器等。批量采购估计为:13元/路。遥测板遥测板框图遥测电路模块功能用于外部交流电压、电流信息的可靠采集,并通过FPAG实现的LVDS总线上送信息到主板。接口输入通过装置内部高精度CT、PT获取外部交流信号,物理接口端子为间距8mm的插拔式航空接线端子; 获取的交流信号经AD芯片转换并实时上传信息给主板, 输出与主板的接口方式为LVDS高速差分总线,物理接口端子为哈丁板卡连接端子。原理设计1、交流信号前级采集调理电路的原理如下:2

25、、信号的选择电路原理图如下:电路由模拟开关芯片ADG1334构成。模拟开关对信号的隔离和信噪抑制能到达-70DB。具体性能见下图(引用自芯片数据手册)。3、信号滤波采集电路原理如下。此电路主要采用芯片AD7606模数转换芯片实现,AD7606工作在并行方式,无过采,模拟信号的输入范围为-5V+5V,采用外部参考电压标准,外部参考电压由芯片REF5025A提供。4、AD芯片控制和LVDS电路原理图如下。FPGA芯片EP4CE6E22C8内部实现与AD芯片AD7606的总线接口电路,内部定时电路提供精准的采样间隔时间, 内部寄存器组提供数据的缓存空间, 内部的LVDS电路把缓存空间的数据调理成LV

26、DS信号发送到主板。可靠性1、AD采集电路前期经过反复验证,功能稳定可靠,对比以前的模拟信号电路在采样精度上有很大的提高。EMC性能达标的关键在PCB设计时要预留足够安全间距。2、电路中预留TVS管,保护芯片不受高压损坏,并预留安全地PGND改善EMC性能。3、AD控制和LVDS电路由可编程芯片实现,且LVDS模块基本成熟,风险较低。成本估计单路材料成本包含互感器、电阻、电容、AD部件、模拟开关部件等。批量采购估计为:25元/路。电源模块功能此模块把外部电源模块提供的电源经EMC可靠性处理后,分成3路24V电源。其中一路再经DCDC芯片降压处理后给装置提供可靠的24V、12V和5V电源;第二路

27、提供给外部操作回路使用,第三路给开入回路使用。此外本模块还实现了电源电池管理功能的控制和检测。接口输入物理接口端子为间距5.08mm的插拔式端子; 输出物理接口端子为哈丁板卡连接端子。原理设计1、电源部分的原理图如下:图中输入电源经共模抑制和滤波电路后再经气体放电管和压敏电阻对浪涌波形吸收处理后的24V电源一路供给DCDC隔离模块, 最后再经DCDC芯片降压产生5V和12V装置内部主电源; 第2、3路分别再次经共模抑制和滤波电路和气体放电管和压敏电阻处理后供给外部操作回路、开入回路使用;2、电源电池管理功能的控制和检测原理图如下:此电路实现装置对后备蓄电池的充放电状态的监控及控制。包括电源故障

28、、电池欠压、活化状态采集;电池活化启动、退出控制及电池退出控制等。在4级极度恶劣电磁环境下此电路对浪涌等EMC干扰的抑制性能有待进一步的验证,具有一定风险。可算是硬件设计的疑难点。成本估计材料成本包含压敏电阻、安规电容、共模电感、DCDC模块、DCDC芯片等。批量采购估计成本为:250元。元器件总成本:核心板380元CPU板415元电源板342元背板252元遥测板*4880*4=3520元遥信遥控板*4223*4=892元机箱800总计6601元3.5.硬件测试方法依据硬件设计规范要求的性能指标如信号完整性、电源纹波等,列出本次设计与性能指标对应的信号、测试点。测试点1):CPU系统电源,+3

29、.3V2):DDR2芯片电源,+1.8V3):CPU内核电源,+1.3V:USB内核电源,+1.2V:USB物理层1.8V电源,+1.8V5):485通讯电源,+3.3V6):直流量采集电路电源电压,+5V7):FPGA内核电源,+1.2V8):LVDS总线电源,+2.5V7):SPI通讯线;:I2C通讯线;:sUART/UART通讯线;.FPGAI辑设计分为子板逻辑和主板逻辑两部分。子板逻辑架构概述作,数据编解码,数据发送,数据接收功能,遥测参数储存等功能。FPGA内部逻辑主要由NIOSII软核处理器、AD7606接口模块、IO接口模块、EPCSFLASH控制接口模块,FIFO控制状态机,

30、收发FIFO以及LVDS收发电路组成。其中各模块通过AVALONMM总线与NIOSII处理器通讯。 以下仅对重要的模块进行说明。1)、CDR模块,原理如下:首先通过PLL产生两个相位相差90度频率为100MHz的时钟,利用CLK和CLK90的上升和下降沿分别对LVDS端口接收来的信号采样,如下图:A、B、C、D分别代表CLK0度、90度、180度、270度4种不同的采集相位,如果在AB之间发现数据有变化,则认为C点为当前数据的最佳采样点,以C点的采集数据做为本次时钟的采集数据,如果4个相位都未发生变化,则沿用上一次的最佳采样点。2)、8B/10B编解码模块由于CDR通过侦测数据的跳变沿来选择采样点,如果长时间数据没有变化,且发送和LVDS子板FPGA主要实现AD数据采集,遥信IO口数据采集,遥控IO口操子板逻辑如下图:LVDS收发部分的逻辑如下:transmitter接收时钟频率和相位上的误差和抖动,长时间使用同一个相位的

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 工程安全合同协议书

- 商品混凝土买卖合同书

- 房屋建筑装修工程施工合同

- 房屋租赁合同条件

- 施工材料代购合同协议书

- 外贸杂货采购合同范本

- 境外白糖采购合同范本

- 劳务转包简易合同范本

- 遵化交通安全课件

- 2025教师资格考试高中语文标准预测试卷答案及解析1-5

- 湖南省炎德英才名校联考联合体2024-2025学年高二下学期3月月考-化学+答案

- 腾讯财经笔试题库及答案

- 昆明市官渡区卫生健康局招聘笔试真题2024

- 吉林省吉林市2024-2025学年高三下学期3月三模试题 历史 含答案

- 2024年昆明市官渡区卫生健康局招聘考试真题

- (一模)2025年广东省高三高考模拟测试 (一) 英语试卷(含官方答案)

- 办公室环境改善项目计划书

- 肛瘘的术后护理

- 畜牧兽医创新创业

- 《鸿门宴》课本剧:楚汉风云震撼开场看英雄如何对决

- 《高技术产业》课件

评论

0/150

提交评论