版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

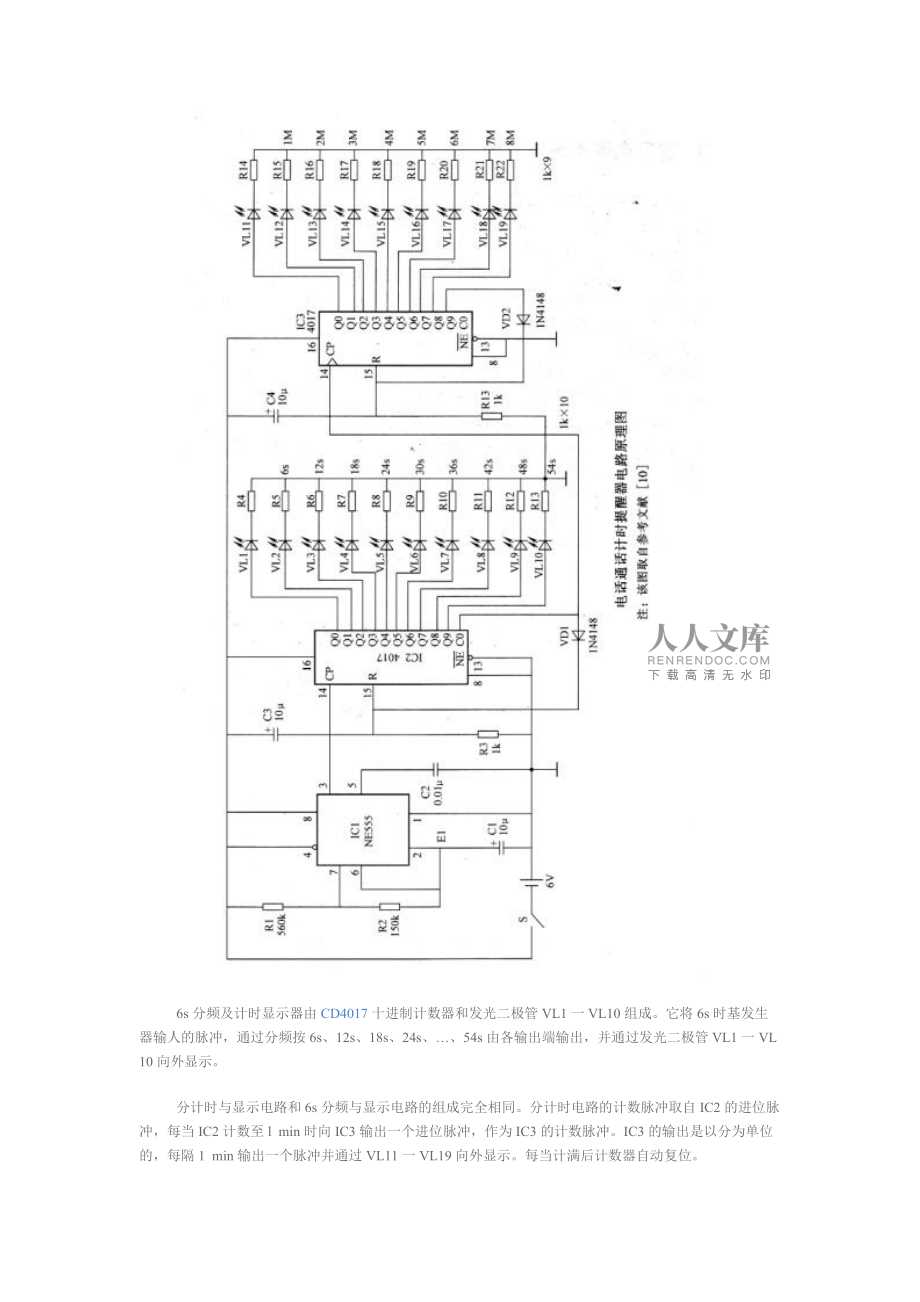

1、目前我国电话实行以分为单位的计时收费方式,除了在第1而n内,即第一个时段为固定收费外,每当进人下一个时段后的第is便立即增加一个时段的收费。对于时间较长的通话来说,多1min的计时收费,在整个通话的计费中其比例是很小的。但是对于经常只需在1 min内完成通话的情况中,即使通话时间拖延1s,其多付出的话费在整个话费中的比例就显得很高。本例介绍的电话通话计时提醒器,对于这样一类通话就显得很有意义了。 工作原理电话通话计时提醒器电路原理图如图所示。全电路由6s时基发生器、6s分频计时及显示器和分计时与显示器组成。6s时基发生器是一个由NE555时基集成电路组成的多谐振荡器,它通过对Rl、R2和C1数

2、值的设定,使振荡器每6s输出一个时基脉冲。 6s分频及计时显示器由CD4017十进制计数器和发光二极管VL1一VL10组成。它将6s时基发生器输人的脉冲,通过分频按6s、12s、18s、24s、54s由各输出端输出,并通过发光二极管VL1一VL10向外显示。分计时与显示电路和6s分频与显示电路的组成完全相同。分计时电路的计数脉冲取自IC2的进位脉冲,每当IC2计数至l min时向IC3输出一个进位脉冲,作为IC3的计数脉冲。IC3的输出是以分为单位的,每隔1 min输出一个脉冲并通过VL11一VL19向外显示。每当计满后计数器自动复位。电路中,C2、R3组成IC2的开机复位电路,C4、R13组

3、成IC3的开机复位电路。接通电源后计数器自动复位,Q0输出高电平,VLl, VLll发光指示。VDl,VD2分别是IC2和IC3的复位控制二极管。当计数器计满后通过VD1、VD2加至R端使其自动复位。元器件选择ICl选用NE555时基集成电路;IC2、IC3选用CD4017十进制计数脉冲分配器数字集成电路。其他元器件均无特殊要求,可按图所标型号及参数进行选用。555时基电路是一种将模拟功能与逻辑功能巧妙结合在同一硅片上的组合集成电路。它设计新颖,构思奇巧,用途广泛,备受电子专业设计人员和电子爱好者的青睐,人们将其戏称为伟大的小IC。1972年,美国西格尼蒂克斯公司(Signetics)研制出T

4、merNE555双极型时基电路,设计原意是用来取代体积大,定时精度差的热延迟继电器等机械式延迟器。但该器件投放市场后,人们发现这种电路的应用远远超出原设计的使用范围,用途之广几乎遍及电子应用的各个领域,需求量极大。美国各大公司相继仿制这种电路1974年西格尼蒂克斯公司又在同一基片上将两个双极型555单元集成在一起,取名为NF556。1978年美国英特锡尔公司(Intelsil)研制成功CMOS型时基电路ICM5551CM556,后来又推出将四个时基电路集成在一个芯片上的四时基电路558由于采用CMOS型工艺和高度集成,使时基电路的应用从民用扩展到火箭、导弹,卫星,航天等高科技领域。在这期间,日

5、本、西欧等各大公司和厂家也竞相仿制、生产。尽管世界各大半导体或器件公司、厂家都在生产各自型号的555556时基电路,但其内部电路大同小异,且都具有相同的引出功能端。图中示出了美国无线电公司生产的CA555时基电路的内部等效电路图。CA555时基电路的内部等效电路图:2005_07/05072521176458.gif等效功能电路:upload/2005_07/05072521175440.gif鉴于各种双极型的555集成块的内部电路大同小异,下面我们以Cne555资料A555为例分析其内部电路和原理。从CA555时基电路的内部等效电路图中可看到,VTl-VT4、VT5、VT7组成上比较器Al,

6、VT7的基极电位接在由三个5k电阻组成的分压器的上端,电压为VDDne555的应用;VT9-VT13组成下比较器A2,VTl3的基极接分压器的下端,参考电位为VDD。在电路设计时,要求组成分压器的三个5k电阻的阻值严格相等,以便给出比较精确的两个参考电位VDD和VDD。VTl4-VTl7与一个4.7k的正反馈电阻组合成一个双稳态触发电路。VTl8-VT21组成一个推挽式功率输出级,能输出约200mA的电流。VT8为复位放大级,VT6是一个能承受50mA以上电流的放电晶体三极管。双稳态触发电路的工作状态由比较器A1、A2的输出决定。555时基电路的工作过程如下:当2脚,即比较器A2的反相输入端加

7、进电位低于VDD的触发信号时,则VT9、VTll导通,给双稳态触发器中的VTl4提供一偏流,使VTl4饱和导通,它的饱和压降Vces箝制VTl5的基极处于低电平,使VTl5截止,VTl7饱和,从而使VTl8截止,VTl9导通,VTne555中文资料20完全饱和导通,VT21截止。因此,输出端3脚输出高电平。此时,不管6端(阈值电压)为何种电平,由于双稳态触发器(VTl4-VTl7)中的47k电阻的正反馈作用(VTl5的基极电流是通过该电阻提供的),3脚输出高电平状态一直保持到6脚出现高于VDD的电平为止。当触发信号消失后,即比较器A2反相输入端2脚的电位高于VDD,则VT9、VTll截止,VT

8、l4因无偏流而截止,此时若6脚无触发输入,则VTl7的Vces饱和压降通过4.7k电阻维持VTl3截止,使VTl7饱和稳态不变,故输出端3脚仍维持高电平。同时,VTl8的截止使VT6也截止。当触ne555原理发信号加到6脚时,且电位高于VDD时,则VTl、VT2、VT3皆导通。此时,若2脚无外加触发信号使VT9、VTl4截止,则VT3的集电极电流供给VTl5偏流,使该级饱和导通,导致VTl7截止,进而VTl8导通,VTl9、VT2。都截止,VT21饱和导通,故3脚输出低电平。当6脚的触发信号消失后,即该脚电位降至低于VDD时,则VTl、VT2、VT3皆截止,使VTl5得不到偏流。此时,若2脚仍

9、无触发信号,则VTl5通过4.7k电阻得到偏流,使VTl5维持饱和导通,VTl7截止的稳态,使3脚输出端维持在低电平状态。同时,VTl8的导通,使放电级VT6饱和导通。通过上面两种状态的分析,可以发现:只要2脚的电位低于VDD,即有触发信号加入时,必使输出端3脚为高电平;而当6脚的电位高于VDD时,即有触发信号加进时,且同时2脚的电位高于VDD时,才能使输出端3脚有低电平输出。4脚为复位端。当在该脚加有触发信号,即其电位低于导通的饱和压降0.3V时,VT8导通,其发射极电位低于lV,因有D3接入,VTl7为截止状态,VTl8、VT21饱和导通,输出端3脚为低电平。此时,不管2脚、6脚为何电位,

10、均不能改变ne555工作原理这种状态。因VT8的发射极通过D3及VTl7的发射极到地,故VT8的发射极电位任何情况下不会比1.4V电压高。因此,当复位端4脚电位高于1.4V时,VT8处于反偏状态而不起作用,也就是说,此时输出端3脚的电平只取决于2脚、6脚的电位。根据上面的分析,CA555时基电路的内部等效电路可简化为如图所示的等效功能电路。显然,555电路(或者专556电路)内含两个比较器A1和A2、一个触发器、一个驱动器和一个放电晶体管。两个比较器分别被电阻R1、R2和R3构成的分压器设定的VDD和VDD。参考电压所限定。为进一步理解其电路功能,并灵活应用555集成块,下面简要说明其作用机理

11、。从图15可见,三个5k电阻组成的分压器,使内部的两个比较器构成一个电平触发器,上触发电平为VDD,下触发电平为VDD。在5脚控制端外接一个参考电源Vc,可以改变上、下触发电平值。比较器Al的输出同或非门l的输入端相接,比较器A2的输出端接到或非门2的输入端。由于由两个或非门组成的RS触发器必须用负极极性信号触发,因此,加到比较器Al同相端6脚的触发信号,只有当电位高于反相端5脚的电位时,RS触发器才翻转;而加到比较器A2反相端2脚的触发信号,只有当电位低于A2同相端的电位VDD时,RS触发器才翻转。通过上面对等效功能电路和CA555时基电路的内部等效电路的分析,可得出555各功能端的真值表。

12、引脚26437电平VDD*1.4V高电平悬空状态电平VDDVDD1.4V低电平低电平电平VDD1.4V保持电平保持电平*0.3V低电平低电平由表可看出,S、R、MR的输入不一定是逻辑电平,ne555 价格可以是模拟电平,因此,该集成电路兼有模拟和数字电路的特色。 相关阅读:ne555逆变器+课程设计家用智能控制系统 1536201.非法入侵报警ne555的应用42.节能灯控制ne555中文资料93.有害气体检测、报警、抽排ne555的应用电路图134.体会.断线报警器制作%ne555逆变器 、原理分析电路的核心部分ne555的应用由NE555组成,R1、R2、C1和NE555组ne555的应用

13、电路图成一个频率越为3KHz左右的多谐振荡电路,当电路接通电源时,振荡器开始工作蜂鸣器LS1发出响声;当1和2被短接时,振荡器的工NE555时基电路#ne555工作原理 表1是NE555的极限参数,不同的封装形式及不同的生产厂商的器件这些参数不尽相同,极限参数是指在不损坏器件的情况下,厂商保证的界限,并非可以工作的条件,如果超过某一环境下使用,其间的安全性将不会得到保证,这使用ne555应用中应加以注意。.ne555价格+空调器及其微电脑控制器的原理与维修第三版 目录:第1章空调器基础知识11空调器的作用及制冷原理111空调名词术语112空调器的作用113蒸气ne555的应用电路图压缩式制冷n

14、e555中文资料原理114热力学名词、术语115热力学基本定律116制冷循环的热.网友在各自领域中所用到的芯片总结转载www$ne555电路 1.音频pcm编码DA转换芯片cirruslogic的csne555价格4344,cs43344334是老封装,据说已经停产,4344封装比较小,非常好用。还有菲利谱的。8211等。2.音频放大片4558,833,此二芯片都是双最新评论555 电路组成多波形多谐振荡器.输出的波形为矩形波,通过对输出矩形波的占空比的调节,可以形成方波。如果对所输出的方波进行进一步处理,就可以形成多种波形的输出信号。图2-23 所示电路以555 振荡电路为核心,通过积分变换

15、电路可以形成多种波形输出,这些波形包括方波、钟形波、三角波和正弦波。555 电路组成多波形多谐振荡器电路工作原理分析 NE555 与R1 、R2 及C3 组成典型的555 多谐振荡电路,由于R1的阻值远小于R2 ,所以输出的波形基本上为方波。该方波信号由脚输出,通过分压电阻R7 、R8 的分压后加至输出波形选择开关的B 点,经选择开关将方波信号加至射极输出器VT2 的基极,通过VT2 缓冲变换后由发射极输出,再经c8捐合加至调节电位器RP ,通过调节在输出端得到方波信号。由NE555 的脚输出的方波信号经过C7 的藕合,加至由R4 、C5 组成的第一节积分变换电路,经积分变换后,将方波变换为钟

16、形波并加至选择开关的C 点,经VT2 缓冲后输出钟形波信号。将钟形波信号通过由R5 、C6 组成的第二节积分变换电路进行第二次积分变换后,钟形波变换为三角波并加至选择开关的D 点,经VT2 缓冲后输出三角波信号。由R5 , C6 形成的三角波,经R6 搞合至由VT1 与C2 组成的放大电路进行放大和变换。在该放大电路中,由于电容C2 的反馈作用,输入的三角波变换为正弦波,由VT1 的集电极输出三角波信号。555 电路组成多波形多谐振荡器电路输出波形的频率约1kHz ,被形幅度为O200mV (峰峰值)。555定时器由3个阻值为5k的电阻组成的分压器、两个电压比较器C1和C2、基本RS触发器、放

17、电三极管TD和缓冲反相器G4组成。虚线边沿标注的数字为管脚号。其中,1脚为接地端;2脚为低电平触发端,由此输入低电平触发脉冲;6脚为高电平触发端,由此输入高电平触发脉冲;4脚为复位端,输入负脉冲(或使其电压低于0.7V)可使555定时器直接复位;5脚为电压控制端,在此端外加电压可以改变比较器的参考电压,不用时,经0.01uF的电容接地,以防止引入干扰;7脚为放电端,555定时器输出低电平时,放电晶体管TD导通,外接电容元件通过TD放电;3脚为输出端,输出高电压约低于电源电压1V3V,输出电流可达200mA,因此可直接驱动继电器、发光二极管、指示灯等;8脚为电源端,可在5V18V范围内使用。55

18、5定时器工作时过程分析如下:5脚经0.01uF电容接地,比较器C1和C2的比较电压为:UR1=2/3VCC、UR2=1/3VCC。当VI12/3VCC,VI21/3VCC时,比较器C1输出低电平,比较器C2输出高电平,基本RS触发器置0,G3输出高电平,放电三极管TD导通,定时器输出低电平。当VI12/3VCC,VI21/3VCC时,比较器C1输出高电平,比较器C2输出高电平,基本RS触发器保持原状态不变,555定时器输出状态保持不来。当VI12/3VCC,VI21/3VCC时,比较器C1输出低电平,比较器C2输出低电平,基本RS触发器两端都被置1,G3输出低电平,放电三极管TD截止,定时器输

19、出高电平。当VI12/3VCC,VI21/3VCC时,比较器C1输出高电平,比较器C2输出低电平,基本RS触发器置1,G3输出低电平,放电三极管TD截止,定时器输出高电平。CD4017功能简述: CD4017是5位Johnson计算器,具有10个译码输出端,CP,CR,INH输入端。时钟输入端的斯密特触发器具有脉冲整形功能,对输入时钟脉冲上升和下降时间无限制。INH为低电平时,计算器在时钟上升沿计数;反之,计数功能无效。CR为高电平时,计数器清零。Johnson计数器,提供了快速操作,2输入译码选通和无毛刺译码输出。防锁选通,保证了正确的计数顺序。译码输出一般为低电平,只有在对应时钟周期内保持

20、高电平。在每10个时钟输入周期CO信号完成一次进位,并用作多级计数链的下级脉动时钟。 CD4017逻辑结构图: CD4017 Logic Diagram 逻辑图CD4017引脚图: CD4017的引脚图CD4017引脚功能:CD4017内部是除10的计数器及二进制对10进制译码电路。CD4017有16支脚,除电源脚VDD及VSS为电源接脚,输入电压范围为315V之外,其余接脚为:A、频率输入脚:CLOCK(Pin14),为频率信号的输入脚。B、数据输出脚:a、 Q1-Q9(Pin3,2,4,7,10,1,5,6,9,11),为解码后的时进制输出接脚,被计数到的值,其输出为Hi,其余为Lo 电位

21、。b、CARRY OUT(Pin12),进位脚,当4017计数10个脉冲之后,CARRY OUT将输出一个脉波,代表产生进位,共串级计数器使用。D、 控制脚:a、 CLEAR(Pin15):清除脚或称复位(Reset)脚,当此脚为Hi时,会使CD4017的Q0为”1”,其余Q1-Q9为”0”。b、CLOCK ENABLE(Pin13),时序允许脚,当此脚为低电位,CLOCK输入脉波在正缘时,会使CD4017计数,并改变Q1-Q9的输出状态。数字电路CD4017是十进制计数分频器,它的内部由计数器及译码器两部分组成,由译码输出实现对脉冲信号的分配,整个输出时序就是O0、O1、O2、O9依次出现与时钟同步的高电平,宽度等于时钟周期。 CD4017有10个输出端(O0O9)和1个进位输出端O5-9。每输入10个计数脉冲,O5-9就可得到1个进位正脉冲,该进位输出信号可作为下一级的时钟信号。 CD4017有3个输(MR、CP0和CP1),MR为清零端,当在MR端上加高电平或正脉冲时其输出O0为高电平,其余输出端(O1O9)均为低电平。CP0和CPl是2个时钟输入端,若要用上升沿来计数,则信号由CP0端输入;

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 二零二五年度电梯安装与智能化运营合同

- 2025年度事业单位聘用合同解除及双方权益保障协议

- 二零二五年度车辆寄售客户隐私保护合同

- 2025年度市政工程农民工劳动合同标准文本4篇

- 2025年度年度服装行业员工劳动合同修订版

- 2025年度煤炭购销居间不可撤销中介合同

- 二零二五年度旅游度假品牌区域代理经营合同

- 二零二五年度房地产代理业务简短合同模板

- 二零二五版新能源汽车充电桩建设与租赁合同4篇

- 二零二五年度牛羊肉出口退税手续办理合同4篇

- 2024人教新目标(Go for it)八年级英语下册【第1-10单元】全册 知识点总结

- 垃圾车驾驶员聘用合同

- 2024年大宗贸易合作共赢协议书模板

- 新闻记者证600道考试题-附标准答案

- 变压器搬迁施工方案

- 单位转账个人合同模板

- 八年级语文下册 成语故事 第十五课 讳疾忌医 第六课时 口语交际教案 新教版(汉语)

- 中考语文二轮复习:记叙文阅读物象的作用(含练习题及答案)

- 2024年1月高考适应性测试“九省联考”数学 试题(学生版+解析版)

- (正式版)JBT 11270-2024 立体仓库组合式钢结构货架技术规范

- EPC项目采购阶段质量保证措施

评论

0/150

提交评论