版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

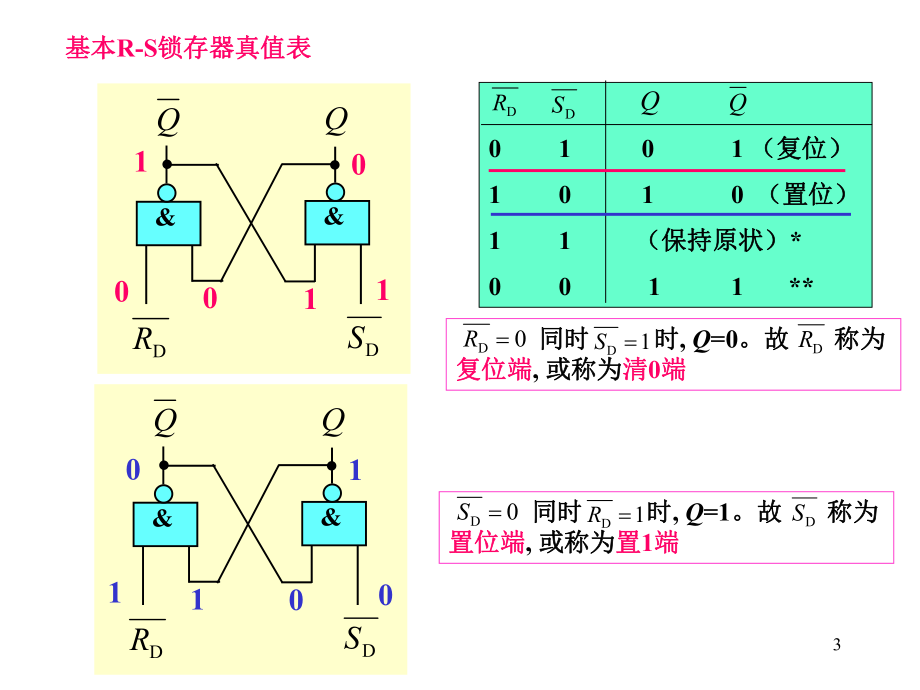

1、19.1 触发器 19.1.1 锁存器 19.1.2 D触发器 19.1.3 JK触发器19.2 寄存器 19.2.1 并行数码寄存器 19.2.2 串行移位寄存器 19.2.3 集成电路移位寄存器19.3计数器 19.3.1 二进制加法计数器 19.3.2 十进制加法计数器 19.3.3 任意进制计数器 19.3.3 集成电路计数器 19.3.3计数器应用举例第第19讲讲第第19章章 时序逻辑电路时序逻辑电路119.1 触发器触发器19.1.1 锁存器锁存器1.基本的基本的R-S锁存器锁存器组成:用组成:用2个与非门个与非门(或或2个或非门个或非门)构成构成&QQDRDS Set D

2、irect直接置位端直接置位端DS Reset Direct直接复位端直接复位端DR 、 输出端输出端QQQQDRDSR-S锁存器符号锁存器符号2&QQDRDS&QQDRDS基本基本R-S锁存器真值表锁存器真值表0111000 1 0 1 (复位)(复位)1 0 1 0 (置位)(置位)1 1 (保持原状)(保持原状)*0 0 1 1 *QQDRDS 同时同时 时时, Q=0。故。故 称为称为复位端复位端, 或称为或称为清清0端端1DS0DRDR011100 同时同时 时时, Q=1。故。故 称为称为置位端置位端, 或称为或称为置置1端端1DR0DSDS3&QQDRDS

3、R-S锁存器真值表锁存器真值表01100110 1 0 1 (复位)(复位)1 0 1 0 (置位)(置位)1 1 (保持原状)(保持原状)*0 0 1 1 *QQDRDS 指指 、 从从01或或10变成变成11时,时,输出端状态不变输出端状态不变DRDS4&QQDRDSR-S锁存器真值表锁存器真值表0011110 1 0 1 (复位)(复位)1 0 1 0 (置位)(置位)1 1 (保持原状)(保持原状)*0 0 1 1 *QQDRDS&QQDRDS110011当当 、 同时从同时从00变成变成11时时DRDS001假设右与非门翻转快,假设右与非门翻转快,Q先变为先变为0设计

4、电路时此种情况应避免设计电路时此种情况应避免 所以所以 、 同时从同时从00变成变成11时时, 输出端状态不定,输出端状态不定, 、 可能是可能是01,也可能是,也可能是10。DRDSQQ5R-S 锁存器特点锁存器特点:(2) 可触发使之翻转可触发使之翻转 (使使 、 之一为之一为0时可翻转时可翻转)。DRDS(1) 具有两个稳态具有两个稳态( 或或 )。1 , 0QQ0 , 1QQ(3) 具有记忆功能具有记忆功能( 、 都为都为1时,保持原来状态时,保持原来状态)。DRDS6R-S锁存器应用举例锁存器应用举例: 单脉冲发生器单脉冲发生器&QQDRDS+5V+5V4.7k 4.7k K

5、7R-S锁存器应用举例锁存器应用举例: 单脉冲发生器单脉冲发生器&QQDRDS+5V+5V4.7k 4.7k K8R-S锁存器应用举例锁存器应用举例: 单脉冲发生器单脉冲发生器&QQDRDS+5V+5V4.7k 4.7k KQQt正脉冲正脉冲负脉冲负脉冲92. 2. 门控门控R-SR-S锁存器锁存器控制端控制端&RSGDRDSQQ电路组成电路组成功能表功能表 G R S Q n+1 说明说明 1 0 0 Qn 保持保持 1 0 1 1 置置1 1 1 0 0 清清0 1 1 1 *不定不定 避免避免 0 Qn 保持保持10门控门控R-S锁存器功能表锁存器功能表 G R

6、S Q n+1 说明说明 1 0 0 Qn 保持保持 1 0 1 1 置置1 1 1 0 0 清清0 1 1 1 *不定不定 避免避免 0 Qn 保持保持3. 门控门控D锁存器组成及功能锁存器组成及功能1D&RSGDRDSQQ电路组成电路组成其他两种情况不会出现其他两种情况不会出现只有这三种情况只有这三种情况具有数据记忆功能具有数据记忆功能G=1时时, Q =DG=0时时, 保持原状保持原状 G D Q 1 0 0 1 1 1 0 保持保持门控门控D锁存器功能表锁存器功能表111D&GQQDRDS 门控门控D锁存器的改进及符号锁存器的改进及符号集成电路集成电路74LS75, 7

7、4LS373门控门控D锁存器符号锁存器符号DGDRDSQQ1219.1.2 D19.1.2 D触发器触发器1. 时钟时钟上升上升沿触发沿触发的的维持阻塞型维持阻塞型D触发器触发器时钟上升沿触发的时钟上升沿触发的D触发器符号触发器符号DCPDRDSQQ时钟时钟数据输入端数据输入端输出输出直接复位端直接复位端直接置位端直接置位端DQn1特性方程特性方程DCP&DRDSQQ功能表功能表CP Q n+1D功能表说明:功能表说明: 在在CP上升沿时,上升沿时,Q等于等于D;在;在CP高高电平、低电平和下电平、低电平和下降沿时,降沿时,Q保持不保持不变。变。132. 时钟时钟下升下升沿触发沿触发的

8、的维持阻塞型维持阻塞型D触发器触发器DQn1特性方程特性方程功能表功能表CP Q n+1D功能表说明:功能表说明: 在在CP下升沿时,下升沿时,Q等于等于D;在;在CP高电平、高电平、低电平和上降沿时,低电平和上降沿时,Q保持不变。保持不变。时钟下升沿触发的时钟下升沿触发的D触发器符号触发器符号DCPDRDSQQ14课堂练习课堂练习 题目题目: 时钟时钟CP及输入信号及输入信号D 的波形如图所示的波形如图所示, 试画出各触发器输出试画出各触发器输出端端Q的波形的波形,设各输出端设各输出端Q的初始状态的初始状态=0.DQDCPQ1DQDCPQ2CP上升沿触发上升沿触发CP下升沿触发下升沿触发CP

9、DQ1tttQ2t153. 3. 集成集成D D触发器介绍触发器介绍(1) 集成双集成双D触发器触发器74LS74VCC(+5V)GND(地地)DCPDRDSQQDCPDRDSQQ16例例: 用用D触发器触发器 将一个时钟进行将一个时钟进行2分频分频.CPCPQQ01 22分频器分频器DCPQQ 、 不用时不用时, 甩空或通甩空或通过过4.7k 的电阻吊高电平。的电阻吊高电平。DRDS频率关系:频率关系:2CPQff17用用2个个2分频器级联组成一个分频器级联组成一个4分频器分频器1Q2QCPDCPQQDCPQQ频率关系:频率关系:42CP1Q2Qfff 44分频器分频器18(2) 集成集成4

10、D触发器触发器74LS175公共公共CP端,公共端,公共清清0端,无置端,无置1端。端。CP1D2D3D4D2Q1Q3Q4Q1QVcc(+5V)GNDCLR4Q3Q2QRDDQQRDDQQRDDQQRDDQQ符号符号 CLR 74LS1751D 2D 3D 4D4D触发器触发器CP1Q 1Q 2Q 2Q 3Q 3Q 4Q 4Q19集成集成4D触发器触发器74LS175的应用举例的应用举例抢答电路抢答电路参赛人参赛人抢答按键抢答按键主持人清主持人清0按键按键1Q 1Q 2Q 2Q 3Q 3Q 4Q 4QVCCGND1D 2D 3D 4D CPCLR5004+5V111&1+5V4.7k

11、风鸣器风鸣器CLK1kHz甲甲乙丙丁74LS175120(3) 集成集成8D触发器触发器74LS273内部有内部有8个个D触发器触发器CP1D8DCLRGNDVCC1Q2D3D4D5D6D7D2Q3Q4Q5Q6Q7Q8QQDRDQDRD组成组成符号符号CLR 74LS2731D 2D 3D 4D 5D 6D 7D 8D8D触发器触发器CP1Q 2Q 3Q 4Q 5Q 6Q 7Q 8Q2119.2寄存器寄存器19.2.1 数码寄存器数码寄存器(并行寄存器并行寄存器)一个一个D触发器组成触发器组成1位的数码寄存器位的数码寄存器一般由一般由D触发器组成,用于存放数码。触发器组成,用于存放数码。由由4

12、D集成电路集成电路74LS175组成组成4位二进制数寄存器位二进制数寄存器由由8D集成电路集成电路74LS273组成组成8位二进制数寄存器位二进制数寄存器DCPQQD CLR 74LS1754D 3D 2D 1D4D触发器触发器CP4Q 3Q 2Q 1QCPD3D2D1D0+5VQ3Q2Q1Q04位二进制数位二进制数D3D0CLR 74LS2738D 7D 6D 5D 4D 3D 2D 1D8D触发器触发器CP8Q 7Q 6Q 5Q 4Q 3Q 2Q 1QQ3Q2Q1Q0Q4Q5Q6Q78位二进制数位二进制数D7D0D7 D6 D5 D4D3D2D1D0CP+5V22计算机计算机 并行输入并行

13、输入/输出接口输出接口基本原理基本原理外部设备外部设备(打印机打印机)8D锁存器锁存器8D1D8Q1QCP计算机计算机CPU控制信号控制信号计算机计算机输出接口输出接口D7D0计算机数据计算机数据2319.2.2 串行移位寄存器串行移位寄存器1. 用用D触发器组成的移位寄存器触发器组成的移位寄存器(右移,串入,串出右移,串入,串出/并出)并出)QSRDQ0Di串行输串行输入数据入数据RDCPQSRDQ1QSRDQ2QSRDQ3Q0 Q1 Q2 Q31CP 1 0 0 0RD 0 0 0 0Di1 1 0 112342CP 0 1 0 03CP 1 0 1 04CP 1 1 0 1串行串行输出输

14、出Q0Q3Q2Q1并行输出并行输出4个个CP后后Di的的4位数据出位数据出现在并行输出端现在并行输出端Q0Q3。再再4个个CP后后Di的的4位数据从位数据从串行输出端串行输出端Q3全部移出。全部移出。24QSRDQ0RDCPQSRDQ1QSRDQ2QSRDQ312342. 循环移位寄存器循环移位寄存器CP Q0 Q1 Q2 Q31 0 1 0 00 1 0 0 02 0 0 1 03 0 0 0 14 1 0 0 0初始值初始值经经4个个CP脉冲脉冲循环一周循环一周 Q0 Q1 Q2 Q3移位方向移位方向253. 并入并入/串出移位寄存器串出移位寄存器 CP Q0 Q1 Q2 Q3 0 1 0

15、 1 11 1 1 0 11 1 1 1 01 1 1 1 1SHIFT/LOAD1 0 1 11 0 1 1置入置入移位移位移位移位移位移位移位时移位时Q3先输出先输出移位方向移位方向D0Q0 Q1 Q2 Q31根据每个时钟上升根据每个时钟上升沿后沿后Q3的状态,可的状态,可画出画出Q3的波形图的波形图0 时,置入时,置入0111 时,移位时,移位CP并行输入数据并行输入数据串行输出串行输出QQ3QDQD&1D&1QD&11Q2Q1Q0D2D3D1D0SHIFT/LOAD移位/置入26计算机计算机串行接口串行接口基本原理基本原理D0D1D2D3CPQ3并入并入/串出串

16、出移位寄存器移位寄存器CP甲计算机数据甲计算机数据Q0Q1Q2Q3CPDi串入串入/并出并出移位寄存器移位寄存器CP乙计算机数据乙计算机数据274. 双向移位寄存器双向移位寄存器左移串入数据Q0左移串行输出右移串入数据&1&1&11DLDRRIGHT/LEFT右移/左移控制CP右移串行输出Q0D0Q1D1Q3D3Q2D2Q3&1右移(右移( ) :黄门开通,蓝门关闭,黄门开通,蓝门关闭,D0=DR,D1=Q0,D2=Q1 D3=Q2,每一个,每一个CP,依次右移一位。,依次右移一位。右移移位方向:右移移位方向:DRQ0Q1Q2Q3。1/LEFTRIGHT左移(左

17、移( ) :蓝门开通,黄门关闭,蓝门开通,黄门关闭,D3=DL,D2=Q3,D1=Q2 D0=Q1,每一个,每一个CP,依次左移一位。,依次左移一位。左移移位方向:左移移位方向:Q0Q1 Q2 Q3 DL。0/LEFTRIGHT28引脚图引脚图右移串入数据右移串入数据(A、B是与的关系)是与的关系)清清0端端时钟时钟CPQ0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 CLRAB74LS1648位并行输出位并行输出19.2.3 集成电路移位寄存器集成电路移位寄存器1. 串入串入/并出右移移位寄存器并出右移移位寄存器74LS164思考:数据思考:数据Di经多少个经多少个CP上升沿后,出现在右边上升

18、沿后,出现在右边74LS164的的Q7上?上?ABABQ0Q7ABQ0Q7DiCP74LS16474LS164级联级联每来一个每来一个CP,AB送送Q0,原来的,原来的Q0至至Q7依次右移一位,依次右移一位,Q7丢失。丢失。29Q0 Q1 Q2 Q3 DR D0 D1 D2 D3 DL CLRS1S0CP74LS1942. 双向移位寄存器双向移位寄存器(74LS194)并行输入数据并行输入数据右移串入数据右移串入数据方式控制方式控制输出输出清清0端端移位移位脉冲脉冲左移串入数据左移串入数据右移右移左移左移30双向移位寄存双向移位寄存74LS194的功能表的功能表CLR CP S1 S0 Q0 Q1 Q2 Q3 0 0 0 0 0 1 0 0 保持保持 1 0 1 1 1 0 1 1 1 D0 D1 D2 D3 (并行输入并行输入) 右移一位右移一位DR左移一位左移一位DLQ0 Q1 Q2 Q3 DR D0 D1 D2 D3 DL CLRS1S0CP74LS194方式控制方式控制输出输出预置数据预置数据左移串入左移串入右移串入右移串入清清0移位脉冲移位脉冲31+5V发光二发光二极管极管LED1k Q0 Q1 Q2 Q3 DR D0 D1 D2 D3 DL S1S0CP74LS194CLRQ0 Q1 Q2 Q3

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2024年SCMP考试日程试题及答案

- 甘肃交通职业技术学院《印刷电路板设计与制作》2023-2024学年第二学期期末试卷

- 广西质量工程职业技术学院《建筑设计1》2023-2024学年第二学期期末试卷

- 2025年河北省秦皇岛市卢龙县高中高三第二次教学质量检测试题语文试题试卷含解析

- 2025海南省安全员-C证考试(专职安全员)题库附答案

- 长春建筑学院《核医学设备与检查技术》2023-2024学年第二学期期末试卷

- 实现CPMM高分的备考法及试题及答案

- 新疆维吾尔自治区吐鲁番市高昌区第二中学2024-2025学年高三下学期第一次周考数学试题(重点班)试题含解析

- 北华航天工业学院《医学生理学》2023-2024学年第一学期期末试卷

- 2025届甘肃省武威市河西成功学校高三下学期开学考试生物试题试卷含解析

- 失血性休克应急预案及处理流程

- 边坡被动防护网的施工细则

- 少儿绘画之《春江水暖鸭先知》

- 2022中医医院章程(完整版)

- 2020 ACLS-PC-SA课前自我测试试题及答案

- QGDW 1168-2013 输变电设备状态检修试验规程(高清版)

- 10000中国普通人名大全

- 第二代身份证号码验证器

- 市场调查与预测复习资料

- GB_T 229-2020 金属材料夏比摆锤冲击试验方法

- 施工组织设计双代号时标网络图

评论

0/150

提交评论