版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

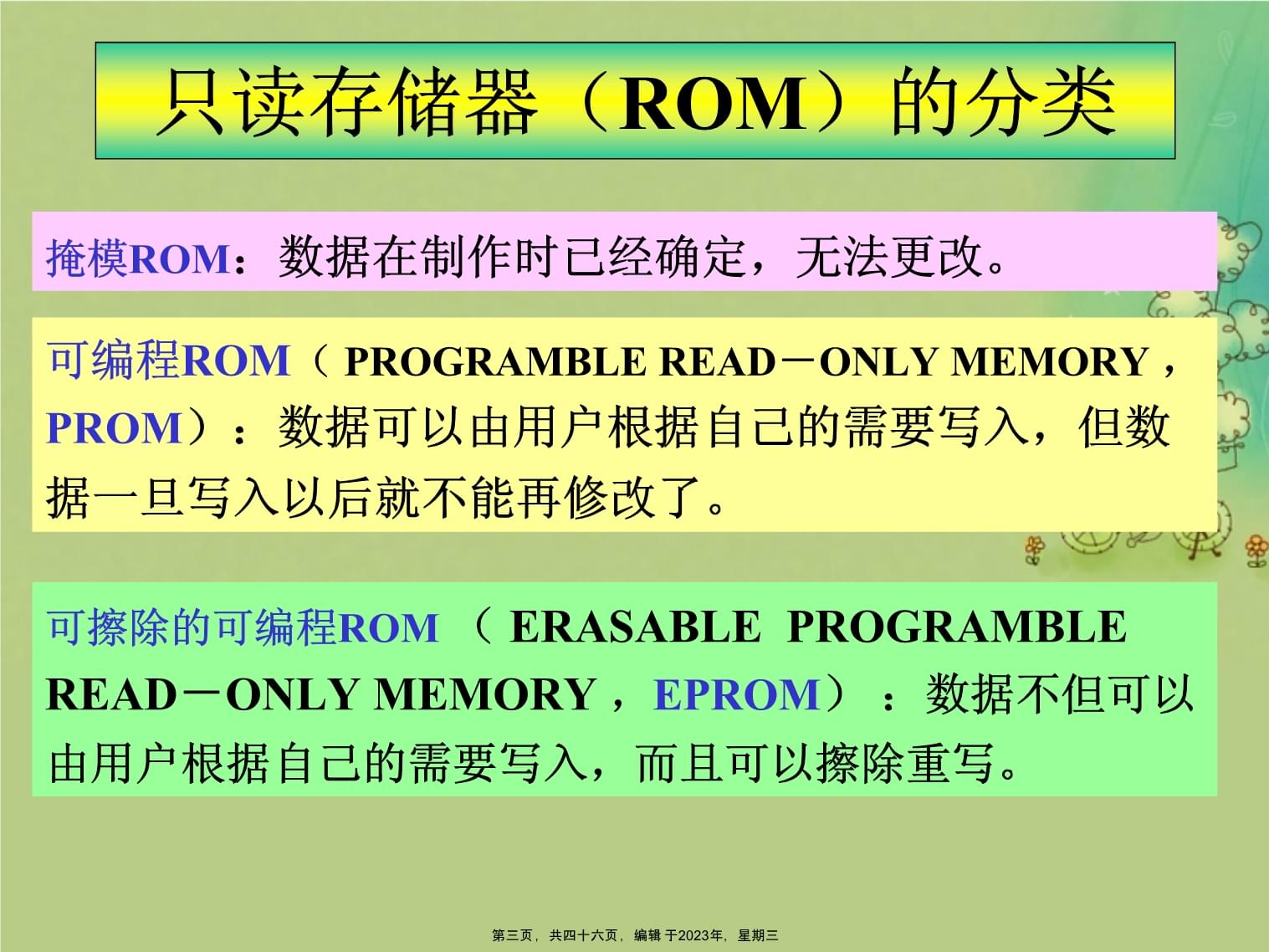

数字系统与逻辑设计第一页,共四十六页,编辑于2023年,星期三半导体存储器的分类只读存储器在正常工作时,它存储的数据是固定不变的,只能从中读取数据,不能快速地随时修改或重新写入数据。只读存储器的优点:电路结构简单,断电以后数据不会丢失。只读存储器的缺点:只适用于存储固定数据的场合。按存取功能分为:只读存储器(READ-ONLYMEMORY,ROM)和随机存取存储器(RANDOM-ACCESSMEMORY,RAM)第二页,共四十六页,编辑于2023年,星期三只读存储器(ROM)的分类掩模ROM:数据在制作时已经确定,无法更改。可编程ROM(PROGRAMBLEREAD-ONLYMEMORY

,PROM):数据可以由用户根据自己的需要写入,但数据一旦写入以后就不能再修改了。可擦除的可编程ROM(ERASABLEPROGRAMBLEREAD-ONLYMEMORY

,EPROM)

:数据不但可以由用户根据自己的需要写入,而且可以擦除重写。第三页,共四十六页,编辑于2023年,星期三随机存储器(RAM)随机存储器在正常工作状态下,可以随时向存储器里写入数据或从中读取数据。随机存储器根据所采用存储单元工作原理的不同分为:静态存储器(STATICRANDOM-ACCESSMEMORY,SRAM):存取速度比DRAM快。动态存储器(DYNAMICRANDOM-ACCESSMEMORY,DRAM):集成度远高于SRAM。第四页,共四十六页,编辑于2023年,星期三7.2只读存储器(ROM)7.2.1掩模只读存储器掩模ROM中存储的数据由制作过程中使用的掩模板决定。掩模板是按照用户的要求而设计的,因此掩模ROM在出厂时内部的数据就已经“固化”在里边了。

第五页,共四十六页,编辑于2023年,星期三二极管ROM的电路结构地址线字线位线(数据线)二极管译码器(与阵列、地址译码器)存储矩阵(或阵列)第六页,共四十六页,编辑于2023年,星期三二极管ROM的电路结构001000010100101100100001010100101101101001110101101001110地址数据A1A0D3D2D1D0000110110101101101001110或阵列有二极管表示存储’1’与阵列第七页,共四十六页,编辑于2023年,星期三二极管ROM的电路结构地址数据A1A0D3D2D1D0000110110101101101001110字线和位线的每个交叉点是一个存储单元。交叉点处接有二极管的相当于存‘1’,没有二极管的相当于存‘0’。存储器的容量(存储单元的数目)=字数位数第八页,共四十六页,编辑于2023年,星期三掩模ROM的结构存储矩阵由许多存储单元排列而成。存储单元:MOS管或双极型三极管每个存储单元存放一位二值代码(0或1)。每一个或一组存储单元有一个对应的地址代码。第九页,共四十六页,编辑于2023年,星期三掩模ROM的结构地址译码器:将输入的地址代码译成相应的控制信号,利用这个控制信号从存储矩阵中把指定的单元选出来,并把其中的数据送到输出缓冲器输出缓冲器:提高存储器的带负载能力,实现对输出状态的三态控制,以便与系统的总线连接。第十页,共四十六页,编辑于2023年,星期三ROM的阵列框图第十一页,共四十六页,编辑于2023年,星期三ROM的阵列框图地址数据A1A0D3D2D1D0000110110101101101001110圆点表示存储器件m0m1m2m3第十二页,共四十六页,编辑于2023年,星期三MOS管构成的存储矩阵字线与位线的交叉点处接有MOS管的相当于存‘1’,没有MOS管的相当于存‘0’。010001001011地址代码经译码为W0~W3中某一条线上的高电平,使接在这根线上的MOS管导通,并使与这些MOS管相连的位线为低电平,经缓冲器后输出为高电平。截止截止截止导通第十三页,共四十六页,编辑于2023年,星期三7.2.2可编程只读存储器(PROM)熔丝用很细的低熔点合金或多晶硅导线制成。编程时给需要存入‘0’的那些单元加上比正常工作电流大得多的电流,这些单元的熔丝就象保险丝一样被烧断,使对应的晶体管的发射极与位线断开,则存储的内容就由‘1’变成了‘0’,而熔丝没有被烧断的那些单元仍然存储‘1’,这样就实现了对PROM的编程。熔丝烧断后不可恢复,因此,PROM只能一次编程。第十四页,共四十六页,编辑于2023年,星期三7.2.2可擦除的可编程只读存储器(EPROM)一、EPROM(UVEPROM)紫外线擦除的PROM(Ultra-VioletErasablePROM)浮栅雪崩注入MOS管(Floating-gateAvalance-InjuctionMOS,简称FAMOS管)FAMOS管是一个栅极“浮置”在SiO2层内的P沟道增强型MOS管,当在它的D和S极之间加上比正常工作电压高得多的负电压(一般在-45V左右)时,D极与衬低之间的PN结发生雪崩击穿,耗尽区的电子在强电场的作用下以极高的速度从D极的P+区射出,其中最快的电子穿过SiO2层到达浮栅,被浮栅俘获而成为栅极存储的电荷,这个过程叫做雪崩注入。第十五页,共四十六页,编辑于2023年,星期三一、EPROM(UVEPROM)在栅极获得足够的电荷后,D极和S极之间便形成导电沟道,使FAMOS管导通,相当于在对应的存储单元存入‘1’。由于栅极“浮置”在SiO2层内,与其它部分完全绝缘,因此注入到栅极上的电荷没有放电通路,能长久地保存下来。导通为‘1’,截止为‘0’。用紫外线或X射线照射FAMOS管的栅极氧化层,则SiO2层中会产生电子空穴对,为浮置栅极上的电荷提供泄放通道,使之放电。电荷消失以后,FAMOS管恢复截止状态,对应的存储单元恢复为‘0’,这个过程称为擦除。擦除时间约为20-30分钟。第十六页,共四十六页,编辑于2023年,星期三E2PROM(电可擦除的ROM)在E2PROM的存储单元中使用的是浮栅隧道氧化层MOS管(FloatingTunelOxide,简称Flotox管)。Flotox管是一种N沟道增强型MOS管,它有两个栅极——控制栅Gc和浮置栅Gf,在Gf和漏区之间有一个极薄的氧化层区域,称为隧道区。当隧道区的电场强度大到一定程度(>107V/cm)时,在Gf和漏区之间出现导电隧道,电子可以双向通过,形成电流,称为隧道效应。Flotox管第十七页,共四十六页,编辑于2023年,星期三E2PROM浮置栅存储电荷,存储‘1’。浮置栅放电,存储‘0’。浮置栅存储有电荷,T1截止读出‘1’,否则读出‘0’。导通E2PROM擦除和写入是需要加高电压的,且所需时间较长,因此在系统正常工作状态下,它只能工作在读出状态,作ROM用。第十八页,共四十六页,编辑于2023年,星期三三、快闪存储器(FlashMemory)在快闪存储器中使用的是叠栅MOS管。快闪存储器用雪崩注如入的方式使浮栅充电而存储‘1’,用隧道效应使浮栅放电而存储‘0’。快闪存储器的特点:2、高速,高密度,允许近万次的电擦除和编程。1、片内所有的叠栅MOS管的源极是连在一起的,所以全部存储单元同时被擦除。第十九页,共四十六页,编辑于2023年,星期三7.3随机存储器随机存储器又叫读/写存储器,简称RAM。在RAM工作时可既可以随时从任何一个指定地址取出(读出)数据,也可以随时将数据存入(写入)任何指定地址的存储单元中去。优点:读写方便,使用灵活。缺点:存在数据易失性,一旦断电所存储的数据便会丢失,不利于数据长期保存。按存储单元的特性分为:SRAM:静态随机存储器DRAM:动态随机存储器第二十页,共四十六页,编辑于2023年,星期三7.3.1静态随机存储器(SRAM)一、SRAM的结构和工作原理输入/输出端口片选信号读写控制信号行地址列地址第二十一页,共四十六页,编辑于2023年,星期三存储矩阵:由许多存储单元排列而成,每个存储单元可以存储1位二值数据(0或1),在译码器和读/写控制电路的控制下既可以写入1或0,也可以将所存储的数据读出。一、SRAM的结构和工作原理存储矩阵中的单元个数即存储容量。第二十二页,共四十六页,编辑于2023年,星期三一、SRAM的结构和工作原理行地址译码器:将输入的地址代码的若干位译成某一条字线上的输出高、低电平信号,使连接在这条字线上的一行存储单元被选中。列地址译码器:将输入的地址代码的其余位译成某一条输出线上的高、低电平信号,从字线选中的一行存储单元中再选中1位(或几位),使被选中的单元经读/写控制电路与输入/输出端(I/O)接通,以便对这些单元进行读写操作。第二十三页,共四十六页,编辑于2023年,星期三读/写控制电路:对电路的工作状态进行控制一、SRAM的结构和工作原理片选信号CS的作用:执行读操作,将存储单元里的内容送到输入/输出端上;执行写操作,输入/输出线上的数据被写入存储器;CS=0时RAM的输入/输出端与外部总线接通,RAM处于正常工作状态;CS=1时RAM的输入/输出端呈高阻态,不能与总线交换数据,此时不能对RAM进行读写操作;第二十四页,共四十六页,编辑于2023年,星期三10244位RAM(2114)的结构框图4096个存储单元由地址码指定的四个存储单元中的数据被送到I/O1~I/O4,实现读操作。加到I/O1~I/O4上的数据被写入指定的四个存储单元。从64行存储单元中选中一行。从已选中的一行中选出要进行读/写的4个存储单元。所有I/O端均被禁止,将存储器内部电路与外部连线隔离。第二十五页,共四十六页,编辑于2023年,星期三二、SRAM的静态存储单元静态存储单元在静态触发器的基础上附加门控管而构成,它靠触发器的自保功能存储数据。六管NMOS静态存储单元六管CMOS静态存储单元第二十六页,共四十六页,编辑于2023年,星期三7.3.2动态随机存储器(DRAM)一、DRAM的动态存储单元动态存储单元利用MOS管栅极电容可以存储电荷的原理制成。电路结构可以做得非常简单,因此被普遍应用于大容量、高集成度的RAM中。缺点:由于MOS管栅极电容的容量很小(通常仅为几皮法),且存在漏电流,所以存储在电容上的电荷保存的时间有限,需要及时补充电荷,这种操作称为刷新或再生。第二十七页,共四十六页,编辑于2023年,星期三单管动态存储单元写操作时,字线给高电平,使T导通,位线上的数据通过T被存入CS中。读操作时,字线仍然给高电平,使T导通。CS通过T向位线上的电容CB提供电荷,使位线获得读出的信号电平。设CS上原来存有正电荷,电压vCS为高电平,而位线电位vB=0,则执行读操作后位线电平vB上升为:实际存储器的位线上总是同时接有很多存储单元,使CB>>CS,因此位线读出的电压信号很小。而且CS上的电压也会下降很多,因此是一种破坏性读出。第二十八页,共四十六页,编辑于2023年,星期三二、灵敏恢复/读出放大器灵敏恢复/读出放大器的作用:1、将读出信号放大。2、将存储单元里原来存储的信号恢复。灵敏恢复/读出放大器每次读出数据的同时完成对存储单元原来所存数据的刷新。第二十九页,共四十六页,编辑于2023年,星期三三、DRAM的总体结构地址分时从同一组引脚输入输入地址代码A0~A7进行读操作输入地址代码A8~A15行地址译码器的输出从存储矩阵1和2中各选一行存储单元,由A7从两行中选出一行,列地址译码器的输出从256列中选中一列。进行写操作第三十页,共四十六页,编辑于2023年,星期三7.4存储器容量的扩展7.4.1位扩展方式适用于字数够用而位数不够的情况每个I/O端作为整个RAM输入/输出数据端的一位。方法:将所有的地址线、R/W、CS分别并联起来。ROM的位扩展方法与此相同扩展后容量为10248第三十一页,共四十六页,编辑于2023年,星期三7.4.2字扩展方式适用于位数够用而字数不够的情况A9A8=00时选中RAM(1),其地址为0-255A9A8=01时选中RAM(1),其地址为256-511扩展后容量为10248保证任何时候只有一个CS有效。任何时候只有一个CS有效,因此输出端可以并联。第三十二页,共四十六页,编辑于2023年,星期三7.5用存储器实现组合逻辑函数地址数据A1A0D3D2D1D0000110110101101101001110在ROM的数据表中,如果将输入地址A1、A0看成两个输入逻辑变量,而将数据输出D3、D2、D1、D0看成一组输出逻辑变量,则D3、D2、D1、D0就是A1、A0的一组逻辑函数,ROM的数据表就是这一组多输出组合逻辑函数的真值表,因此该ROM可以实现表中的四个函数(D3、D2、D1、D0),其表达式为:第三十三页,共四十六页,编辑于2023年,星期三7.5用存储器实现组合逻辑函数从ROM结构来看,其地址译码器形成了输入变量的全部最小项,即每一条字线对应输入地址变量的一个最小项,而每一位数据输出又都是若干个最小项之和,因此任何形式的组合逻辑函数均可以通过向ROM中写入相应的数据来实现。用具有n位输入地址,m位数据输出的ROM可以获得一组最多m个的任何形式的n变量组合逻辑函数,只要根据函数形式向ROM中写入相应的数据来即可。此原理同样适用于RAM第三十四页,共四十六页,编辑于2023年,星期三①根据逻辑函数的输入、输出变量数目,确定ROM的容量,选择合适的ROM。②写出逻辑函数的最小项表达式,画出ROM的阵列图。③根据阵列图对ROM进行编程。用ROM实现逻辑函数的一般步骤第三十五页,共四十六页,编辑于2023年,星期三例7.5.2例7.5.2试用ROM产生如下一组多输出逻辑函数。解:输入变量4个将逻辑函数化为最小项表达式。输出变量4个需要164的ROM第三十六页,共四十六页,编辑于2023年,星期三例7.5.2W0W1W2W3W4W5W6W7W8W9W10W11W12W13W14W15地址译码器(与逻辑阵列)存储矩阵(或逻辑阵列)Y1Y2Y3Y4注意位序第三十七页,共四十六页,编辑于2023年,星期三例7.5.2Y1Y2Y3Y4注意位序第三十八页,共四十六页,编辑于2023年,星期三例7.5.1例7.5.1试用ROM设计一个八段字符显示译码器。数字输入输出DCBAabcdefgh0.1.2.3.4.5.6.7.8.9.00000001001000110100010101100111100010011111110101100001110110111111001101100111101101111011111111100001

1111111111110111аbcdef101010111100110111101111111110100011111000011010011110101101111010001110解:输入变量4个以地址端A3、A2、A1、A0作为BCD代码D、C、B、A的输入端,以数据输出端D0~D7作为a~h的输出端。输出变量8个需要168的ROM。第三十九页,共四十六页,编辑于2023年,星期三例7.5.1接入二极管表示存入0,未接二极管表示存入1。第四十页,共四十六页,编辑于202

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025至2030年中国三色加液管市场现状分析及前景预测报告

- 企业供应链危机管理与应对

- 考生必读陪诊师考试试题及答案

- 2025至2030年中国万能联动开关箱行业投资前景及策略咨询报告

- 2025至2030年中国一次性便盆行业投资前景及策略咨询报告

- 2025至2030年中国一体化摄录像机数据监测研究报告

- 2025至2030年中国PE足球网数据监测研究报告

- 2025至2030年中国PET耐酸碱遮蔽胶带市场分析及竞争策略研究报告

- 2025至2030年中国IGBT逆变埋弧焊机成套设备行业发展研究报告001

- 2025至2030年中国FR雪花杯行业发展研究报告

- 土方回填施工记录表

- 体育调查问卷

- 公司样品标识卡

- 英语人教新起点(一起)四年级下册-Unit 3 Lesson 2 Travel plans教学设计

- SONYα300α350使用手册

- 冀教版二年级语文下册看图写话专项加深练习题含答案

- 海外专家部分项目简介

- 医疗美容主诊医师备案服务指南

- 集装箱吊装方案(共5页)

- 油浸式变压器工艺文件汇编

- 南方科技大学机试样题练习南方科技大学样卷

评论

0/150

提交评论