版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、电子信息与电气工程学院EDA课程设计设计题目:<< 数字电子时钟>>专业:电子信息工程班级: 姓名: 学号: 数字电子时钟简介数字电子时钟是一利用数字电路来显示秒分时的计时装置,与传统的机械钟相比,具有走时准确,显示直观,无机械传动装置等优点;因而得到广泛应用。随着人们生活水平的不断改善和美化,很多场合都可以看到数字电子时钟,并且已成为人们生活中必不可少的一部分,最常见比如电子手表,电子闹钟,万年历,手机时钟数字电子时钟设计任务本设计以KX-DN系列综合实验开发板系统开发实验,通过verilog语言编写各个功能模块,并且经过精确仿真修改达到理想状态,最后连接各个功能模块

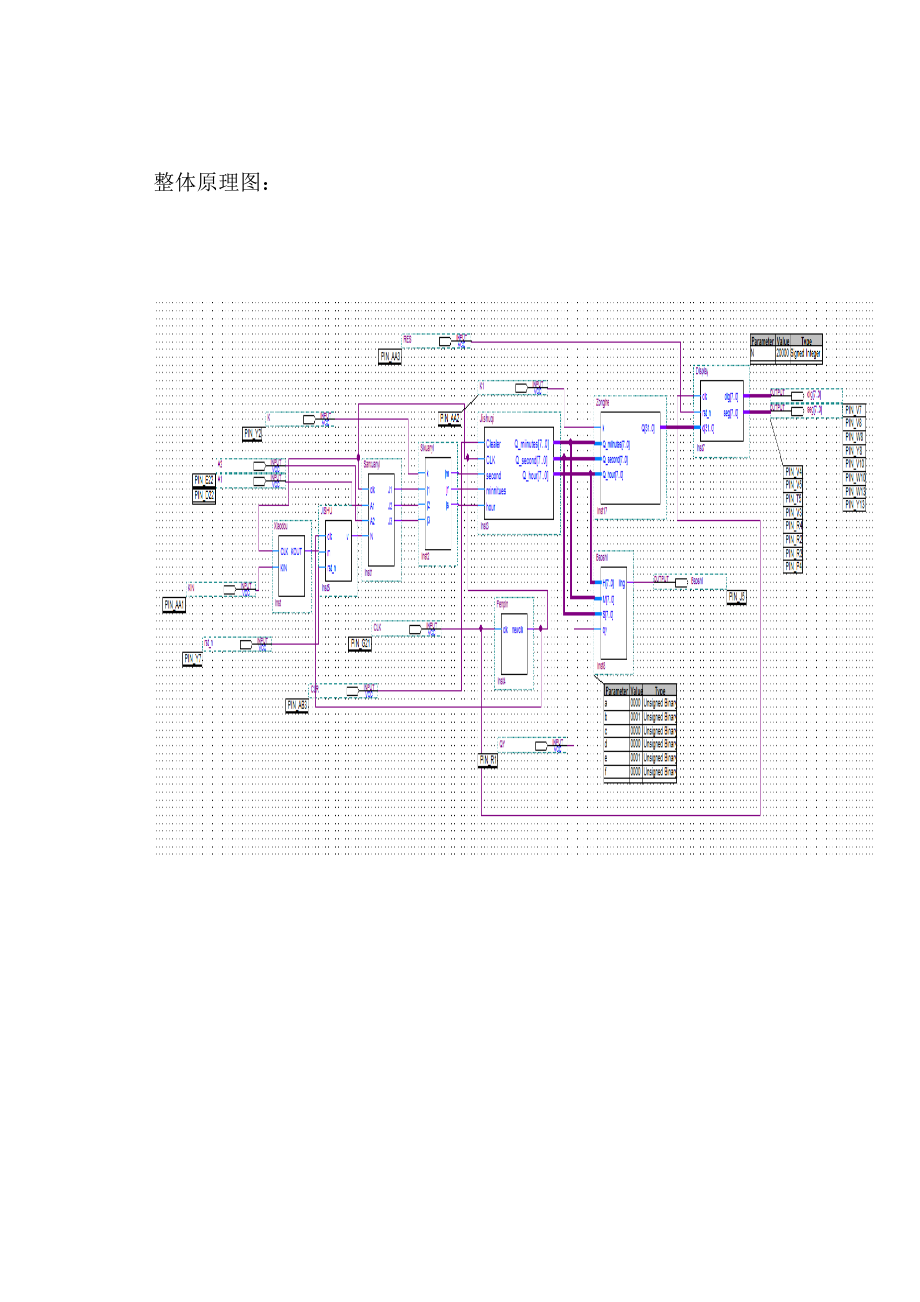

2、组成一个完整的数字电子时钟电路。本设计不仅能够精确显示时分秒(为了起到直观、简洁、美化的作用,我们用“”区分),而且能通过开发板上的按键来控制改变时、分、秒的功能,大大方便了用户的校时、校分、校秒,大大增加数字电子时钟实用性。该时钟还有一键清零(复位清零)的功能,可以防止因外界、内因而导致的时钟计数错误,然后再通过校时、校分、校秒的功能来进行调整时间。最后还能通过开发板上的蜂鸣器来进行整点报时,这一点对这个设计来说是最具人性化的。我们可以按照自己的意愿来进行调整时间报时,已达到个性化设计。一、总体设计方案设计原理及思路原理图如下:数码管显示模块 分频模块 四选一多路选择器 计数器模块24进制计

3、数器60进制计数器60进制计数器整点报时模块四选三多路选择器计数器模块去抖动模块数字钟实际上就是对1Hz的频率进行计数的计数电路。振荡器产生32768Hz的时钟信号,经过分频器后产生512Hz、64Hz、2Hz的脉冲信号,秒计数器计满60后,触发分计数器,分计数器计满60后,触发计时电路,当计满24小时后开始下一轮计数。如果计数的起始时间与设想的有误差,可以通过调时、调分按键或复位键进行手动调时。计数器的输出经过4选1多路选择器后以动态扫描方式送到LED数码管输出。由框图可知程序模块可分为消抖模块、2分频、60进制计数器、24进制计数器、4选3多路选择器、七段译码器、位选端控制器组成。整体原理

4、图: 二 各模块说明2.1消抖模块2.1.1消抖模块原理按键开关是各种电子设备不可或缺的人机接口。在实际应用中,很大一部分的按键是机械按键。在机械按键的触点闭合和断开时,都会产生抖动,为了保证系统能正确识别按键的开关,就必须对按键的抖动进行处理。为了消除机械开关的抖动,可在开关与输出端点之间接人一个RS触发器,就能使输出端产生很清晰的阶跃信号。2.1.2消抖模块程序代码module Xiaodou (CLK, KIN,KOUT); input CLK, KIN; /工作时钟和输入信号 output KOUT; reg KOUT; reg 3:0 KH,KL; /定义对高电平和低电平脉宽计数之寄

5、存器。 always (posedge CLK) begin if (!KIN) KL<=KL+1 ; /对键输入的低电平脉宽计数 else KL<=4'b0000; end /若出现高电平,则计数器清0 always (posedge CLK) begin if (KIN) KH<= KH+1; /同时对键输入的高电平脉宽计数 else KH<=4'b0000; end /若出现高电平,则计数器清0 always (posedge CLK) begin if (KH > 4'b1100) KOUT<=1'B1; /对高电平脉

6、宽计数一旦大于12,则输出1 else if (KL > 4'b0111) KOUT<=1'B0; /对低电平脉宽计数若大于7,则输出0 end endmodule仿真波形:2.2四选一多路选择器2.2.1四选一多路选择器原理该四选一多路选择器没有进位端,用于四选一多路选择器的输入,控制其输出计时器的计时信号。同时它也作为位选端控制器的输入,决定哪个数码管亮。四选一多路计数器采用时序逻辑电路,从0开始计时到3后归零,重新进行开始计时。2.2.2四选一多路选择器程序代码module Zonghe(k,Q_miinutes,Q_second,Q_hour,Q); inp

7、ut k; input7:0 Q_second,Q_miinutes,Q_hour; output reg 31:0 Q; always begin Q31:24=Q_hour; Q23:20=4'ha; Q19:12=Q_miinutes; Q11:8=4'ha; Q7:0=Q_second; end endmodule仿真波形2.3 2分频2.3.1 2分频原理该模块用于产生秒计数脉冲。2分频即在每一个输入脉冲的上升沿(或下降沿)取反即可得到。2.3.2 2分频程序代码module Fenpin(clk,newclk); input clk; output reg newc

8、lk;reg24:0 cnter; always (posedge clk) begin if(cnter<20000000) cnter=cnter+1; else cnter=0; if (cnter<10000000) newclk=1; else newclk=0; end endmodule仿真波形:2.4六十进制计数器2.4.1六十进制计数器原理六十进制计数器作为秒计数器和分计数器的低位,具有进位输出端和异步复位端,复位信号为高电平有效。它要求从0到59计数,到五十九清零重新计数。采用时序逻辑电路。设计时应考虑计数器能够进行级联。2.4.2六十进制计数器程序代码modu

9、le Count60(clrn,clk,q,j,cont); input clrn,clk,j; output reg 7:0 q; output reg cont; always (posedge clkj or negedge clrn) begin if(clrn) q=1'b0; else begin if(q=8'b0101_1001) q=1'b0; else q=q+1'b1; if(q3:0=4'b1010) begin q3:0=4'b0;q7:4=q7:4+1'b1; end if(q=8'b0101_1001

10、) cont=1; else cont=0; end end endmodule 仿真波形:2.5二十四进制计数器(含进位端)2.5.1二十四进制计数器(含进位端)原理该二十四进制计数器作为秒计数器和分计数器的高位, 具有进位输出端和异步复位端,复位信号为高电平有效。它要求从0到23计数,到23清零重新计数。采用时序逻辑电路。设计时应考虑计数器能够进行级联。2.5.2二十四进制计数器(含进位端)程序代码module count24(clrn,clk,q,j,cont); input clrn,clk,j; output reg 7:0 q; output reg cont; always (p

11、osedge clkj or negedge clrn) begin if(clrn) q=0; else begin if(q='h23) q=0; else q=q+1; if(q3:0='ha) begin q3:0=0;q7:4=q7:4+1; end if(q='h23) cont=1; else cont=0; end end endmodule仿真波形:2.6四选一多路选择器2.6.1四选一多路选择器原理四选一多路选择器通过四进制计数器的输出信号控制实现了对计数器产生的脉冲信号的选择性输出。加入此模块是为了实现数码管的动态扫描输出。四选一多路选择器的输入是

12、一个二位二进制数,输出是计时器、计分器、计秒器的高位或低位。2.6.2四选一多路选择器程序代码module Sixuanyi(k,jm,jf,js,j1,j2,j3); input k,j1,j2,j3; output reg jm,jf,js; always begin if(k=0) jm,jf,js=j1,j2,j3; else; end endmodule仿真波形:2.7三选一多路选择器2.7.1三选一多路选择器原理三选一多路选择器通过三进制计数器的输出信号控制实现了对计数器产生的脉冲信号的选择性输出。加入此模块是为了实现数码管的动态扫描输出。三选一多路选择器的输入是一个三进制数,输出

13、是计时器、计分器、计秒器的高位或低位。2.7.2三选一多路选择器程序代码module Sanxuanyi(clk,A1,A2,N,J1,J2,J3);input clk,A1,A2,N;output reg J1,J2,J3; always begin case (A1,A2) 0:J1=N; 1:J2=N; 2:J3=N; default :J1=N; endcase end endmodule仿真波形:2.8七段译码器2.8.1七段译码器原理七段译码器是对输入的信号对应的位置进行编码,使其能显示出输入的数的值。本文所介绍的译码器将小数点dp通过位拼接符将其与计数器的计数值组合,然后一同给到

14、译码管,便于输出。计时器低位的小数点要求常亮,即dp=1;计分器的低位小数点要求以1Hz的频率闪烁,可以让它以2分频的输出为值。2.8.2七段译码器程序代码module Display( clk ,rst_n,d,dig ,seg);input clk ; /20MHzinput rst_n ; /复位信号,低电平有效input 31:0 d; /要显示的32位数据output 7:0 dig ; /位选信号output 7:0 seg; /段码dp到a由高到低排列parameter N= 20000; /分频系数reg clkout ; /扫描时钟reg 13:0cnt; /分频计数器reg

15、 2:0 scan_cnt ; /扫描计数器 reg 3:0 disp_dat ; /每一位数码管待译码数据reg 7:0 dig;reg 7:0 seg_r;always ( posedge clk or negedge rst_n) /分频到1KHzbegin if (!rst_n)cnt <= 0 ;else begin if(cnt= N/2-1)beginclkout <= clkout; cnt<=0;end else cnt<=cnt+1'b1; endendalways (posedge clkout or negedge rst_n) /产生扫

16、描计数值 begin if (!rst_n) scan_cnt <= 0 ; else scan_cnt <= scan_cnt + 1'b1; endalways ( scan_cnt,d) /8位数码管位选择,同时送相应要显示数据begin case ( scan_cnt )3'b000 : begin dig<= 8'b0000_0001;disp_dat<= d3:0; end3'b001 : begin dig<= 8'b0000_0010;disp_dat<= d7:4; end3'b010 : b

17、egin dig<= 8'b0000_0100;disp_dat<= d11:8; end3'b011 : begin dig<= 8'b0000_1000;disp_dat<= d15:12; end3'b100 : begin dig<= 8'b0001_0000;disp_dat<= d19:16; end3'b101 : begin dig<= 8'b0010_0000;disp_dat<= d23:20; end3'b110 : begin dig<= 8'b

18、0100_0000;disp_dat<= d27:24; end3'b111 : begin dig<= 8'b1000_0000;disp_dat<= d31:28; end default : begin dig<= 8'b0000_0001;disp_dat<= d3:0; end endcaseendalways ( disp_dat ) /共阳极数码管译码begin case (disp_dat) 4'h0 : seg_r = 8'hc0; /显示"0" 4'h1 : seg_r = 8

19、'hf9; /显示"1" 4'h2 : seg_r = 8'ha4; /显示"2" 4'h3 : seg_r = 8'hb0; /显示"3" 4'h4 : seg_r = 8'h99; /显示"4" 4'h5 : seg_r = 8'h92; /显示"5" 4'h6 : seg_r = 8'h82; /显示"6" 4'h7 : seg_r = 8'hf8; /显示"

20、;7" 4'h8 : seg_r = 8'h80; /显示"8" 4'h9 : seg_r = 8'h90; /显示"9" 4'ha : seg_r = 8'hbf; /显示"a" /*4'hb : seg_r = 8'h83; /显示"b" 4'hc : seg_r = 8'hc6; /显示"c" 4'hd : seg_r = 8'ha1; /显示"d" 4'h

21、e : seg_r = 8'h86; /显示"e" 4'hf : seg_r = 8'h8e; /显示"f"*/ default: seg_r = 8'hff;/灭 endcaseendassign seg=seg_r; /取反变成共阴极段码endmodule2.9整点报时模块2.9.1整点报时模块程序代码module Baoshi(H,M,S,qy,ling);input 7:0 H,M,S;input qy;output ling;reg bshi;reg ling;parameter a=4'b0000,b=

22、4'b0001,c=4'b0000,d=4'b0000,e=4'b0001,f=4'b0000;always(H or M or S or qy)beginif(H,M,S=24'b000000010000000000010000)ling<=qy;elseling<=0;endendmodule2.10综合模块2.10.1综合模块原理综合模块采用模块例化的方法实现。2.10.2综合模块程序代码module Zonghe(k,Q_miinutes,Q_second,Q_hour,Q); input k; input7:0 Q_second,Q_miinutes,Q_hour; output reg 31:0 Q; a

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025年临床执业医师考试外科学试题及答案

- 临床执业医师考试教育学试题及答案

- 2025年公共营养师考试考点归纳试题及答案

- 2025年育婴师考试资料系统性试题及答案

- 企业人力资源战略对接试题及答案

- 信息技术对图书馆的影响试题及答案

- 人力资源管理师考试学习方向试题及答案

- 2025年公共营养师报考条件与流程试题及答案

- 01《初识“WPS文字”》四年级信息技术教学设计 苏科版

- 2024年心理咨询师理论基础题型分析试题及答案

- GB/T 17207-2012电子设备用固定电容器第18-1部分:空白详细规范表面安装固体(MnO2)电解质铝固定电容器评定水平EZ

- 国开电大《人员招聘与培训实务》形考任务4国家开放大学试题答案

- 临时用电现场安全检查表

- 猪营养体系课件

- 青少年模拟法庭剧本(敲诈勒索)

- 中考复习确定二次函数的解析式课件

- 万用表校准报告

- 模板支撑体系拆除申请表

- 公司金融课件(完整版)

- 地铁盾构法施工技术试题

- 高处作业审批表

评论

0/150

提交评论