版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、5-1 概述概述5-2 时序逻辑电路的分析方法时序逻辑电路的分析方法5-3 若干常用的时序逻辑电路若干常用的时序逻辑电路5-4 时序逻辑电路的设计方法时序逻辑电路的设计方法反馈电路将存储电路的输出状态反馈到组合逻辑电路的输入端,与输入信号一起共同决定电路的输出。时序逻辑电路的特点时序逻辑电路的特点1、功能特点、功能特点而且取决于上一个时刻的输出状态。具备这种逻辑功能特点的电路叫做时序逻辑电路(简称时序电路)。包含组合逻辑电路和存储电路;包含反馈电路。任一时刻的输出信号不仅取决于此时刻的输入信号,2、电路特点、电路特点时序电路以触发器作为基本单元,使用门电路加以配合,完成特定的时序功能。若电路中

2、所有的触发器都由同一时钟脉冲控制,则称为同步时序电路,否则称为异步时序电路。v 重点讲同步时序逻辑电路的分析方法。v 同步时序电路:构成电路的每块触发器的时钟脉冲来自同 一个脉冲源,同时作用在每块触发器上 。v 异步时序电路:构成电路的每块触发器的时钟脉冲来自不同的脉冲源,作用在每块触发器上的时间也不一定相同。 一、同步时序逻辑电路的分析步骤一、同步时序逻辑电路的分析步骤1、写输出方程(输出输入)2、写驱动方程(触发器输入输入)3、写状态方程(触发器的次态初态、触发器输入)4、填状态转换表5、画状态转换图6、画时序波形图7、分析其功能8、检查自启动二、举例二、举例 1.试分析下图时序电路的逻辑

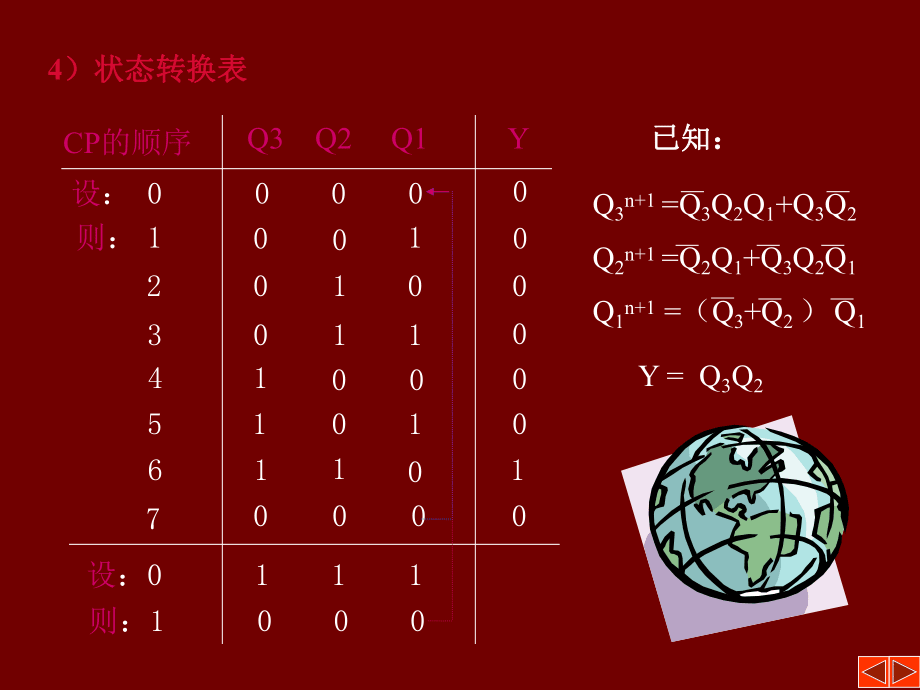

3、功能。解:1)输出方程Y = Q3Q22)驱动方程J3 = Q2Q1 ;J1 = Q3Q2 ; K2 = Q3 Q1 3) 状态方程=Q3Q2 Q1 =Q2Q1+Q3Q2Q1=Q3Q2Q1+Q3Q2Q1n+1 = J1Q1+K1Q1Q2n+1 = J2Q2+K2Q2Q3n+1 = J3Q3+K3Q3 K1 = 1J2 = Q1 ;K3 = Q2=(Q3+Q2 ) Q1Q3Q2Q1YCP1J1K1J1K 1J1K&1&Q3Q2Q1C1C1C1&4)状态转换表)状态转换表CP的顺序Q3 Q2 Q1Y 设: 0 0 0 0 设:0 1 1 1 则:1 0 0 0Q1n+1Q2

4、n+1Q3n+1 =Q2Q1+Q3Q2Q1=Q3Q2Q1+Q3Q2=(Q3+Q2 ) Q1Y = Q3Q2 则: 100120103011410051016110000000170000已知:已知:5)状态转换图)状态转换图000001010011100101110111/0/1Q3Q2Q1/Y/0/0/0/0/0/16) 时序图时序图CPtQ3tYtQ2t7、分析电路的功能、分析电路的功能 8、检查自启动、检查自启动由状态转换表知,此电路能自启动。1 2 3 4 5 6 7Q1t随CP的输入,电路循 环输出七个稳定状态,所以是七进制计数器。Y端的输出是此七进制 计数器的进位脉冲。110000

5、输入变量/输出变量2.试分析如图所示时序逻辑电路的功能并检查电路能否自启动。 1J1KC11J1KC11Q0QCPXZ=1=1=1&FF1FF011(1)写输出方程 nnQQXZ01)((2)写驱动方程 nQXJ1010KnQXJ0111K(3)写状态方程 将各驱动方程代入JK触发器的特性方程 ,得各触发器的状态方程: nnnQKQJQ1nnnnnQQXQKQJQ01000010)(nnnnnQQXQKQJQ10111111)((4)列状态转换表 由于输入控制信号X可取1,也可取0,所以分两种情况列状态转换表和画状态图。 当X=0时: 将X=0代入输出方程和状态方程,则 nnQQZ01

6、nnnQQQ01110110nnnQQQ当X=1时。 将X=1代入输出方程和状态方程,则 nnQQZ010111nnnQQQnnnQQQ0110根据以上两种情况,我们可以列出状态转换表(设现态为 )0001nnQQ (5)画状态图 根据状态表,我们很容易画出该电路的状态转换图。偏离状态(6)画时序波形图 1Q0QXCPZ游离于主循环的状态称为偏离状态,进入任一偏离状态都可返回主循环时,称该电路具有自启动特性。(7)逻辑功能分析 该电路一共有3个循环状态00、01、10。当X=0时,按照加1规律从00011000循环变化,并每当转换为10状态(3个循环状态中的最大数)时,输出Z=1;当X=1时,

7、按照减1规律从10010010循环变化,并每当转换为00状态(3个循环状态中的最小数)时,输出Z=1。所以该电路是一个可控3进制计数器。当X=0时,作加法计数,Z=1是进位信号;当X=1时,作减法计数,Z=1是借位信号。 (8)检查电路的自启动情况 从状态表或状态图中可以看出,若电路的现态为有效循环以外的状态11,则随着时钟的输入,电路的次态为00,能自动进入主循环。所以,该电路可以自启动。 1 1Q2 Q1 Q0 JC K JC K JC KSDCPCP Q2 Q1 Q00123456781 1 1 1 1 11 1 11 1 11 1 01 1 0 1 0 11 0 11 0 01 0 0

8、0 1 10 1 10 1 00 1 00 0 10 0 10 0 00 0 01 1 11 1 1J0 = K0 = 1 1J1 = K1= Q0J2 = K2= Q1 Q0 结论:结论:减法计数器。减法计数器。例题例题 分析电路的逻辑功能。分析电路的逻辑功能。下一页下一页上一页上一页下一节下一节返返 回回上一节上一节5.2.3异步时序逻辑电路的分析异步时序逻辑电路的分析 与同步时序逻辑电路不同的是,异步电路中,每次电路状态发生转换时并不是所有触发器都有时钟信号。只有那些有时钟信号的触发器才需要用特性方程去计算次态,而没有时钟信号的触发器将保持原来的状态不变。例例:试分析如图所示的时序逻辑电

9、路的功能并检查电路能否自启动。 C1FF01D1FFC11DCP0QQ1Z&解解: 由于在异步时序逻辑电路中,没有统一的时钟脉冲,因此,分析时必须写出时钟方程。 (1)写各时钟方程 CP0=CP(时钟脉冲源的上升沿触发)CP1=Q0(当FF0的Q0由01时,Q1才可能改变状态,否则Q1将保持原状态不变) (2)写输出方程 (3)写各触发器的驱动方程 nQD00nQD11(4)写各触发器的次态方程 将各驱动方程代入D触发器的特性方程 ,得: DQn1C1FF01D1FFC11DCP0QQ1Z&nnQDQ0010(CP由01时此式有效) 1111nnQDQ(Q0由01时此式有效)

10、(5)列状态转换表 nQ1nQ011nQ10nQ现态次态输出时钟脉冲 ZCP1 CP00 01 11 00 11 11 00 1 0 01000 0 0 (6)画状态转换图和时序波形图 (7)逻辑功能分析由状态图可知:该电路一共有4个循环状态00、01、10、11,在时钟脉冲作用下,按照减1规律循环变化,所以这是一个4进制减法计数器,Z=1是借位信号。电路可以自启动。K0 = 1 1J1 = 1 1 K1= 1 1J0 = Q2J2 = Q1Q0K2 = 1 1例题例题 分析电路的逻辑功能。分析电路的逻辑功能。下一页下一页上一页上一页下一节下一节返返 回回上一节上一节CPQ2 Q1 Q0012

11、345J2 K2 J1K1 J0K00 0 0 0 0 01 11 11 11 11 11 11 10 01 10 0 0 01 10 00 01 10 01 10 01 11 10 01 11 10 00 01 10 00 00 00 00 0 结论:结论: 五进制加五进制加法计数器。法计数器。K0 = 1 1J1 = 1 1 K1= 1 1J2 = Q1Q0K2 = 1 1J0 = Q21 11 11 11 11 11 11 11 11 11 11 11 11 11 11 11 11 11 1下一页下一页上一页上一页下一节下一节返返 回回上一节上一节5-3-1 5-3-1 寄存器和移位寄存

12、器寄存器和移位寄存器5- -3- -2 计数器计数器5-3-3 5-3-3 顺序脉冲发生器顺序脉冲发生器一、寄存器一、寄存器: :用于寄存一组二值代码的逻辑器件(用四块D触发器构成) 若输入:若输入:1 0 0 11 0 0 10 0 0 00 0 0 01 1、电路结构、电路结构 存入:存入: 1 0 0 1 1 0 0 1 2 2、工作原理、工作原理存数指令CPQ0Q1Q2Q3D0D1D2D31DR1DR1DR1DRRD若输入信号 、 、 、 已被送到相应触发器的D端,当CP脉冲来到时,四个触发器的输出端 的电平分别等于端 、 、 、 的电平,这时输入信号就被寄存起来了。只要没有新的输入信

13、号,触发器的状态就不会改变,也就是说,输入信号在寄存器中一直保持到下一个输入信号到达时为止。 0D1D2D3D3210QQQQ、0D1D2D3D每个触发器只能储存1位二值代码,所以4个触发器组成的寄存器能储存一组4位的二值代码。如:1001。同时,这里也有异步置位端,所以,在没有输入脉冲的前提下,也可用它来进行清0。但是,在进行储存数码时,这个异步置位端必须结成无效状态,即接高电平(因为RD为低电平有效。二、二、 移位寄存器移位寄存器:移位寄存器除了具有存储代码的功能以外,还具有移位功能。1、移位电路组成、移位电路组成(从Q3 向Q0移)Q0端是串行输出端;DIL是左移数据输入端;1DC1FF

14、DQ31DC1FFCQ21DC1FFBQ11DC1FFAQ0CPDILQ0Q1Q2Q3 端是并行输出端。2 2、工作过程、工作过程例如:要移入D0D1D2D3移状态表Q0 Q1 Q2 Q3 DIL CP顺序X X X D0 X X D0 D1X D0 D1 D2D0 D1 D2 D3 4个CP过后,D0D1D2D3移入D01D12D23D34利用移位寄存器可以实现代码的串行并行转换,以及并行串行转换。1.串行数据变为并行数据举例:用五个时钟脉冲将串行数据个就各位,用并行取样脉冲开门取数。2.并行转换为串行举例:并行置入时,要先用置0 端将 所有 Q 置0,数据就可以使并行数据与 D 端相连了。

15、当然并行采样信号M=1,即送个脉冲:M4 4、集成移位寄存器、集成移位寄存器74LS19474LS194 1 0 1 右移(向Q3移)1 1 1 并行输入功能表:功能表:RD S1 S0 工作状态 0 x x 清零 1 0 0 保持1 1 0 左移(向Q0移)10 111 1 11 1 11 1 1 11234具体的电路,可参见书本P238图5.3.7。向右移举例:1要想只将一个1右移,操作过程见上:1 0 1 0 0 1 0 0 0 10Q0 Q1 Q2 Q3CPS1S074LS194RDD0 D1 D2 D3DIRDIL4DIR为右移串行输入端, DIL为左移串行输入端,D0D1D2D3为

16、数据并行输入端 Q0Q1Q2Q3 为数据并行输出端,S1S0工作状态控制端。右移等效于2;左移等效于2计数器同步异步二进制十进制任意进制二进制十进制任意进制加法,减法,可逆加法,减法,可逆加法计数器:随cp的输入,电路递增计数减法计数器:随cp的输入,电路递减计数可逆计数器:随cp的输入,电路可增可减计数一、同步计数器一、同步计数器(一) 同步二进制计数器1、同步二进制加法计数器CPT0=1Q0T1Q1T2Q2CQ3T3&C11NC11NC11NC11N&T0=1;T1=Q0;T2=Q1Q0;T3=Q2Q1Q0C=Q3Q2Q1Q0(2) 驱动方程驱动方程(1) (1) 输出方程

17、输出方程(四块T触发器组成)已知:已知:T0=1T1=Q0T2=Q1Q0T3=Q2Q1Q0C=Q3Q2Q1Q0(3)时序波形图时序波形图Q0tQ1tQ2tQ3t1 2 3 4 5 67 8 910 11 1213 14 1516CPtCt(4) 状态转换情况状态转换情况 (在波形图上读)000000010010001101001110111110000(5) 分析功能分析功能这是十六进制计数器(也是四位二进制加法计数器)计数容量为24-1=152、集成四位二进制加法计数器、集成四位二进制加法计数器74LS16174LS161Q 1、Q 2、Q 3 端分别为四分频、八分频和十六分频端。Q0端为二

18、分频端。则,Q0端输出脉冲的频率为1/2f 若CP的频率为f 计数器的另一个作用是分频:同理:Q3 Q2 Q1 Q0CCPEPET74LS161RDLD D3 D2 D1 D0逻辑符号逻辑符号CP:时钟输入端EP、ET:功能转换端C:进位输出端RD:复位端LD:预置数的控制端D3D2D1D0:预置数的输入端功能表:3、同步二进制减法计数器、同步二进制减法计数器10 0 0 0RD 端 LD 端功能的区别:0工作特点:随CP的不断输入,电路递减计数。CPRDLDEP ET工作状态0XXX X置零01X X预置数X110 1保持X11X 0保持(但C=0)111 1计数Q3 Q2 Q1 Q0CCP

19、EPET74LS161RDLD D3 D2 D1 D0X X X X01Q3 Q2 Q1 Q0CCPEPET74LS161RDLD D3 D2 D1 D0X X X XX X X X0例如:0 0 1 10 0 1 1工作原理:只有当第j 位以下的各位均为0时,再减1才能使此位翻转。也就是说,把同步二进制加法计数器中相应的Q换作Q即可。这里就不再具体介绍了4、四位二进制可逆计数器、四位二进制可逆计数器74LS19174LS191逻辑符号逻辑符号(二)(二) 同步十进制计数器同步十进制计数器集成同步十进制加法计数器有74LS160。电路框图、功能表 和74LS161相同,但输出只有0000100

20、1十个稳定状态。集成同步十进制可逆计数器有74LS190。电路框图、功能表和74LS191相同。功能表功能表1X1X保持0XX预置数010加法计数011减法计数CPISLDU/D 工作状态XQ3 Q2 Q1 Q0C/BCPI74LS191LD D3 D2 D1 D0CPOU/DSS=0,C/B=1时,CPO=CPI进位输出函数C=Q3Q0状态转换图见下页同样,十进制减法计数器在电路上稍加修改,然后只要将加法中的Q换为Q即可。74LS16074LS160的状态转换图的状态转换图(Q3Q2Q1Q0 )0000000100100011010001010110011110001001101010111

21、110111111001101C=Q3Q0=1tpdtpd二、异步计数器二、异步计数器1、异步二进制加法计、异步二进制加法计数器数器v构成(以三位为例)v时序图v计数状态 (在时序图上读)1JC11K1JC11K1JC11K1FF0FF1FF2CP0CP1CP2Q0Q1Q20CP0t0Q0t0Q1t0Q2t12345678(CP1) (CP2) tpd2、异步十进制计数器、异步十进制计数器2.异步二进制减法计数器异步二进制减法计数器如果将T触发器之间按二进制减法计数规则连接,就可得到二进制减法计数器。1JC11K1JC11K1JC11K1FF0FF1FF2CP0CP1CP2Q0Q1Q2这里仍然

22、以三位为例,并且仍采用下降沿动作。电路连接图如图所示。时序图参见书本图5.3.29。目前常用的4位异步二进制加法计数器有74LS293、74LS393等只是对异步4位二进制计数器稍加修改。v 功能说明(表1)3、异步二、异步二五五十进制计数十进制计数74LS29074LS290CP输入端进制输出状态分频端CP0Q0二0、1Q0为二分频端CP1Q3Q2Q1五000100Q3为五分频端CP1Q3Q2Q1Q0十00001001Q3为十分频端且Q0与CP1相连输出端&S91S92&R01R02CP1CP0Q0Q1Q2Q3S1JC11KR11JC11KR11JC11KR&FF0F

23、F1FF2FF3S1JC11KRv 功能说明异步置0端RO1 RO2异步置9端S91 S92功能说明1 1X 01 10 1置 00 X1 1X 01 1置 90 00 0计 数(表2)v 逻辑符号CP0CP1Q3Q2Q1Q0R01R02S92S9174LS290v 用作十进制时的连线CP0CP1Q3Q2Q1Q0R01R02S92S9174LS290置 9 端有两个,全高时有效;清零端有两个,全高时有效;置 9 优先,清零次之。计数时两者均应无效。三、任意进制计数器的构成方法三、任意进制计数器的构成方法用 N 进制计数器,构成 M 进制计数器(一)(一) MN 的情况的情况 (用多片N进制计数

24、器组合构成)1 1、连接线路(并行进位方式低位进位作为高位状态选择)、连接线路(并行进位方式低位进位作为高位状态选择)Q3 Q2 Q1 Q0CCPEPET74LS160RDLDD3 D2 D1 D0Q3 Q2 Q1 Q0CCPEPET74LS160RDLDD3 D2 D1 D0CP1Y(1)(2)11例例2 2试用两片74LS160构成百进制计数器。2 2、连接方式与特点、连接方式与特点1)异步CP方式。低位的进位信号是高位的时钟。2)两片的EP、ET恒为1,都处于计数状态。3 3、进制、进制 MM = 1010 = 100高位的C 端是此计数器的进位输出端,进位信号为Y=1。高位、低位各自能

25、输出10个稳定状态:1 1、连接线路、连接线路( (串行进位方式串行进位方式- -低位进位作为高低位进位作为高位时钟)位时钟)为何用非门?Q3 Q2 Q1 Q0CCPEPET74LS160RDLDD3 D2 D1 D0CP1Y(1)(2)Q3 Q2 Q1 Q0CCPEPET74LS160RDLDD3 D2 D1 D01例例3 3 电路如图,试分析电路为几进制计数器,两片之间是几进制。解:解:1 1、连接方式与特点、连接方式与特点异步CP方式。(1)片Y端的进位信号是(2)片的时钟。(1)片是10进制,当两片计数到0001、0011状态时,电路整体清零(称为整体清零法)。Y 端是此计数器的进位输

26、出端,进位信号为Y=1。(即:两片之间是10进制)。0 0 0 00 0 0 0CP1Y(1)(2)Q3 Q2 Q1 Q0CCPEPET74LS161RDLDD3 D2 D1 D0Q3 Q2 Q1 Q0CCPEPET74LS161RDLDD3 D2 D1 D0&11Y &M为素数(不能分解成N1N2)12 2、 计数状态表计数状态表(2)片 (1)片CP顺序 Q3Q2Q1Q0 Q3Q2Q1Q0 状态数190 0 0 00 0 0 0100 0 0 00 0 0 1110 0 0 10 0 0 1120 0 1 00 0 0 112101112130 0 0 0 0 0 0 00

27、 0 0 0 0 0 0 0 00 0 0 11 0 0 1暂态3 3、进制、进制 MM = 10 + 3 = 13 。RD=00 0 0 1 0 0 1 1131414例例4 4电路如图,试分析电路为几进制计数器,两片之间是几进制。解:(1)片的进位信号控制(2)片的使能端,Y 端是此计数器的进位输出端,进位信号为Y=0。两片之间是16进制。当两片计数到0100、0010状态时,电路总体置入0(称为整体置数法)。CPYQ3 Q2 Q1 Q0CCPETEP74LS161RDLDD3 D2 D1 D0Q3 Q2 Q1 Q0CCPETEP74LS161RDLD D3 D2 D1 D01(1)(2)

28、11&同步CP方式。(2)片仅在 ET=EP=C1=1 的时间内计数。1 1、连接方式与特点、连接方式与特点0 1 0 00 0 1 00 0 0 00 0 0 0(2)片 (1)片CP顺序 Q3Q2Q1Q0 Q3Q2Q1Q0 状态数1160 0 0 00 0 0 112170 0 0 0 0 0 0 00 0 0 0 0 0 0 0 00 0 0 10 0 0 0 150 0 0 0161 1 1 1310 0 0 1321 1 1 1 320 0 1 0330 0 0 0 470 0 1 0481 1 1 1 480 0 1 1490 0 0 0 630 0 1 1641 1 1

29、1 640 1 0 0650 0 0 0 67650 1 0 00 0 0 1 660 1 0 00 0 1 0 3 3、进制、进制 M:M = 164 + 3 = 672 2、计数状态表、计数状态表6667LD=05-4-1 同步任意进制计数器的设计同步任意进制计数器的设计要求 :1)用小规模集成电路(触发器和门电路)设计。2)计数器应能自启动3)电路应力求简单例 :设计一个 七进制计数器,要求它的状态转换图如下001100010101011111110Q1Q2Q3/C/0/0/0/0/0/0/1循环输出m1 、m4、m2、m5、m6、m7、m3、七个状态。触发器和门电路数目最少触发器和门电

30、路的输入端数目最少注:当用中、大规模集成电路时,电路最简的标准是使用的集成电路数码最少、种类最少,互相连线也最少。 1、填总的、填总的 次态次态/输出输出卡洛图卡洛图 XXX/X100/0 001/1101/0010/0110/0 011/0111/02、分解卡洛图、分解卡洛图X 1 0 10 1 0 1X 0 0 0 1 1 1 1X 0 1 1 0 0 1 1解:解:循环输出 m1 、m4 、m2、m5、m6、m7、m3、 0 0 0 1 1 1 1 0Q2Q3Q10100 01 11 10Q1Q2Q3Q2n+10100 01 11 10Q1Q2Q3Q1n+10100 01 11 10Q1

31、Q2Q3Q3n+101X 0 1 0 0 0 0 000 01 11 10Q1Q2Q3C01Q1Q2Q3/CC=1如果按常规合并最小项,则:如果将XXX定义为有效循环中的任意一个状态,例如 将XXX定义为010,电路将能自启动。 3、为了自启动,合理确定无关项的次态、为了自启动,合理确定无关项的次态此时,最小项的合并如图。X 1 0 10 1 0 1X 0 0 0 1 1 1 1X 0 1 1 0 0 1 100 01 11 10Q1Q2Q3Q2n+10100 01 11 10Q1Q2Q3Q1n+10100 01 11 10Q1Q2Q3Q3n+101X 0 1 0 0 0 0 000 01 11 10Q1Q2Q3C014、写状态方程、写状态方程和输出方程和输出方程Q1n+1= Q2 Q3Q3n+1= Q2Q2n+1= Q1+Q2Q35、确定触发器的类型,写驱动方程、确定触发器的类型,写驱动方程若用JK触发器组成这个电路,就将状态方程化成JK触发器特性方程的标准形式:Q2n+1= Q1(Q2 + Q2) + Q2Q3 = (Q1 + Q3)

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 抵押协议中的争议解决条款

- 商品质量评估合同(2篇)

- 2025年统编版小学道德与法治四年级下册《这些东西哪里来》说课课件

- 定制家具采购信息保密协议

- 建筑维修材料购销合同

- 喷涂设备材料合同

- 养生培训课件

- 快捷宝运营管理案例分析

- 工厂安全知识教学

- 幼儿园教育活动计划的种类

- 预防未成年人犯罪法治教育课件

- 2024年郑州黄河文化旅游发展有限公司招聘笔试真题

- 劳务派遣方案计划书

- 【苏州工学院智能建造研究院】2025中国低空经济产业链全面解析报告

- 浙江省义乌市宾王中学教育集团2024-2025学年九年级3月作业检测道德与法治试题(原卷版+解析版)

- 2025年玉米种子的购销合同

- 2025年甘肃省兰州市政建设集团有限责任公司招聘笔试参考题库附带答案详解

- 2024-2025学年高二下学期《提高效率向时间要成果》主题班会课件

- 城市公园景观设计教学课件

- 智能宠物喂食器与饮水机市场趋势研究

- 初三班级学生中考加油家长会课件

评论

0/150

提交评论