版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、实验六 Verilog设计分频器/计数器电路一、实验目的 1、进一步掌握最基本时序电路的实现方法; 2、学习分频器/计数器时序电路程序的编写方法; 3、进一步学习同步和异步时序电路程序的编写方法。 二、实验内容 1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock周期的高电平),文件命名为fenpinqi10.v。 2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上

2、升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。 3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。 4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法

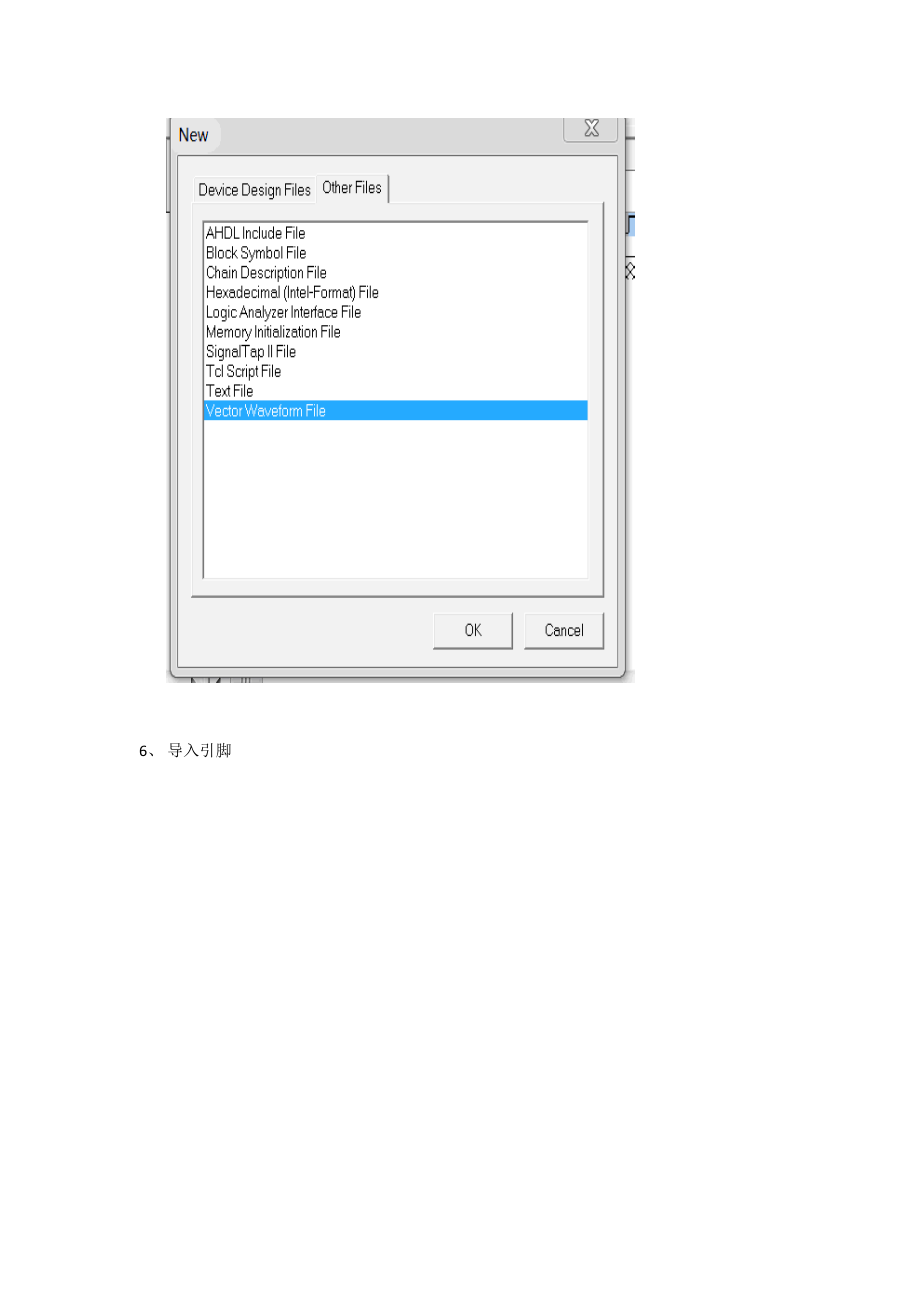

3、计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。 5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q3.0是计数器低4位状态输出端,Q7.0是高4位状态输出端;COUT是进位输出端。三、实验步骤实验一:分频器1、 建立工程1 / 282、 创建Verilog HDL文件3、 输入10分频器程序代码并保存4、 进行综合编译5、

4、 新建波形文件6、 导入引脚7、 设置信号源并保存8、 生成网表9、 功能仿真10、 仿真结果分析由仿真结果可以看出clockout输出5个clock周期的低电平和5个clock的高电平达到10分频的效果,设计正确。实验二:十进制加法计数器(异步清零)1、 建立工程2、 创建Verilog HDL文件3、 输入加法计数器代码并保存4、 进行综合编译5、 新建波形文件6、 导入引脚7、 设置信号源并保存8、 生成网表9、 功能仿真10、 仿真结果分析由仿真结果可以看出异步清除端CLR高电平时,输出Q清零,CLR低电平则Q进行1到9的计数,超过9进位端C为1 ,Q从0 开始重新计数如此循环。因此设

5、计正确。实验三:8位同步二进制加减计数器1、 建立工程2、 创建Verilog HDL文件3、 输入同步8位加减法计数器程序代码并保存4、 进行综合编译5、 新建波形文件6、 导入引脚7、 设置信号源并保存8、 生成网表9、 功能仿真10、 仿真结果分析由仿真波形图可以看出当时钟clock的上升沿到来时,clr为低电平时清零,实现同步复位。当updown为低电平时,计数器做减法操作;当updown为低电平时,计数器做加法操作。所以设计正确。实验四:可变模数计数器1、 建立工程2、 创建Verilog HDL文件3、 输入可变模数计数器程序代码并保存module mcout5_ljj (M1,M

6、0,CLK,out,c,CLR);input M1,M0,CLK,CLR;output c;output5:0out;reg c;reg5:0M,N;reg5:0out;always(posedge CLK or posedge CLR)begin if (CLR) begin out<=0;N<=0; end else begin N<=M; case(M1,M0) 'b00: M<=18; 'b01: M<=4; 'b10: M<=12; 'b11: M<=6; endcase if(N=M) begin if(ou

7、t=(M-1) begin out<=0;c<=c; end else begin out<=out+1; end end else begin out<=0;c<=0; end endendendmodule4、 进行综合编译5、 新建波形文件6、 导入引脚7、 功能仿真11、 仿真结果分析当M1M0=00时波形图,此时为模18的加法计数器当M1M0=01时波形图,此时为模4加法计数器当M1M0=10时波形图,此时为模12加法计数器当M1M0=01时波形图,此时为模6加法计数器实验五:2位十进制计数器1、 建立工程2、 创建Verilog HDL文件3、 输入2

8、位十进制计数器程序代码并保存module counter8 (clk,clr,ena,cout,ql,qh);input clk,clr,ena;output cout;output3:0 ql,qh;reg3:0qh,ql;reg cout;always (posedge clk or posedge clr)begin if(clr) begin qh<=0; ql<=0; cout<=0; end else if(ena) begin ql<=ql+1; if(ql='b1010) begin ql<=0;qh<=qh+1; if(qh='b1010) begin qh<=0; cout<=cou

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 四川省成都市温江区2023-2024学年五年级下学期语文期末试卷(含答案)

- 2025建筑工地材料装卸合同

- 2025上海市物业管理服务合同

- 2025家具购买合同书模板

- 2025标准中介版房屋租赁合同样本

- 2025合作协议:土地项目共同开发合同

- 2025关于地暖系统安装合同书

- 2025销售行业简易劳动合同(参考文本)

- 2025国内劳务合同(5)范文

- 《青少年骨折与关节损伤》课件

- 福建省漳州地区校联考2024-2025学年七年级下学期期中考试语文试卷(含答案)

- 2025年便利店店员劳动合同

- GB/T 196-2025普通螺纹基本尺寸

- 2025年陕西省汉中市宁强县中考一模道德与法治试题(含答案)

- 工地分红合同协议

- 变配电工多选试题及答案

- 零售业智能转型:DeepSeek驱动的消费行为分析与推选系统

- 中华人民共和国农村集体经济组织法

- GB/T 25052-2024连续热浸镀层钢板和钢带尺寸、外形、重量及允许偏差

- 杭州市主城区声环境功能区划分图

- 6G项目实施方案参考模板

评论

0/150

提交评论