下载本文档

版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

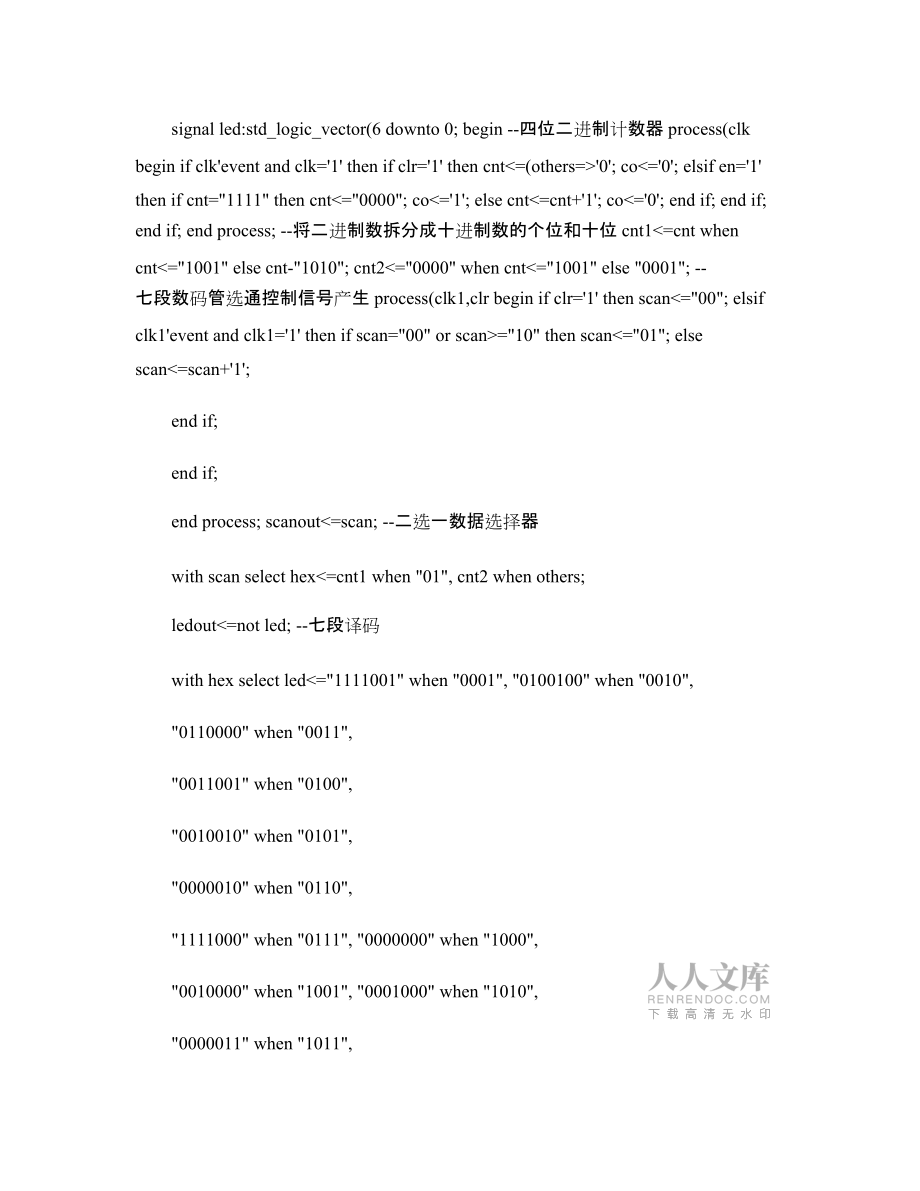

1、1、要求:设计一个四位二进制计数器,将计数结果由数码管显示,显示结果为十进制数。数码管选通为低电平有效,段码为高电平有效。分析:VHDL 描述包含五部分:计数器、将四位二进制数拆分成十进制数的个位和十位、二选一的数据选择器、七段译码、数码管选通控制信号 线定义为信号library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity counter3 is Port ( clk:in STD_LOGIC; clk1 : in STD_LOG

2、IC; clr : in STD_LOGIC; en : in STD_LOGIC; co : out STD_LOGIC; scanout:out std_logic_vector(1 downto 0; ledout:out std_logic_vector(6 downto 0; end counter3; architecture Behavioral of counter3 is signal cnt:std_logic_vector(3 downto 0; signal cnt1:std_logic_vector(3 downto 0; signal cnt2:std_logic_

3、vector(3 downto 0; signal hex:std_logic_vector(3 downto 0; signal scan:std_logic_vector(1 downto 0;enclrsignal led:std_logic_vector(6 downto 0; begin -四位二进制计数器 process(clk begin if clkevent and clk=1 then if clr=1 then cnt0; co=0; elsif en=1 then if cnt=1111 then cnt=0000; co=1; else cnt=cnt+1; co=0

4、; end if; end if; end if; end process; -将二进制数拆分成十进制数的个位和十位 cnt1=cnt when cnt=1001 else cnt-1010; cnt2=0000 when cnt=1001 else 0001; -七段数码管选通控制信号产生 process(clk1,clr begin if clr=1 then scan=10 then scan=01; else scan=scan+1;end if;end if;end process; scanout=scan; -二选一数据选择器with scan select hex=cnt1 w

5、hen 01, cnt2 when others;ledout=not led; -七段译码with hex select led=1111001 when 0001, 0100100 when 0010,0110000 when 0011,0011001 when 0100,0010010 when 0101,0000010 when 0110,1111000 when 0111, 0000000 when 1000,0010000 when 1001, 0001000 when 1010,0000011 when 1011,1000110 when 1100,0100001 when 11

6、01, 0000110 when 1110,0001110 when 1111,1000000 when others;end Behavioral; 2、八位二进制计数器结果有两位七段数码管显示 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; - Uncomment the following library declaration ifinstantiating - any Xilinx primitives in this c

7、ode. -library UNISIM; -use UNISIM.VComponents.all; entity counter8 isPort ( clk:in std_logic; clk1 : in STD_LOGIC;clr : in STD_LOGIC; en : in STD_LOGIC; co : out STD_LOGIC;scanout:out std_logic_vector(1 downto 0; ledout : out STD_LOGIC_VECTOR (6 downto 0; end counter8; architecture Behavioral of cou

8、nter8 is signal cnt:std_logic_vector(7 downto 0; signal hex:std_logic_vector(3 downto 0; signal scan:std_logic_vector(1 downto 0; signal led:std_logic_vector(6 downto 0; begin process(clk begin if clkevent and clk=1 thenif clr=1 thencnt0; co=0;elsif en=1 thenif cnt=11111111 then cnt=00000000;co=1;el

9、secnt=cnt+1;co=0;end if; end if;end if; end process; process(clk1,clr begin if clr=1 then scan=10 then scan=01; else scan=scan+1; end if; end if; end process; scanout=scan; with scan select hex=cnt(3 downto 0 when 01, cnt(7 downto 4 when others; ledout=not led; with hex select led=1111001 when 0001, 0100100 when 0010, 0110000 when 0011, 0011001 when 0100, 0010010 when 0101, 0000010 when 0110, 1111000 when 0111, 0000000 when 1000, 0010000 when 1001,

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 快递员与快递公司劳动合同续签合同

- 2025年中国办公设备及耗材行业市场前景预测及投资价值评估分析报告

- 电商支付接口技术合作开发合同

- 网店平台迁移包含广告投放与推广支持协议

- 艺术表演机构专业演员全职岗位合同

- 股权继承安排与公司治理结构优化合作协议

- 模具制造工艺版权许可补充协议

- 跨国公司员工背景调查保密及合作合同

- 环保设施运营维护大气污染防治责任保证书

- 环保机投放协议书

- 九年级十二班走读生家长会课件

- 国开电大《人员招聘与培训实务》形考任务4国家开放大学试题答案

- 工改工政策分析课件

- 醇基燃料技术资料

- 施工企业资质及承接工程的范围

- 泥浆测试记录表

- 《摩擦力》说课课件(全国获奖实验说课案例)

- 个人信用报告异议申请表

- 初中数学 北师大版 七年级下册 变量之间的关系 用图象表示的变量间关系 课件

- 2023年艺术与审美期末试卷答案参考

- 电气工程竣工验收表格模板

评论

0/150

提交评论