版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

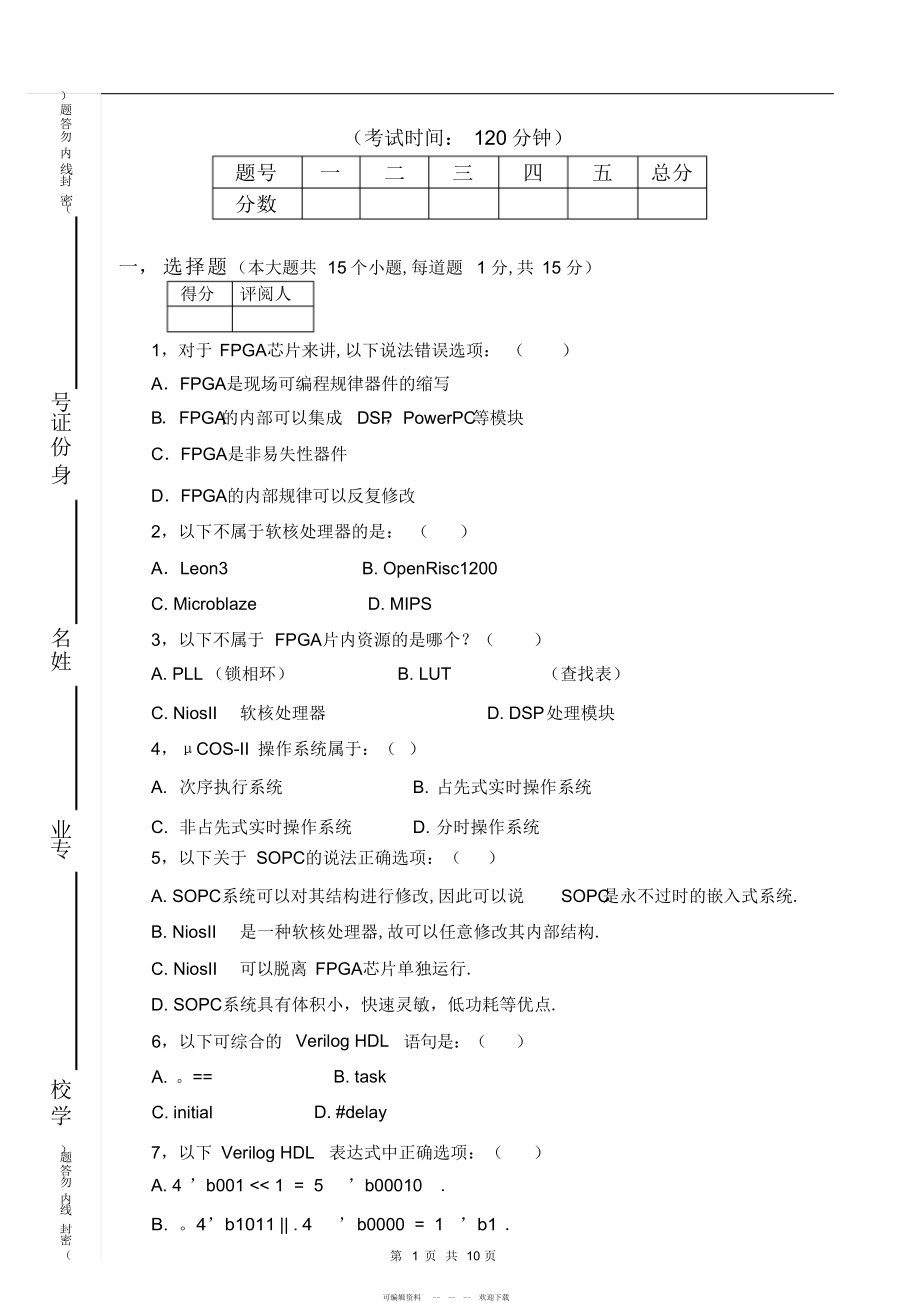

1、)题答勿(考试时间: 120 分钟)内封线题号一二三四五总分(密分数一, 选择题(本大题共 15 个小题,每道题 1 分,共 15 分) 得分评阅人1,对于 FPGA芯片来讲,以下说法错误选项: ()AFPGA是现场可编程规律器件的缩写号证BFPGA的内部可以集成 DSP,PowerPC等模块份CFPGA是非易失性器件身DFPGA的内部规律可以反复修改2,以下不属于软核处理器的是: ()ALeon3B. OpenRisc1200C. MicroblazeD. MIPS名3,以下不属于 FPGA片内资源的是哪个?()姓A. PLL (锁相环)B. LUT(查找表)C. NiosII软核处理器D.

2、 DSP 处理模块4,COS-II 操作系统属于:( )A. 次序执行系统B. 占先式实时操作系统业C. 非占先式实时操作系统D. 分时操作系统专5,以下关于 SOPC的说法正确选项:()A. SOPC系统可以对其结构进行修改,因此可以说SOPC是永不过时的嵌入式系统.B. NiosII是一种软核处理器,故可以任意修改其内部结构.C. NiosII可以脱离 FPGA芯片单独运行.6,以下可综合的Verilog HDL语句是:()A. 。=C. initialB. taskD. #delayD. SOPC系统具有体积小,快速灵敏,低功耗等优点.校学题)7,以下 Verilog HDL表达式中正确

3、选项:()答勿A. 4 b001 << 1 = 5b00010.内线封B. 。4b1011 | . 4 b0000 = 1b1 .密(第 1 页 共 10 页可编辑资料 - - - 欢迎下载C. 4 b1010 & 4 b1101 = 1b1 .D. 4 b1011 && 4 b0100 = 4 b1111 .8,以下选项中哪个不是嵌入式系统软硬件划分的原就.()A.系统优化原就B.资源利用率原就C.性能原就D.性价比原就9,NiosII的系统中SDRAM的 IP核时钟与系统全局时钟相差多少度?()A. -60度C. -70度B. -50D. -90度度10

4、,以下描述可以在 FPGA中稳固运行的是:()A. 状态机编码中接受二进制编码方式B. 在时钟上升沿到来时 A 的值由“ 1001”变为“ 0110”C. 大量接受异步电路设计D. 接受时钟的正负沿调整采样11,以下关于 Verilog HDL模块连接正确选项:()Module1 Module2.a code1 ,.clk clk ,.rst rst ,.b k1 ;A. a 是顶层模块, code1 是底层模块.B. b 是顶层模块, k1 是底层模块.C. Module1 是底层模块, Module2 是顶层模块.D. Module2 的端口可以用 reg 类型定义12,以下关于 uCli

5、nux的说法正确选项 :()A. uClinux是在 linux的基础上裁剪了内核和应用程序库.B. uClinux可以使用 linux的一部分命令C. uClinux由于没有 MM,U 故仅能运行在没有MMU的处理器上D. uClinux13,以下对是硬实时的嵌入式操作系统.I2C 总线说法正确选项 : ()可编辑资料 - - - 欢迎下载A. SCL 线为高电平常, SDA线又低电平向高电平跳变表示数据传输的开头.B. SCL 线为低电平常, SDA线又低电平向高电平跳变表示数据传输的终止.C. SDA 线是双向的,而 SCL线是单向的.D. 在标准传输模式下, I2C 总线的速度是 40

6、0Kb/s 14,以下关于储备器的说法错误选项 : ()A. Nor flash的的特点是写入数据慢读出数据快.多用于储备指令.B. 全部的 Flash 储备器都存在“位交换” ,故必需使用 EDC/ECC算法以确保稳固性C. Sram 是静态随机储备器,一般读写速度很快但容量较小.D. DDR是在 SDRAM的基础上提高一倍时钟. 15,以下哪项不是 PLL锁相环的功能 : ()A. PLL 可以优化时钟,故有效降低 FPGA芯片的功耗.B. PLL 核是集成在 FPGA内的硬 IP 核,故无论使用与否, PLL 都存在在 FPGA中.C. 使用 PLL可以有效削减时钟偏斜的现象D. PLL

7、 可以调整时钟的频率,占空比,相位等二,判定题 (本大题共 10 个小题,每题 1 分,共 10 分) 得分评阅人1,NiosII系统结构中有 32 个 32 位的通用寄存器, 8 个 32 位把握寄存器.()2,Avalon 接口是一个同步协议的接口. ()3,在较高频率下 SDRAM把握器核与 SDRAM芯片之间需要 PLL调整时钟相位.()4,NiosII的定时器把握器的特性之一是具有增1,减 1 两种计数模式.()5,在 QuartusII编译之前,对 FPGA未使用的引脚一般要设置成 As inputtri-stated.()6,Flash 的数据总线是三态的, NiosIICPU与

8、 Flash 相连接时需要 Avalon 三态总线桥.()7,在 SOPC Builder 中定义 CPU的复位地址在 Flash ,而在 NiosII IDE中用户程序被连接到 Flash之外的地址,那么elf2flash有用程序将在用户程序前插入一个Boot-copier.()可编辑资料 - - - 欢迎下载8,对于 SDRAM把握器的数据引脚,可以与 OUTPU属T属性的引脚相连.()性的引脚相连,也可以与 BIDIR可编辑资料 - - - 欢迎下载9,SOPC Builder 供应了一个组件编辑器,一个典型的组件主要有三部分组成:硬件文件,软件文件和组件描述文件三部分组成.()10,s

9、ystem.h 头文件对 SOPC硬件进行了软件的描述. ()三,填空题 (本大题共 10 个空,每空 1 分,共 10 分) 得分评阅人1,Altera公司的 FPGA常用的配置方式: JTAG 方式, , .2,CycloneII FPGA 上面集成的 Block RAM 为 M4K,一个 M4K的大小是 .可编辑资料 - - - 欢迎下载3,使用 QuartusII进行 FPGA设计的开发流程是:设计输入,真,. ,仿可编辑资料 - - - 欢迎下载4,NiosII IDE为软件开发供应了 4 个主要功能:工程治理器,编辑器和编译器,调试器,.5,SOPC组件 On-chip Memor

10、y 可以用作 RAM外,仍可以设置成,甚至可以设置成双口存取.6,CycloneII EP2C20器件包含 4 个 PLL,每个 PLL 均有个输出.其中第个输出的驱动才能最强.四,简答题 (本大题共 8 个小题,每道题 5 分,共 40 分) 得分评阅人1,简述 SOPC开发流程和对 SOPC的懂得?可编辑资料 - - - 欢迎下载2,简述 IP 核复用的好处.3,硬核和软核的区分.4,Moore 和 Mealy 状态机的异同?可编辑资料 - - - 欢迎下载5,如何懂得可编程规律设计的面积和速度平稳与互换原就?6 ,什么是同步设计,什么是异步设计?FPGA设计中为什么遵循同步设计原就?7,

11、Verilog HDL设计中堵塞赋值和非堵塞赋值有什么区分?举例说明.可编辑资料 - - - 欢迎下载8,简述 FPGA设计中毛刺产生的条件及排除毛刺的简洁方法.五,程序题 (本大题共 3 个小题,共 25 分)得分评阅人1,在 Verilog HDL或者 VHDL中如何定义 inout型 的接口?( 7 分)可编辑资料 - - - 欢迎下载2,系统的时钟输入是 50MHz,请用 VerilogHDL或者 VHDL设计一个分频器得到 10Hz的时钟输出.( 8 分)3, 说明扫描矩阵键盘的工作原理,用Verilog或 VHDL编写去除按键抖动的代码?(提示:认为只有一次按下是键盘抖动,三次按下

12、才是有按键输入)(10 分)可编辑资料 - - - 欢迎下载答案选择题:1 C2 D3 C4 B5 A6 B7 B8 A9 A10 B11,C12,A13,B14,D15,A判定题:1,F2,T3 ,T4,F5 ,T6 ,T7,T8 ,F 9 ,T10 T填空题:1,AS方式/EPCS方式 ,PS方式/CPLD方式2,4Kbit3,综合,布局布线,配置或下载4,下载器5,ROM6,3 , 3简答题:1,第一建立 SOPC工程添加系统需要的 IP 核,设置每个 IP 核的属性,然后分别进行系统的硬件设计和软件设计,然后把硬件设计生成的配置文件下载到FPGA,再启动 NiosII运行软件程序. S

13、OPC设计灵敏,可以依据需要设计针对不同应用的嵌入式系统.2,设计快速,便利,灵敏,性能优化,3,硬核是实际电路构成的不行以转变的功能模块.软核是用 HDL语言编写的可以修改全部或部分内部结构的功能模块.4,假如规律输出只取决于当前状态,这样的状态机叫Moore 状态机.假如规律输出不仅取决于当前状态,而且仍取决于输入,这样的状态机叫Mealy 状态机.5,面积指占用的规律单元的数量,速度指模块的处理速度.面积和速度是相互制约的,也就是说,假如占用很小的FPGA面积,速度就受到确定限制, 相反,想要较高的处理速度必定是占用很大的面积.所以在 FPGA中确定要考虑模块的实际需要,假如要达到很高的

14、处理速度可以多个模块并行处理,假如要节省规律资源,可以反复使用一个处理模块.6,假如设计中功能模块内的寄存器值都在同一个时钟的上升沿或下降沿下变化,这个设计就是同步设计,否就为异步设计.在 FPGA中接受同步设计的缘由是保证设计的稳固性,削减竞争和冒险的发生.7,always posedge clk BeginA <= B ;B的值赋给 AC <= D ;同时 D的值赋给 C End非堵塞always posedge clk BeginA = B ;B的值赋给 AC = D ;下一个上升沿时 D的值赋给 C End堵塞8,假如输入端的多位信号,其中的两位或者两位以上规律值在同一时间

15、向相反方向跳变,在输出端就可能显现毛刺.可编辑资料 - - - 欢迎下载1,在时钟方面多使用 PLL,2,规律多接受同步设计, 3,使用 D触发器.程序题:1,inout data ; Input data_in ; Reg data_reg ; Reg link_data ;assign data = link_data . data_reg : 1 bz ; / link_data为高时, data 是输出端.link_data为低时, data 是输入端.2,parameter period = 5000000 ; Reg31:0 cnt ;Regclkout ;Always posedge clk or negedge rst BeginIf rst = 0 Cnt <= 32 b0 ;ElseCnt <= cnt + 1 ;If cnt = period <<

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025-2030中国有机生物施肥行业市场现状供需分析及投资评估规划分析研究报告

- 2025-2030中国月嫂行业市场深度调研及发展趋势与投资前景研究报告

- 2025-2030中国智能锁行业应用现状与发展趋势前景研究报告

- 2025-2030中国智能窗户材料行业市场发展趋势与前景展望战略分析研究报告

- 2025-2030中国智能牙刷行业市场发展分析及发展前景与投资研究报告

- 2025-2030中国无刷电机行业运营现状与重点企业发展建议研究报告

- 2025-2030中国旋转阀行业市场发展趋势与前景展望战略研究报告

- 2025-2030中国旅行社软件行业市场现状供需分析及投资评估规划分析研究报告

- 2025-2030中国数字版权管理(DRM)行业市场现状供需分析及投资评估规划分析研究报告

- 2025-2030中国数字图书馆行业发展前景及发展策略与投资风险研究报告

- 有效咳嗽咳痰课件

- 2024《整治形式主义为基层减负若干规定》全文课件

- DZ∕T 0227-2010 地质岩心钻探规程(正式版)

- 新教材人教A版高中数学必修第二册全册教学课件

- 高考地理一轮复习 课件 中国地形-山脉

- 绘画心理分析课件

- (环境监测)第四章-大气和废气监测课件

- 乳腺癌患者生存质量测定量表(FACT-B)

- 国家职业技能《数控机床装调维修工》技术知识考试题库与答案共300题

- 《国际关系学入门》课件第九章 对外政策

- FANUC机器人培训教程(完成版)(PPT134页)

评论

0/150

提交评论