下载本文档

版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

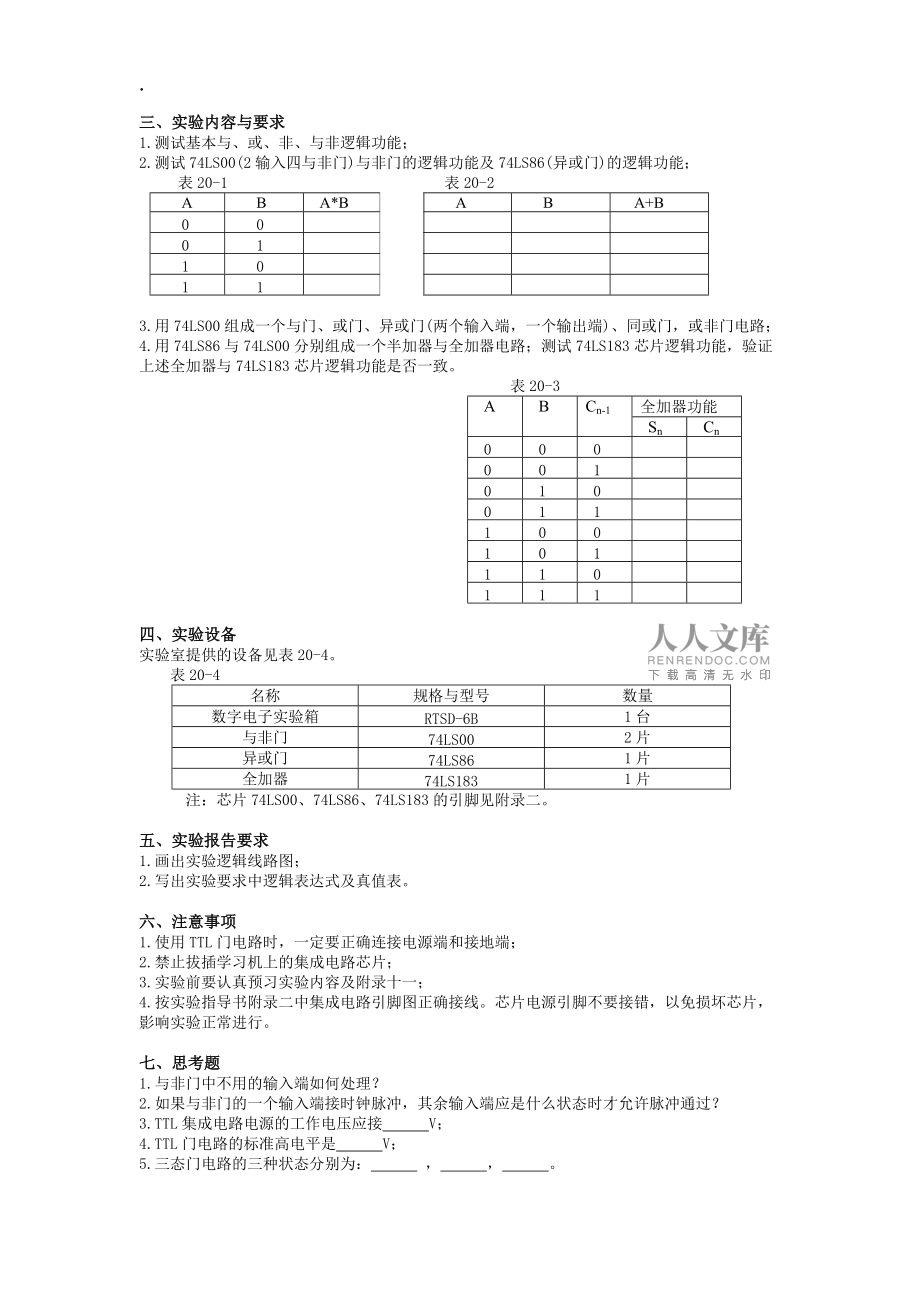

1、.基本门电路一、实验目的1.了解TTL门电路的原理、性能和使用方法;2.掌握基本门电路逻辑功能;3.熟悉基本运算单元、半加器和全加器的逻辑关系和功能。二、实验原理在数字电路中,门电路是实现某种逻辑关系的最基本的单元,任何复杂的组合电路和时序电路都可用逻辑门通过适当的组合连接而成。因此,掌握逻辑门的工作原理,熟练、灵活地使用逻辑门,是学习数字电路的基础。本实验在数字学习机上进行,其各种逻辑电路都是由集成TTL门电路构成,逻辑关系用正逻辑分析。图20-1 与门电路ABF&1.与门逻辑功能为当输入端A与B均为“1”时,输出才为“1”,其逻辑函数式为2.或门图20-2 或门电路ABF&逻辑功能为当输入

2、端A或B有一端为“1”时,输出为“1”,其逻辑函数式为3.异或门其逻辑功能为当输入信号A、B相同时,输出为“0”,当两个输入信号不同时,输出为“1”。其逻辑函数式为图20-4 有异或门的半加器&CnSnAnBn=1图20-3 异或门电路ABF&4.半加器半加器是求同一位上的两个加数和的运算单元。这个和称为半加和或本位和。逻辑表达式为式中,分别表示两个加数在第n位上的数码,为本位和,为该位向高一位的进位。图20-5 全加器逻辑图An&=1BnCn-1=1CnSn5.全加器全加器是在半加器的基础上,能够实现两个加数的某一位加法运算全功能的逻辑电路。它不仅能求本位和,而且可以同时将从低位来的进位也加

3、进去。全加器电路由两个半加器和一个或门构成,逻辑表达式为式中,表示全加和,表示低位全加器输出的进位数,表示本位全加进位数,表示半加和。三、实验内容与要求1.测试基本与、或、非、与非逻辑功能;2.测试74LS00(2输入四与非门)与非门的逻辑功能及74LS86(异或门)的逻辑功能; 表20-1 表20-2 A B A*B A B A+B 0 0 0 1 1 0 1 13.用74LS00组成一个与门、或门、异或门(两个输入端,一个输出端)、同或门,或非门电路;4.用74LS86与74LS00分别组成一个半加器与全加器电路;测试74LS183芯片逻辑功能,验证上述全加器与74LS183芯片逻辑功能是

4、否一致。 表20-3 A BCn-1全加器功能 Sn Cn 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1四、实验设备实验室提供的设备见表20-4。表20-4名称规格与型号数量数字电子实验箱RTSD-6B1台与非门74LS002片异或门74LS861片全加器74LS1831片 注:芯片74LS00、74LS86、74LS183的引脚见附录二。五、实验报告要求1.画出实验逻辑线路图;2.写出实验要求中逻辑表达式及真值表。六、注意事项1.使用TTL门电路时,一定要正确连接电源端和接地端;2.禁止拔插学习机上的集成电路芯片;3.实验前要认真预习实验内容及附录十一;4.按实验指导书附录二中集成电路引脚图正确接线。芯片电源引脚不要接错,以免损坏芯片,影响实验正常进行。七、思考题1.与非门中不用的输入端如何处理?2.如果与非门的一个输入端接时钟脉冲,其余输入端应是什么状态时才允许脉冲通过?3.TTL集成电路电源的工作电压应接 V;4.TTL门电路的标准高电平是 V;5.三态门电路的三种状态分别为: , , 。图20-6 数字学习机功能与结构图数码显示插座区显示灯16个ONOFFF

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 笔墨纸砚试题及答案

- 包装运输试题及答案

- 产品推广流程

- 2025年春节节前安全培训

- 冷轧酸洗工艺流程

- 二甲医院等级评审前培训

- ICU病人腹泻护理查房

- 小学音乐《爱我中华》课程

- 布艺销售培训

- 智齿拔除病例分析与微创拔牙技术应用

- 手术室医疗垃圾的分类

- 教育领域中的信息化技术讨论以小学数为例

- 绿色施工知识培训课件

- 《骨盆骨折的急救》课件

- 2025年拍卖师职业技能知识考试题库与答案(含各题型)

- 浙江省杭州市六校2023-2024学年高一下学期期末联考技术试卷-高中技术

- 《人工智能:AIGC基础与应用》题库 项选择题

- 《班组长培训》课件

- 临床约翰霍普金斯跌倒评估量表解读

- GB/T 44786-2024水力发电厂自动化计算机控制导则

- 妇幼健康信息管理制度

评论

0/150

提交评论