付费下载

下载本文档

版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

iiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiiinoutiiiiii0in102111010322211010433322120300out例:32位先行进位加法器的1、能概述先行进位加法器是对普通的全加器进行改良而设计成的并行加法器,主要是针对普通全加器串联时互相进位产生的延迟进行了改良。超前进位加法器是通过增加了一个不是十分复杂的逻辑电路来做到这点的。设二进制加法器第i位A,B输出为,位输入为C进位输出为,有:=A⊕⊕

i

()C*B+A*C+B*C*B(A+B)*令=A*B,=A+B则C当A和B都为1时G=1产生进位C1当A和B有一个为1时=,传递进位C

()因此G义为进位产生信号P定为进位传递信号的优先级比高也就是说当G1时当然此时也有=1条件产生进位,而不管是多少;当G而时进位输出为,之前的逻辑有关。下面推导4位前进位法器。设加数和被加数为A,位输入为C,进位输出为,对于第i位的进位产生G=A·B进传递=A+B,i=0,1,2,3。是这各级进位输出,递归的展开,有:CCC=G+P·CC=G+P·C=G+P·GC

0C=G+P·C+P·G·G+·P·CC=G+P·C+P·G·G+·P·P·CC

()由此可以看出,各级的进位彼此独立产生,只与输入数AiBi和Cin有,将各级间的进位级联传播给去掉了,因此减小了进位产生的延迟。每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。实现上述逻辑表达的电路称为超进位部LookaheadUnitCLA部件通过这种进位方式实现的法器称为超前进位加法器为个进位是并行产生的,所以是一种并行进位加法器。从公式)可知,更多位数的部只会增加逻辑门的输入端个数,而不会增加门的级数,因此,如果采用超前进位方式实现更多位的加法器,从理论上讲,门延迟不变。但是由于CLA部件中连线数量和输入端个数的增多,使得电路中需要具有大动信号和大扇入门,这会大大增加门的延迟,起不到提高电路性能的作用。因此更多位数的加

44m0m0344m0m03m03222104m08m14m1m1m0m112m28m2m2m1m2m1m0m116m3m3m3m2m304BCLA法器可通过位部和超前进位加法器来实现,如图示。将式()中进位C的辑方程改写为:C=G

(1-4)C4表位法器的进位输出Pm0、分表示位法器的位传递输出和进位产生输出,分别为:=·P·PG+·G·P·G+将式()应用于个4位行进位加法器,则有:C=G+P·CC=G·C=G·G+

0C=G+P·C=G+·G+P·P·G+·PC=G=G·G·G·P·G()比较式)和式以看出这两组进位逻辑表达式是类似的。不过式1-3)表示的是组内进位,式()表示的是组间的进。实现逻辑方程组()的电路称为成组先行进位部件。图1a为所设计的32位超前进位加法器的结构框,该加法器采用三级超前进位加法器设计,组内和组间均采用超前进位。由8个4超前进位加法器与个部构成。图1b为用超前进位和进位选择实现的位先行进位加法器结构图。2、构框图ABAB

ABAB

ABAB

A

B

A

B

4CLA

C

4CLA

C

4CLA

C

4CLA

4CLA

C

4CLA

C

4CLA

C

4CLA

C

gp

S

gp

SSgp4BCLA

gp

S

Sgp

SSgpgp

Sgp

CLAC

gp

C

g4BCLA

gp()位超前进位加法器结构图A

B

A

B

A

B

16位

1

16位

0

16位

010

C

16

(b超前进位进位选择实现结构图32位行进位加法器结图

x32x3x32x332332144位前进位3、口说明表1:32位前进位加法器接信号说明表序号

接口信号名称A[31:0]

方向IIO

说明输入数据输入数据加法器结果

备注4、位超前进加法器的设(4bits)功能述产生进位信(如图2a位法器的进位传递信号Px以位加法器的进位产生信号Gx·PG=+P·G·P·G·P·P·G结构图

4

3

2

1

0

3

3

2

2

1

1

0

0()位超前进位链AB

A

B

A

B

A

B

FA

C

3

CFAFAFA

C

0gp33C

S

Sgpgp2211gpm0m0

S

gp00

S

(b超前进位加法器图位CLA部和位前进位加法器

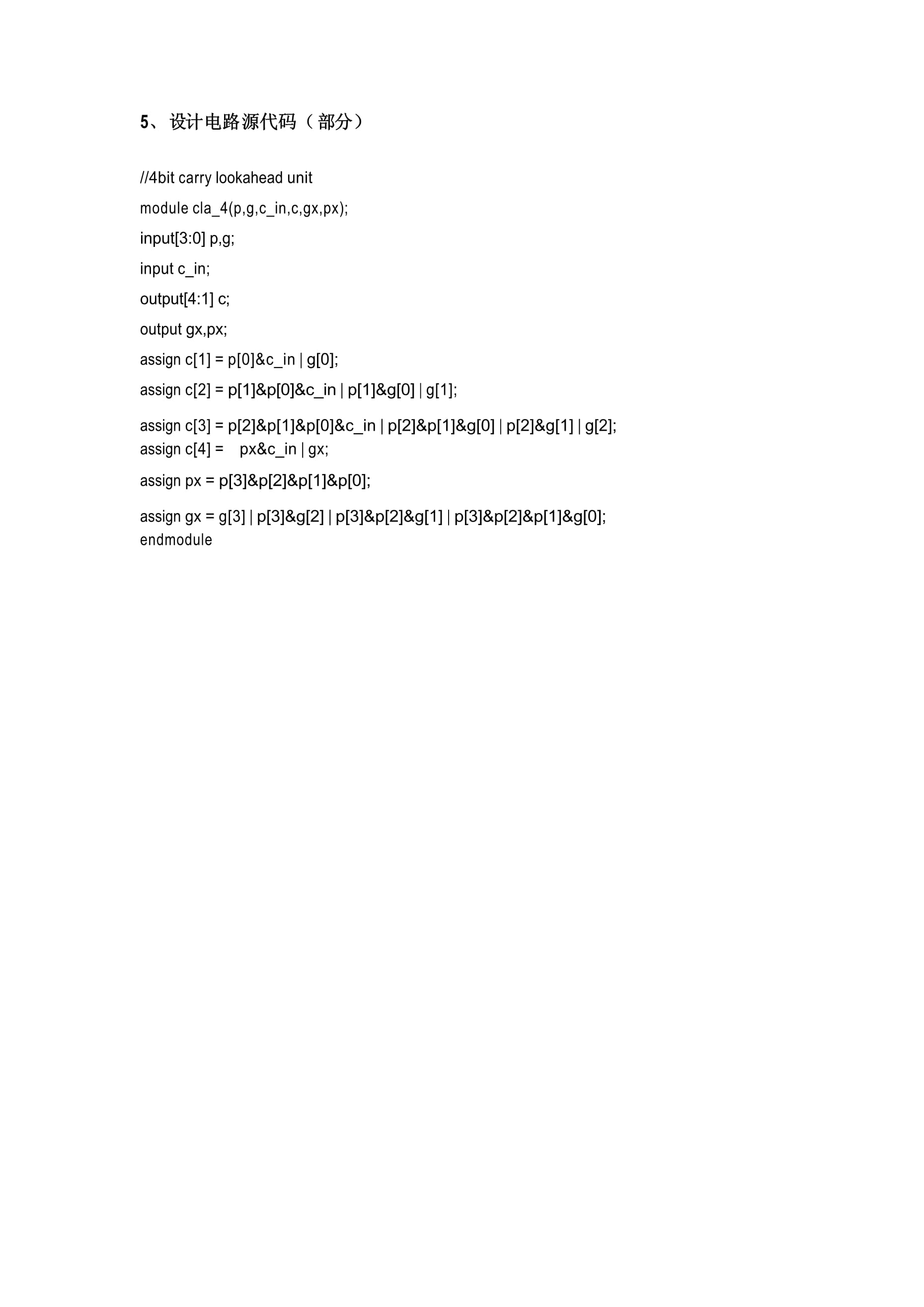

5、计电路代码(分)//4bitcarrylookaheadunitmodulecla_4(p,g,c_in,c,gx,px);inputc_in;outputassignc[1]=p[0]&c_ing[0];assign

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 全员安全意识提升专项行动方案

- 注册会计师税法中企业所得税法税收优惠减免税的适用条件

- 气体公司充装操作准则

- 机械制造厂设备维修制度

- 某钢铁厂热轧工艺操作制度

- 2026中国科学院化学研究所怀柔研究中心招聘备考题库含答案详解(能力提升)

- 2026清华大学出版社校园招聘备考题库带答案详解(培优b卷)

- 2026浙江台州市中医院招聘心电图诊断医生(编外)1人备考题库(含答案详解)

- 2026安徽皖信招聘铁塔阜阳市分公司技术人员2人备考题库及参考答案详解ab卷

- 2026江西鹰潭月湖区民政局招聘工作人员1人备考题库及参考答案详解(新)

- 2026年护士资格考试统考历年真题及答案

- 2025年12月大学英语六级考试真题第2套(含答案+听力原文+听力音频)

- 流行病学筛检试题及答案

- 2026年变形零件的特殊加工工艺

- 2026年成都辅警考试题库及完整答案

- 2026年上海电机学院单招综合素质考试题库附参考答案详解(达标题)

- 2026年商业地产运营管理协议

- 2026年moldflow铜牌考试试题

- 病人护工合同范本

- 汽油柴油知识课件

- 2026年浙江建设职业技术学院单招职业倾向性考试题库附答案

评论

0/150

提交评论