下载本文档

版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

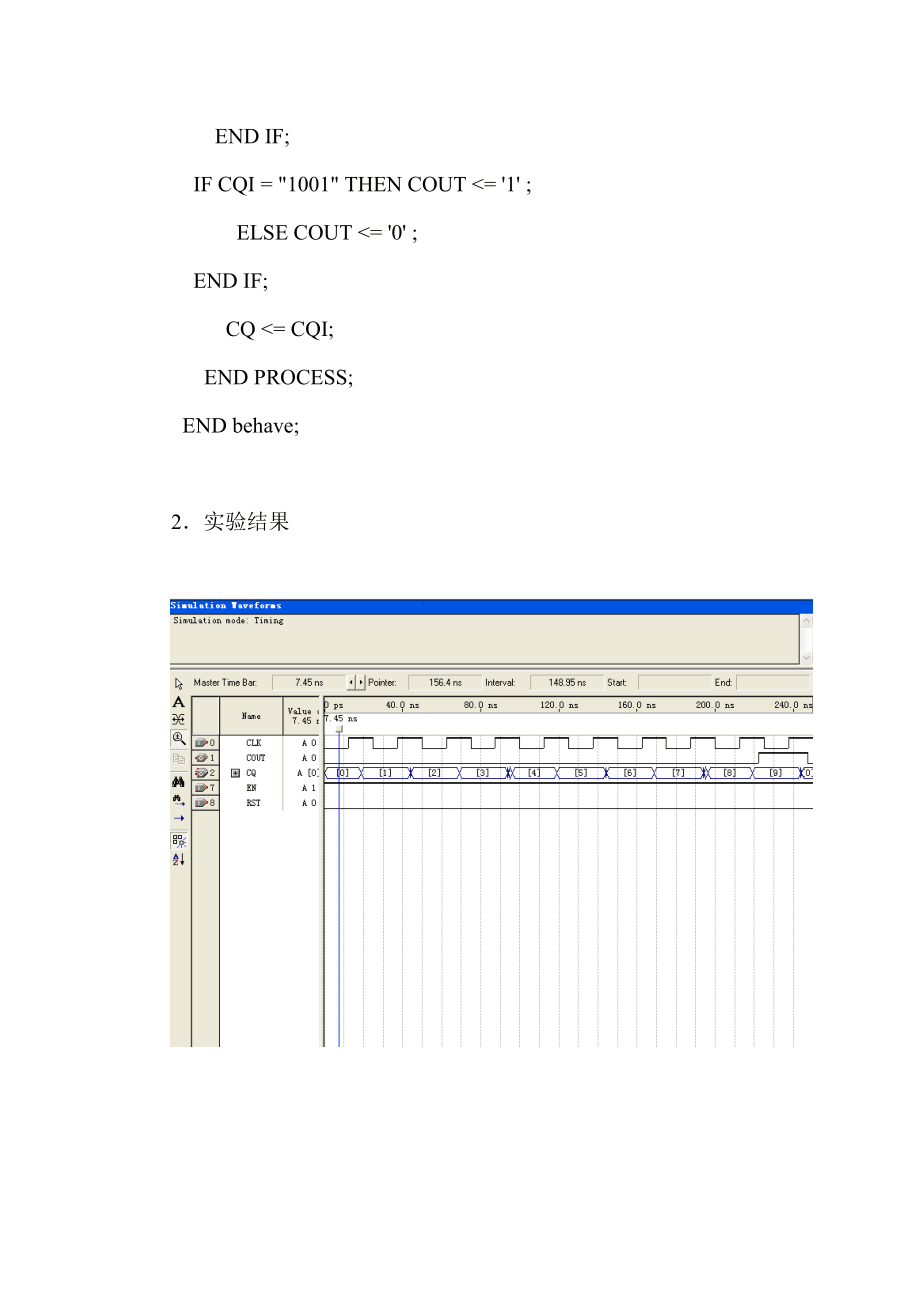

1、EDA实验5 计数器设计一、实验目的 计数器是实验中最为常用的时序电路模块之一,本实验的主要目的是掌握使用HDL描述计数器类型模块的基本方法。二、实验仪器1. EDA开发软件 一套2. 微机 一台3. 实验开发系统 一台三、实验说明计数器是数字电路系统中最基本的功能模块之一,设计时可以采用原理图或HD语言完成。下载验证时的计数时钟可选用连续或单脉冲,并用数码管显示计数值。四、实验要求1 设计一个带有计数允许输入端、复位输入端和进位输出端的十进制计数器。2 编制仿真测试文件,并进行功能仿真。3 下载并验证计数器功能。4 为上述设计建立元件符号。五、实验过程1.源程序LIBRARY IEEE;US

2、E IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY counter IS PORT (CLK,RST,EN : IN STD_LOGIC; CQ : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); COUT : OUT STD_LOGIC ); END counter; ARCHITECTURE behave OF counter IS BEGIN PROCESS(CLK, RST, EN) VARIABLE CQI : STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN IF

3、 RST ='1' THEN CQI := (OTHERS => '0'); ELSIF CLK'EVENT AND CLK = '1' THEN IF EN = '1' THEN IF CQI < "1001" THEN CQI := CQI + 1; ELSE CQI :=(OTHERS => '0' ); END IF; END IF; END IF; IF CQI = "1001" THEN COUT <= '1' ; ELSE COUT <= '0' ; EN

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025版北京房地产售后增值服务合同

- 二零二五年DJ培训机构聘用教师合同

- 二零二五年度新能源汽车采购及充电设施建设合同

- 二零二五年度环保型供电工程总承包合同范本

- 2025版太阳能热水系统安装与售后服务合同范本

- 2025版汽车配件展摊位租赁合同范本

- 二零二五年度家居用品采购定制协议

- 二零二五年度生物制药研发成果转让合同

- 二零二五年度汽车租赁与维修连锁承包合同范本

- 2025版动画电影编剧聘请合同范文

- 英汉互译单词练习打印纸

- 政府预算和部门预算支出经济分类科目对照表

- GA/T 2012-2023窃照专用器材鉴定技术规范

- 气相色谱质谱联用仪技术指标

- 湖州市市级机关事业单位编外招聘考试试卷真题及答案2022

- 第三章 科学研究与科学方法论

- 山东黄金归来庄矿业有限公司归来庄金矿矿山地质环境保护与土地复垦方案

- 项目融资计划书

- 针刺伤的预防及处理

- YY/T 0595-2020医疗器械质量管理体系YY/T 0287-2017 应用指南

- LS/T 1222-2020粮食干燥机系统工艺设计技术规范

评论

0/150

提交评论