版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、29第二章 逻辑门 第2章逻辑门内容提要:本章系统地介绍数字电路的基本逻辑单元门电路,及其对应的逻辑运算与图形描述符号,并针对实际应用介绍了三态逻辑门和集电极开路输出门,最后简要介绍TTL集成门和CMOS集成门的逻辑功能、外特性和性能参数。2.1 基本逻辑门导读:在这一节中,你将学习:n 与、或、非三种基本逻辑运算n 与、或、非三种基本逻辑门的逻辑功能n 逻辑门真值表的列法n 画各种逻辑门电路的输出波形在逻辑代数中,最基本的逻辑运算有与、或、非三种。每种逻辑运算代表一种函数关系,这种函数关系可用逻辑符号写成逻辑表达式来描述,也可用文字来描述,还可用表格或图形的方式来描述。最基本的逻辑关系有三种

2、:与逻辑关系、或逻辑关系、非逻辑关系。实现基本逻辑运算和常用复合逻辑运算的单元电路称为逻辑门电路。例如:实现“与”运算的电路称为与逻辑门,简称与门;实现“与非”运算的电路称为与非门。逻辑门电路是设计数字系统的最小单元。2.1.1 与门“与”运算是一种二元运算,它定义了两个变量A和B的一种函数关系。用语句来描述它,这就是:当且仅当变量A和B都为1时,函数F为1;或者可用另一种方式来描述它,这就是:只要变量A或B中有一个为0,则函数F为0。“与”运算又称为逻辑乘运算,也叫逻辑积运算。 “与”运算的逻辑表达式为:式中,乘号“”表示与运算,在不至于引起混淆的前提下,乘号“”经常被省略。该式可读作:F等

3、于A乘B,也可读作:F等于A与B。图2-1 与运算电路逻辑与运算可用开关电路中两个开关相串联的例子来说明,如图2-1所示。开关A、B所有可能的动作方式如表2-1a所示,此表称为功能表。如果用1表示开关闭合,0表示开关断开,灯亮时F=1,灯灭时F=0。则上述功能表可表示为表2-1b。这种表格叫做真值表。它将输入变量所有可能的取值组合与其对应的输出变量的值逐个列举出来。它是描述逻辑功能的一种重要方法。表2-1a 功能表开关A开关B灯F断开断开灭断开闭合灭闭合断开灭闭合闭合亮表2-1b “与”运算真值表AB000010100111由“与”运算关系的真值表可知“与”逻辑的运算规律为:简单地记为:有0出

4、0,全1出1。由此可推出其一般形式为: 实现“与”逻辑运算功能的的电路称为“与门”。 每个与门有两个或两个以上的输入端和一个输出端,图2-2是图2-2 与门的逻辑符号两输入端与门的逻辑符号。在实际应用中,制造工艺限制了与门电路的输入变量数目,所以实际与门电路的输入个数是有限的。其它门电路中同样如此。例2-1 画出表示3输入与门和8输入与门的逻辑符号。解:使用标准符号,并加入正确数量的输入数据线,结果如图2-3所示。图2-3 3输入和8输入与门例2-2 如图2-4所示,向2输入与门输入图示的波形,求其输出波形F。图2-4 图2-5解:当输入波形A和B同时为高电平时(对应于图2-5中的阴影部分),

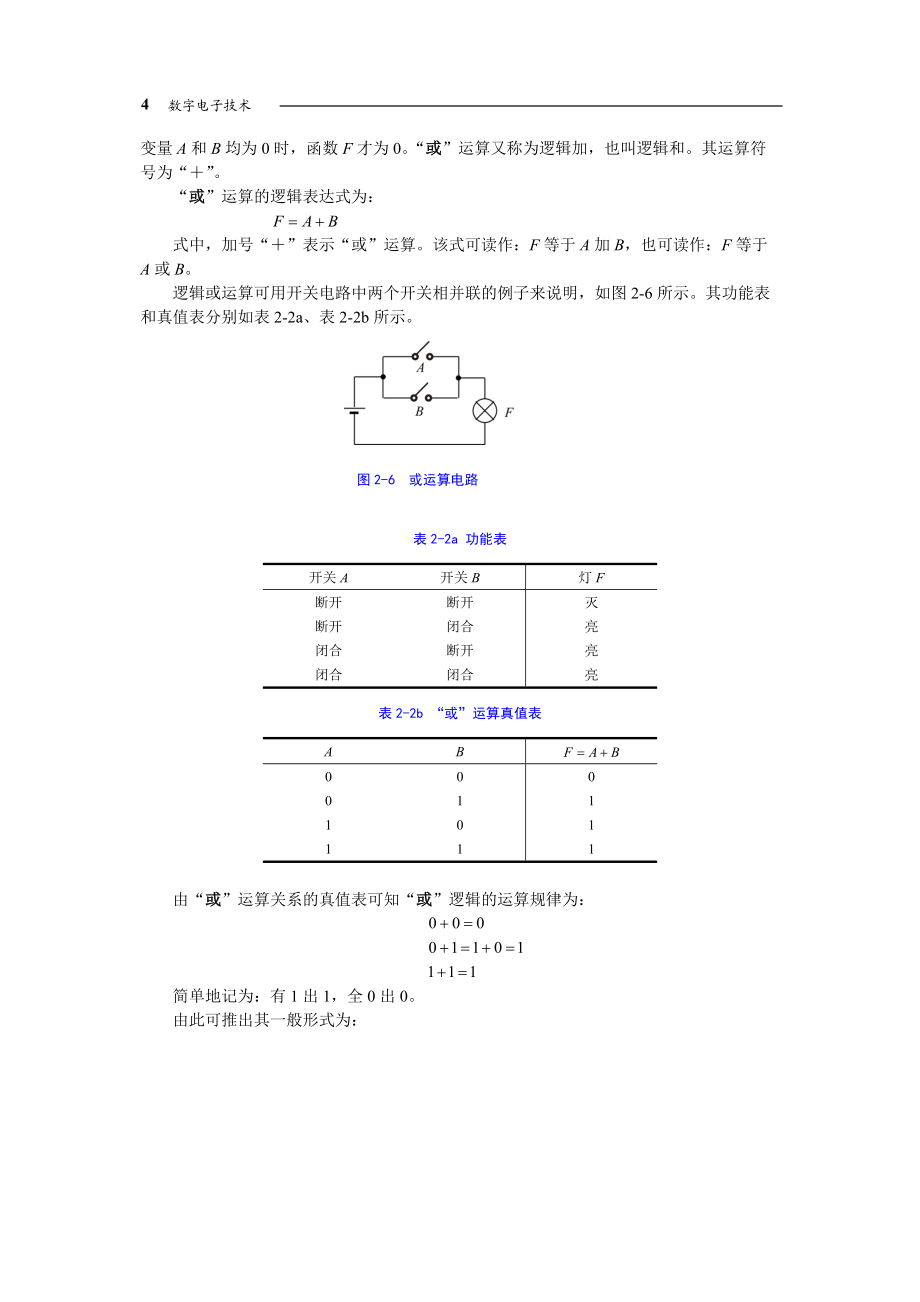

5、输出波形F为高电平。2.1.2 或门“或”运算是另一种二元运算,它定义了变量A、B与函数F的另一种关系。用语句来描述它,这就是:只要变量A和B中任何一个为1,则函数F为1;或者说:当且仅当变量A和B均为0时,函数F才为0。“或”运算又称为逻辑加,也叫逻辑和。其运算符号为“”。 “或”运算的逻辑表达式为:式中,加号“”表示“或”运算。该式可读作:F等于A加B,也可读作:F等于A或B。逻辑或运算可用开关电路中两个开关相并联的例子来说明,如图2-6所示。其功能表和真值表分别如表2-2a、表2-2b所示。图2-6 或运算电路表2-2a 功能表开关A开关B灯F断开断开灭断开闭合亮闭合断开亮闭合闭合亮表2

6、-2b “或”运算真值表AB000011101111由“或”运算关系的真值表可知“或”逻辑的运算规律为:简单地记为:有1出1,全0出0。由此可推出其一般形式为:图2-7 或门的逻辑符号实现“或”逻辑运算功能的电路称为“或门”。每个或门有两个或两个以上的输入端和一个输出端,图2-7是两输入端或门的逻辑符号。例2-3 画出表示3输入与门和8输入或门的逻辑符号。图2-8 3输入和8输入与门解:使用标准符号,并加入正确数量的输入数据线,结果如图2-8所示。例2-4 如图2-9所示,向2输入或门输入图示的波形,求其输出波形F。解:当输入波形A和B之一、或全部为高电平时(对应于图2-10中的阴影部分),输

7、出波形F为高电平。图2-9 图2-102.1.3 非门逻辑“非”运算是一元运算,它定义了一个变量(记为A)的函数关系。用语句来描述之,这就是:当A=1时,则函数F=0;反之,当A=0时,则函数F=1。非运算亦称为“反”运算,也叫逻辑否定。“非”运算的逻辑表达式为: 式中,字母上方的横线“”表示“非”运算。该式可读作:F等于A非,或F等于A反。图2-11 非运算电路逻辑“非”运算可用图2-11(a)中的开关电路来说明。在图2-11(b)中,若令A表示开关处于常开位置,则表示开关处于常闭位置。其功能表和真值表很简单,分别如表2-3a、2-3b所示。表2-3a 功能表A断开1闭合0表2-3b “非”

8、运算真值表A0110由“非”运算关系的真值表可知“非”逻辑的运算规律为:简单地记为:有0出1,有1出0。由此可推出其一般形式为:实现“非”逻辑运算功能的电路称为“非门”。非门也叫反相器。每个非门有一个输入端和一个输出端。图2-12是非门的逻辑符号。图2-12 非门的逻辑符号例2-5如图2-13所示,向非门输入图示的波形,求其输出波形F。图2-13 图2-14解:如图2-14所示,当输入波形为高电平时,输出就为低电平;反之亦然。自测练习: 1. 满足( )时,与门输出为高电平。(a)只要有一个或多个输入为高电平(b)所有输入都是高电平(c)所有输入都是低电平2. 4输入与门有( )种可能的输入状

9、态组合?3. 对于5输入与门,其真值表有( )行,( )列?4. 与门执行( )逻辑运算。5. 满足( )时,或门输出为低电平。(a)一个输入为高电平(b)所有输入都是低电平(c)所有输入都是高电平(d)(a)和(c)都对6. 4输入或门有( )种可能的输入状态组合?7. 对于5输入或门,其真值表有( )行,( )列?8. 或门执行( )逻辑运算。9. 非门执行( )逻辑运算。10. 非门有( )个输入。2.2 复合逻辑门导读:在这一节中,你将学习:n 与非、或非、异或、同或的复合逻辑运算n 与非门、或非门的逻辑功能n 异或门、同或门的逻辑功能n 各种复合逻辑门的真值表描述及输出波形基本逻辑运

10、算的复合叫做复合逻辑运算。而实现复合逻辑运算的电路叫复合逻辑门。最常用的复合逻辑门有与非门、或非门、与或非门和异或门等。2.2.1 与非门“与”运算后再进行“非”运算的复合运算称为“与非”运算,实现“与非”运算的逻辑电路称为与非门。一个与非门有两个或两个以上的输入端和一个输出端,两输入端与非门的逻辑符号如图2-15所示。其输出与输入之间的逻辑关系表达式为:图2-15 与非门的逻辑符号与非门的真值表如表2-4所示。表2-4 “与非”门真值表AB001011101110使用与非门可实现任何逻辑功能的逻辑电路。因此,与非门是一种通用逻辑门。例2-6如图2-16所示,向2输入与非门输入图示的波形,求其

11、输出波形F。图2-16 图2-17解:当输入波形A和B同为高电平时(如图2-17中的阴影部分),输出波形F为低电平。2.2.2 或非门“或”运算后再进行“非”运算的复合运算称为“或非”运算,实现“或非”运算的逻辑电路称为或非门。或非门也是一种通用逻辑门。一个或非门有两个或两个以上的输入图2-18 或非门的逻辑符号端和一个输出端,两输入端或非门的逻辑符号如图2-18所示。输出与输入之间的逻辑关系表达式为:或非门的真值表如表2-5所示。表2-5 “或非”门真值表AB001010100110和与非门一样,或非门也可用来实现任何逻辑功能的逻辑电路。因此,或非门也是一种通用逻辑门。例2-7 如图2-19

12、所示,向2输入与非门输入图示的波形,求其输出波形F。解:只要输入波形A、B有一个、或均为高电平时(对应于图2-20中的阴影部分),输出波形Y就为低电平。图2-19 图2-202.2.3 异或门在集成逻辑门中,“异或”逻辑主要为二输入变量门,对三输入或更多输入变量的逻辑,都可以由二输入门导出。所以,常见的“异或”逻辑是二输入变量的情况。对于二输入变量的“异或”逻辑,当两个输入端取值不同时,输出为“1”;当两个输入端取值相同时,输出端为“0”。实现“异或”逻辑运算的逻辑电路称为异或门。如图2-图2-21 二输入异或门的逻辑符号21所示为二输入异或门的逻辑符号。相应的逻辑表达式为:其真值表如表2-6

13、所示。表2-6 二输入“异或”门真值表AB000011101110例2-8 如图2-22所示,向异或门输入图示的波形,求其输出波形F。图2-22 图2-23解:当输入波形A和B有且只有一个为高电平时的时间内(对应于图2-23中的阴影部分),输出波形F就为高电平。至于多变量的“异或”逻辑运算,常以两变量的“异或”逻辑运算的定义为依据进行推证。N个变量的“异或”逻辑运算输出值和输入变量取值的对应关系是:输入变量的取值组合中,有奇数个1时,“异或”逻辑运算的输出值为1;反之,输出值为0。2.2.4 同或门“异或”运算之后再进行“非”运算,则称为“同或”运算。实现“同或”运算的电路称为同或门。同或门的

14、逻辑符号如图2-24所示。二变量同或运算的逻辑表达式为: 图2-24 同或门的逻辑符号其真值表如表2-7所示。表2-7 二变量“同或”门真值表AB001010100111例2-9如图2-25所示,向同或门输入图示的波形,求其输出波形F。图2-25 图2-26解:当输入波形A和B有且只有一个为高电平时的时间内(对应于图2-26中的阴影部分),输出波形F就为低电平。像多变量的“异或”逻辑运算一样,多变量的“同或”逻辑运算也常以两变量的“同或”逻辑运算的定义为依据进行推证。N个变量的“同或”逻辑运算的输出值和输入变量取值的对应关系是:输入变量的取值组合中,有偶数个1时,“同或”逻辑运算的输出值为1;

15、反之,输出值为0。自测练习:1. 2输入与非门对应的逻辑表达式是( )。2. 满足( )时,与非门输出为低电平。(a)只要有一个输入为高电平。(b)所有输入都是高电平(c)所有输入都是低电平3. 当用两输入与门的一个输入端传输信号时,作为控制端的另一端应加( )电平。 4. 对于5输入与非门,有( )种可能的输入变量取值组合。5. 对于4输入与非门,其真值表有( )行,( )列。6. 对于8输入与非门,在所有可能的输入变量取值组合中有( )组输入状态能够输出低电平?7. 或门和非门应该( )连接才能组成或非门? 8. 满足( )时,或非门输出为高电平。(a)一个输入为高电平。(b)所有输入都是

16、低电平(c)多于一个的输入是高电平(d)(a)和(c)都对9. 当二输入异或门的输入端电平( )( 相同,不相同)时,其输出为1。10. 将二输入异或门用作反相器时,应将另一输入端接( )电平。11. 当二输入同或门的输入端电平( )( 相同,不相同)时,其输出为1。12. 要使二输入变量异或门输出端F的状态为0,A端应该:(a)接B (b)接0 (c)接113. ( )是异或门的表达式。(a)(b)(c)14. 异或门可看作1的( )(奇、偶)数检测器。2.3 其它逻辑门导读:在这一节中,你将学习:n 三态逻辑门的逻辑功能n 含有三态逻辑门电路的分析n 集电极开路输出逻辑门的逻辑功能n 集电

17、极开路输出逻辑门的应用2.3.1 三态逻辑门三态输出门(简称TS门)除了有高电平和低电平(即逻辑1和逻辑0)两种逻辑状态外,还有第三种状态高阻状态(记为Z),或称为禁止状态。在第三种状态下,三态门的输出端相当于悬空,此时的输出端就好象一根空头的导线,其电压值可浮动在高低电平之间的任意数值上。图2-27 三态门的逻辑符号(a) 控制端高电平有效(b) 控制端低电平有效三态输出门的构成是在普通逻辑门电路的基础上增加一些专门的控制电路,以及一个新的控制输入端三态使能端,即EN(Enable)端,通过1/0逻辑电平来控制。图2-27给出了三态与非门的逻辑符号。图2-27(a)为高电平有效的三态门,其真

18、值表如表2-8所示。当EN = 1时,三态门工作,实现正常“与非”功能;当EN = 0时,三态门禁止,呈现高阻态。图2-27(b)则正好相反,为低电平有效的三态门,当EN = 0时,三态门工作;当EN = 1时,三态门禁止;图2-27(b)在控制端上加了一个小圆圈,表示低电平有效。表2-8 三态门的真值表使能端数 据输出端ENABF0xx高阻1001101111011110 当三态门输出端处于高阻状态时,该门电路表面上仍与整个电路系统相连接,但实际上对整个系统的逻辑功能和电气特性均不发生任何影响,如同没把它接入系统一样。三态门是数字系统在采用总线结构时对接口电路提出的要求。因此,三态门在总线接

19、口中得到了广泛的应用。如图2-28所示,三态门用来实现多路数据在总线上的分时传送。为实现这一功能,只要控制各个门的EN输入端,轮流定时地使各个EN端为1,并且在任何时刻只有一个EN端为1,这样就可以把各个门的输出信号轮流传送到总线上。必须保证在任何时刻只有一个三态门被选通,即只有一个门向总线传送数据;否则,会造成总线上的数据混乱,并且损坏处于导通状态的输出管。传送到总线上的数据可以同时被多个负载门接收,也可以在控制信号作用下,让指定的负载门接收。利用三态门还可以实现数据的双向传输,如图2-29所示,其中门G1和门G2为三态反相器,门G1低电平有效,门G2高电平有效。当三态使能端EN = 0时,

20、门G1选通,门G2禁止,数据从A传到B;当三态使能端EN = 1时,门G2选通,门G1禁止,数据从B传到A。图2-29 用三态门实现数据双向传输图2-28 三态门用于总线传输2.3.2 集电极开路逻辑门集电极开路门,简称OC门。其特点是门电路内部输出三极管的集电极开路。在使用时,必须外接“上拉电阻RP”使得该输出端与直流电源相连。多个OC门输出端相连时,可以共用一个上拉电阻RP。图2-30显示了一个OC与非门的开关级电路结构,其逻辑符号如图2-31所示。只有当A和B都为1时,输出才为0;否则,F点与逻辑门脱离了连接,上拉电阻将它拉至逻辑1。下面介绍OC门的几个主要应用。1 实现线与功能图2-3

21、1 OC与非门的逻辑符号图2-30 OC与非门的开关级描述两个OC门输出端并联的电路如图2-32所示,其并联后实现的逻辑功能如表2-9所示。显然,F与F1 、F2之间为“与”逻辑关系,即由于这种“与”逻辑是两个OC门的输出线直接相连实现的,故称作“线与”。图2-32实现的逻辑表达式为:图2-32 OC与非门构成的线与逻辑电路虽然利用集电极开路门可以使门的输出端并联起来,获得附加的逻辑功能。但是,由于负载电阻R受许多因素限制,其值不能取得很小,限制了它的开关速率。一般来说,OC门和TS门都可以允许输出端直接并接在一起,用来实现多路信号在总线上的分时传送。但是三态门在使用时不需要再另外加接电阻,所

22、以更经济一些。在现代逻辑设计中,三态门几乎已经完全取代了OC门。表2-9 OC与非门输出端并联后的逻辑功能表F1F2F000010100111例2-10写出图2-33中OC门线与的输出表达式Y。解:输出表达式是:Y = ABCDEFGH可以看出,四个2输入OC与门的线与结果连接构成了一个8输入的与门。2 实现电平转换当线与的OC门F1 、F2的输出级都截止时,F输出高电平,这个高电平就等于电源的电压Vcc,这个Vcc的电平值可以不同于门电路本身的电源,所以只要根据要求选择Vcc就可以得到所需要的高电平值。在数字系统中,在系统的接口部分(与外部设备相连接的地方)常需要转换电平,常用逻辑门来完成电

23、平的转换。如图2-34所示把上拉电阻接到Vcc=10V的电源上,这样在OC门输入普通的TTL电平,而输出高电平就可以变为10V。因而输出可适应于需要较高电平的器件,如荧光数码管、MOS译码器等。3 用做驱动器可用它来驱动发光二极管、指示灯、继电器和脉冲变压器等。图2-35是用来驱动发光二极管的电路。当OC门输出低电平时,发光二极管导通发光;当OC门输出高电平时,发光二极管截止。图2-33 例题2-10图2-34 实现电平转换图2-35 驱动发光二极管表2-10 例211ACF1F2000高阻01高阻1101高阻11高阻0例题2-11 写出表2-10所示门电路的输出逻辑表达式,列出真值表,并说明

24、逻辑功能。解: 当C=0时,F1=A;当C=1时,F 1输出高阻状态。因此它是一个使能端低电平有效的三态缓冲器门,C为使能端。如图例2-36(a)所示。当C=1时,F 2=;当C=0时,F 2输出高阻状态。因此它是一个使能端高电平有效的三态非门,C为使能端。如图例2-36(b)所示。图2-36 例题2-11自测练习:1. 集电极开路的与非门也叫( ),使用集电极开路的与非门,其输出端和电源之间应外接( )电阻。2. 三态门的输出端有( )、( )和( )三种状态。3. 三态门输出为高阻状态时,( )是正确的说法。 (a) 用电压表测量指针不动 (b) 相当于悬空 (c)电压不高不低 (d) 测

25、量电阻指针不动 4. 以下电路中可以实现“线与”功能的有( ): (a) 与非门 (b) 三态输出门 (c)集电极开路门 5对于图2-27(b)所示的三态与非门,当控制端EN = 0时,三态门输出为( );当EN = 1时,三态门输出为( )。2.4 集成电路逻辑门导读:在这一节中,你将学习:n TTL集成逻辑门的概念n 比较各种TTL系列的特性n CMOS集成逻辑门的概念n 集成电路逻辑门的性能参数n 计算具体逻辑器件的扇出系数n TTL与CMOS两种集成电路在混合应用时的接口2.4.1 概述把若干个有源器件和无源器件及其连线,按照一定的功能要求,制作在一块半导体基片上,这样的产品叫集成电路

26、。若它完成的功能是逻辑功能或数字功能,则称为数字集成电路。最简单的数字集成电路是集成逻辑门。集成电路比分立元件电路有许多显著的优点,如体积小、耗电省、重量轻、可靠性高等等,所以集成电路一出现就受到人们的极大重视并迅速得到广泛应用。数字集成电路的规模一般是根据门的数目来划分的。小规模集成电路(SSI)约为10个门,中规模集成电路(MSI)约为100个门,大规模集成电路(LSI)约为1万个门,而超大规模集成电路(VLSI)则为1百万个门。在本节中,将介绍小规模数字集成电路的基本知识,而不涉及集成电路的内部电路。集成电路逻辑门,按照其组成的有源器件的不同可分为两大类:一类是双极性晶体管逻辑门; 另一

27、类是单极性的绝缘栅场效应管逻辑门。双极性晶体管逻辑门主要有TTL门(晶体管晶体管逻辑门)、ECL门(射极耦合逻辑门)和I2L门(集成注入逻辑门)等。单极性MOS门主要有PMOS门(P沟道增强型MOS管构成的逻辑门)、NMOS门(N沟道增强型MOS管构成的逻辑门)和CMOS门(利用PMOS管和NMOS管构成的互补电路构成的门电路,故又叫互补MOS门)。其中,使用最广泛的是TTL集成电路和CMOS集成电路。每种集成电路又分为不同的系列,每个系列的数字集成电路都有不同的品种类型,用不同的代码表示,也就是器件型号的后几位数码。例如:00:4路2输入与非门02:4路2输入或非门08:4路2输入与门10:

28、3路3输入与非门20:双路4输入与非门27:3路3输入或非门32:4路2输入或门86:4路2输入异或门具有相同品种类型代码的集成电路,不管属于哪个系列,它们的逻辑功能相同,外形尺寸相同,引脚也兼容。例如,7400, 74LS00, 74ALS00, 74HC00, 74AHC00都是14个引脚兼容的4路2输入与非门封装。图2-37给出了7400芯片的引脚图、DIP(Dual In-line Package双列直插式封装)外形图。其它型号芯片的引脚图见本书附录。最常用的是采用塑料或陶瓷封装技术的双列直插式封装(DIP),这种封装是绝缘密封的,有利于插到电路板上。图2-37 7400引脚配置及DI

29、P封装外形图常见的另一种IC封装形式是SMT(Surface-Mount Technology)封装,简称表面贴装。SMT封装的芯片直接焊接在电路板的表面,而无须在印刷电路上穿孔,所以其密度更高,即给定区域内可以放置更多的IC芯片。使用集成门电路芯片时,要特别注意其引脚配置及排列情况,分清每个门的输入端、输出端和电源端、接地端所对应的引脚,这些信息及芯片中门电路的性能参数,都收录在有关产品的数据手册中,因此使用时要养成查数据手册的习惯。2.4.2 TTL集成电路逻辑门TTL门电路由双极型三极管构成,其特点是速度快、抗静电能力强,但其功耗较大,不适宜做成大规模集成电路。目前广泛应用于中、小规模集

30、成电路中。TTL门电路有74(民用)和54(军用)两大系列,每个系列中又有若干子系列。例如,74系列包含如下基本子系列:74:标准TTL(Standard TTL)。74L:低功耗TTL(Low-power TTL)。74S:肖特基TTL(Schottky TTL)。74AS:先进肖特基TTL(Advanced Schottky TTL)。74LS:低功耗肖特基TTL(Low-power Schottky TTL)。74ALS:先进低功耗肖特基TTL(Advanced Low-power Schottky TTL)。使用者在选择TTL子系列时主要考虑它们的速度和功耗,其速度及功耗的比较见表2-

31、11。其中74LS系列产品具有最佳的综合性能,是TTL集成电路的主流,是应用最广的系列。54系列和74系列具有相同的子系列,两个系列的参数基本相同,主要在电源电压范围和工作温度范围上有所不同。54系列适应的范围更大些,如表2-12所示。不同子系列在速度、功耗等参数上有所不同。对于全部的TTL集成门电路都采用+5V电源供电,逻辑电平为标准TTL电平。表2-11 TTL系列速度及功耗的比较速度TTL系列功耗TTL系列最快最慢74AS 74S 74ALS 74LS7474L最小最大74L 74ALS74LS74AS 7474S表2-12 54系列与74系列的比较系列电源电压(V)环境温度()544.

32、5 5.555 +125744.75 5.250 702.4.3 CMOS集成电路逻辑门CMOS集成门电路由场效应管构成,它的特点是集成度高、功耗低,但速度较慢、抗静电能力差。虽然TTL门电路由于速度快和更多类型选择而流行多年,但CMOS门电路具有功耗低、集成度高的优点,而且其速度也已经获得了很大的提高,目前已经能够与TTL门电路相媲美。因此,CMOS门电路获得了广泛的应用,特别是在大规模集成电路和微处理器中已经占据了支配地位。CMOS集成电路的供电电源可以在318V之间,不过,为了与TTL门电路的逻辑电平兼容,多数的CMOS集成电路使用+5V电源。另外还有3.3V CMOS门电路。3.3V

33、CMOS门电路是最近发展起来的,它的功耗比5V CMOS门电路低得多。同TTL门电路一样,CMOS门电路也有74和54两大系列。74系列5V CMOS门电路的基本子系列如下:l 74HC和74HCT:高速CMOS(High-speed CMOS),T表示和TTL直接兼容。l 74AC和74ACT:先进CMOS(Advanced CMOS),它们提供了比TTL系列更高的速度和更低的功耗。l 74AHC和AHCT:先进高速CMOS(Advanced High-speed CMOS)。74系列3.3V CMOS门电路的基本子系列如下:l 74LVC:低压CMOS(Lower-voltage CMOS

34、)。l 74ALVC:先进低压CMOS(Advanced Lower-voltage CMOS)。和5V电源电压工作下的CMOS集成电路相比,其功耗可减少34左右。2.4.4 集成电路门的性能参数在本节,我们仅从使用的角度介绍集成逻辑门电路的几个外部特性参数,目的是希望对集成逻辑门电路的性能指标有一个概括性的认识。至于每种集成逻辑门的实际参数,可在具体使用时查阅有关的产品手册和说明。数字集成电路的性能参数主要包括:直流电源电压、输入 / 输出逻辑电平、扇出系数、传输延时、功耗等。1 直流电源电压TTL集成电路的标准直流电源电压为5V,最低4.5V,最高5.5V。CMOS集成电路的直流电源电压可

35、以在318V之间,74系列CMOS集成电路有5V和3.3V两种。CMOS电路的一个优点是电源电压的允许范围比TTL电路大,如5V CMOS电路当其电源电压在26V范围内时能正常工作,3.3V CMOS电路当其电源电压在23.6V范围内时能正常工作。2 输入 / 输出逻辑电平对一个TTL集成门电路来说,它的输出“高电平”,并不是理想的+5V电压,其输出“低电平”,也并不是理想的0V电压。这主要是由于制造工艺上的公差,使得即使是同一型号的器件输出电平也不可能完全一样;另外,由于所带负载及环境温度等外部条件的不同,输出电平也会有较大的差异。但是,这种差异应该在一定的允许范围之内,否则就会无法正确标识

36、出逻辑值“1”和逻辑值“0”,从而造成错误的逻辑操作。数字集成电路分别有如下四种不同的输入 / 输出逻辑电平。对于TTL电路:l 低电平输入电压范围VIL :0 0.8V。l 高电平输入电压范围VIH :25V。l 低电平输出电压范围VOL :不大于0.4V。l 高电平输出电压范围VOH :不小于2.4V,门电路输出高、低电平的具体电压值与所接的负载有关。对于5V CMOS电路:n 低电平输入电压范围VIL :0 1.5V。n 高电平输入电压范围VIH :3.55V。n 低电平输出电压范围VOL :不大于0.33V。n 高电平输出电压范围VOH :不小于4.4V。图2-38给出了TTL电路的输

37、入 / 输出逻辑电平示意图。当输入电平在VIL(max)和VIH(min)之间时,逻辑电路可能把它当作0,也可能把它当作1。而当逻辑电路因所接负载过多等原因不能正常工作时,高电平输出可能低于VOH(min),低电平输出可能高于VOL(max)。图2-38 标准TTL门的输入 / 输出逻辑电平3 传输延迟时间tpd在集成门电路中,由于晶体管开关时间的影响,使得输出与输入之间存在传输延迟。传输延时越短,工作速度越快,工作频率越高。因此,传输延迟时间是衡量门电路工作速度的重要指标。例如,在特定条件下,传输时间为10ns的逻辑电路要比20ns的电路快。由于实际的信号波形有上升沿和下降沿之分,因此td是

38、两种变化情况所反映的结果。一是输出从高电平转换到低电平时,输入脉冲指定参考点与输出脉冲相应参考点之间的时间,记为tPHL;另一种是输出从低电平转换到高电平时的情况,记作tPLH ,如图2-39所示为一个反相器的传输延迟时间tPHL和tPLH的测量。参考点可以选在输入和输出脉冲相应边沿的50%处。在实际中常用平均传输延迟时间来表示门电路的传输延迟这一指标:图2-39 tPHL和tPLH的定义TTL集成门电路的传输延迟时间tpd的值为几纳秒十几个纳秒;一般CMOS集成门电路的传输延迟时间tpd较大,几十个纳秒左右,但高速CMOS系列的tpd较小只有几个纳秒左右;ECL集成门电路的传输延迟时间tpd

39、最小,有的ECL系列不到1纳秒。4 扇入和扇出系数对于集成门电路,驱动门与负载门之间的电压和电流关系如图2-40所示,这实际上是电流在一个逻辑电路的输出与另一个电路的输入之间如何流动的描述。在高电平输出状态下,驱动门提供电流IOH给负载门,作为负载门的输入电流IIH ,这时驱动门处于“拉电流”工作状态。而在低电平输出状态下,驱动门处于“灌电流”状态。图2-40 两种逻辑状态中的电流和电压扇入和扇出系数是反映门电路的输入端数目和输出驱动能力的指标。扇入系数:指一个门电路所能允许的输入端个数。扇出系数:一个门电路所能驱动的同类门电路输入端的最大数目。扇出系数越大,门电路的带负载能力就越强。一般来说

40、,CMOS电路的扇出系数比TTL电路高。扇出系数的计算公式为:从上式可以看出,扇出系数的大小由驱动门的输出端电流IOL、IOH的最大值和负载门的输入端电流IIL、IIH的最大值决定。这些电流参数已在制造商的IC参数表中以某种形式给出。例2-12 已知74ALS00的电流参数为IOL(max) = 8mA,IIL(max)= 0.1mA,IOH(max)= 0.4mA,IIH(max)= 20mA。求一个74ALS00与非门输出能驱动多少个74ALS00与非门的输入。解:首先考虑低电平状态。在低电平状态下得到能被驱动的输入个数:注意:在查IC手册时,我们会发现输入电流IIL实际上是0.1mA。这

41、里的负号用来表示电流是由输入端流出的。今后,在计算中可以忽略负号。在高电平状态能驱动的输入个数是:如果低电平扇出系数和高电平扇出系数不相同,扇出系数选择两个中的较小者。因此,74ALS00与非门能驱动20个其它的74ALS00与非门输入端。对于标准系列TTL门,扇出系数一般为10,对于其它系列TTL门如74LS系列,扇出系数一般为20。对于CMOS门电路,虽然输入端阻抗非常高,所需输入电流非常小,但由于其输入端有电容,当电平发生变化时,电容有充放电电流通过,因此, CMOS门电路输出端可接的输入端数量也是受到限制的,其扇出系数一般为50左右。需要注意的是,当输入端个数超过扇出系数时,就有可能改

42、变原来的输出电平,使得输出低电平超过VOL(max),或者输出高电平低于VOH(min),从而导致输出电平产生混乱。这时可采用另一种方法即接入缓冲门增大输出端的驱动能力,以避免上述情况的出现。5 功耗功耗是指门电路通电工作时所消耗的电功率,它等于电源电压Vcc和电源电流Icc的乘积,即功耗。但由于在门电路中电源电压是固定的,而电源电流不是常数,也就是说,在门电路输出高电平和输出低电平时通过电源的电流是不一样的,因而这两种情况下的功耗大小也不一样。一般求它们的平均值:一般情况下,CMOS集成电路的功耗较低,而且与工作频率有关(频率越高功耗越大),其数量级为微瓦,因而CMOS集成电路广泛应用于电池

43、供电的便携式产品中;TTL集成电路的功耗较高,其数量级为毫瓦,且基本与工作频率无关。2.4.5 TTL与CMOS集成电路的接口*我们知道,TTL门电路和CMOS门电路是两种不同类型的电路,它们的参数并不完全相同。因此,在一个数字系统中,如果同时使用TTL门电路和CMOS门电路,为了保证系统能够正常工作,必须考虑两者之间的连接问题。以满足表2-13所列条件:如果不满足表2-13所列条件,必须增加接口电路。常用的方法有增加上拉电阻、采用专门接口电路、驱动门并接等。如图2-41所示,这是TTL门驱动CMOS门的情况,为了两者的电平匹配,在TTL驱动门的输出端接了上拉电阻R。表2-13 TTL门与CM

44、OS门的连接条件驱动门负载门VOH(min)VIH(min)VOL(max)VIL(max)IOHIIHIOLIIL凡是和TTL门兼容的CMOS门(如74HCT××和74ACT××系列CMOS门)可以和TTL的输出端直接连接,不必外加元器件。至于其它CMOS门电路与TTL门电路的连接,可以采用电平转换器,如CC4049(六反相器)或CC4050(六缓冲器)等, 或采用CMOS漏极开路门(OD门),如CC40107等,其具体方法可以参考相关的技术资料。图2-41 TTL驱动门与CMOS负载门的连接自测练习: 1. 最流行的数字IC是( )和( )集成电路。

45、2. 字母TTL代表( ),3. 字母CMOS代表( )。4. ( )TTL子系列传输延时最短?( )TTL子系列功耗最小?5. CMOS门电路比TTL门电路的集成度( )、带负载能力( )、功耗( )。6. 对于TTL集成电路,如用万用表测得某输出端电压为2V,则输出电平为:(a)高电平(b)低电平(c)既不是高电平也不是低电平7. 对于TTL集成电路,3V输入为( )输入。(a)禁止(b)高电平(c)低电平8. 对于TTL集成电路,0.5V输入为( )输入。(a)禁止(b)高电平(c)低电平9. 输入信号经多级门传输到输出端所经过的门越多,总的延迟时间就( )。10. 扇出系数N越大,说明

46、逻辑门的负载能力( )(强,弱 )。11. 功耗极低是( )数字IC系列的显著特点。(a)CMOS(b)TTL12. ( )集成电路的特点是具有很好的抗干扰能力。(a)CMOS(b)TTL13. 所有TTL子系列的( )特性都相同。(a)速度(b)电压14. TTL集成电路中,( )子系列速度最快。15. 下列( )不是TTL集成电路。(a)74LS00(b)74AS00(c)74HC00(d)74ALS00本章小结1. 逻辑门是数字系统的“构造块”,是一种“判决”电路。根据输入电平的组合情况,逻辑门产生可预测的输出电平。2. 逻辑运算中的三种基本运算是与、或、非运算,与其对应的表示方式是逻辑

47、符号、逻辑表达式和真值表。基本逻辑运算是构成复合逻辑运算的基础。3. 只有当所有输入都是高电平时,与门的输出才是高电平。只要有一个或多个输入为高电平时,或门的输出就是高电平。非门(反相器)产生的输出电平正好与输入电平相反。4. 常用的复合逻辑运算有与非运算、或非运算、异或及同或运算,其中的与非、或非运算是通用运算。利用这些简单的逻辑关系可以组成更复杂的逻辑运算。5. 与非门等价于在与门后接一个反相器(即非门)。或非门等价于在或门后接一个反相器(即非门)。6. 只有当所有输入都是高电平时,与非门的输出才是低电平。只有当所有输入都是低电平时,或非门的输出才是高电平。7. 与非门可用来实现任一种基本

48、和复合逻辑运算;或非门同样可做到这一点。8. 异或门的表达式为,仅当输入A和B处于相反的逻辑电平时,输出F才变为高电平。9. 同或(异或非)门的表达式为,仅当输入A和B处于相同逻辑电平时,输出F才变为高电平。10. 把集电极开路输出线连接到一起能实现“线与”功能。把三态输出连接在一起可以允许多个器件共用一条数据总线,在这种情况下,某一时刻只允许一个器件驱动总线。11. 各种类型的逻辑门都是以集成电路(IC)形式提供的。主要的数字集成电路系列是TTL和CMOS系列。12. TTL系列集成电路采用双极型晶体管制造,这种系列提供有许多SSI逻辑门和MSI器件。13. CMOS集成电路利用互补MOSF

49、ET制造。由于它具有低功耗和较高的速度及集成度高等特点,CMOS技术已经占领了市场。14. 当许多器件连接在一起时,知道给定的输出能驱动多少个输入而不降低其性能至关重要。能驱动同类输入端的个数称为扇出系数。15. 对数字IC的理解重点在于它们的输出与输入之间的逻辑关系和外部电气特性。其性能参数主要包括:直流电源电压、输入 / 输出逻辑电平、传输延迟、扇出系数、功耗等。其特性包括:集成块类型、引脚逻辑图和符号。16. TTL系列和CMOS系列存在不同的特点和电压差别,除了兼容系列外,两者不能直接相连,当两者同处于一个系统中时就需要考虑接口问题。参考文献1 R.L.托克海姆美编著,陈文楷,徐萍萍译

50、. 数字原理. 北京:科学出版社,2002。2 Thomas L.Floyd美编著. Digital Fundamentals (Seventh Edition) (英文影印版). 北京:科学出版社,2003。3 John M. Yarbrough美编著,李书浩,仇广煜等译. 数字逻辑应用与设计. 北京:机械工业出版社,2000年。4 康华光编. 电子技术基础(数字部分). 北京:高等教育出版社,2000年。专业词汇汉英对照晶体管-晶体管逻辑(TTL):Transistor-Transistor LogicCMOS:Complementary Metal-Oxide Semiconductor

51、 求反:Complement双列直插式封装(DIP):Dual in-line Package 扇出系数:Fan out 集成电路(IC):Integrated Circuit反相:Inversion反相器:Inverter逻辑电平:Logic level金属氧化物半导体场效应管(MOSFET):Metal Oxide Semiconductor Field Effect Transistor与门:AND gate与非门:NAND gate或非门:NOR gate非门:NOT gate集电极开路门(OC):Open Collector Gate或门:OR gate功耗:Power Dissipation传输延时:Propagation delay表面贴焊

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2026江苏南京大学YJ20260640马克思主义学院特任助理研究员招聘1人备考题库有答案详解

- 2026河南郑州市公园广场事务中心公益性岗位招聘135人备考题库及答案详解1套

- 2026江西吉安新干县人民医院招聘见习岗专业技术人员20人备考题库附答案详解

- 2026北京纳米能源与系统研究所曹霞课题组招聘2人备考题库及答案详解(名师系列)

- 2026山东济南市中城市发展集团有限公司社会招聘备考题库参考答案详解

- 2026广西柳州柳城县中医医院招聘19人备考题库附答案详解(夺分金卷)

- 2026年安徽电子信息职业技术学院公开招聘博士人才5名备考题库及一套完整答案详解

- 2026河南郑州市招生考试中心公益性岗位招聘10人备考题库及答案详解(网校专用)

- 2026山东滨州市财金投资发展集团有限公司春季校园招聘备考题库附答案详解(基础题)

- 2026河北兴冀人才资源开发有限公司招聘护理助理30人备考题库附答案详解(培优a卷)

- 麻醉科药品管理工作制度

- 2026浙江温州市瓯海区交通运输局招聘2人建设笔试备考题库及答案解析

- 2026年华为光技术笔测试卷及参考答案详解1套

- 14.2法治与德治相得益彰 课 件 2025-2026学年统编版 道德与法治 八年级下册

- 2026年自考00247国际法真题

- 2026年紧凑型聚变能实验装置总装调试操作手册

- 感恩母爱温暖相伴-2026年母亲节主题班会课件

- (2025年)抗菌药物合理使用培训试题附答案

- 武汉街道全要素规划设计导则

- 2025年温医大三一笔试及答案

- 北森测评题库及答案2026

评论

0/150

提交评论