版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、简易频谱分析仪2005年电子大赛二等奖文章来源:凌阳科技教育推广中心作者:国防科技大学 李楠 刘亮 李俊 发布时间:2006-8-30 11:46:44摘要:本设计以凌阳16位单片机SPCE061的核心控制器件,配合Xilinx Virtex-II FPGA 及Xilinx公司提供的硬件DSP高级设计工具System Generator,制作完成本数字式外差频谱分析仪。前端利用高性能A/D对被测信号进行采集,利用FPGA高速、并行的处理特点,在FPGA内部完成数字混频,数字滤波等 DSP算法SPCE061单片机是整个设计的核心控制器件,根据从键盘接受的数据控制整个系统的工作流程,包括控制FPG

2、AT作以及控制双路D/A在模拟示波器屏幕上描绘频谱图。人机接口使用128X64液晶和4X4键盘。本系统运行稳定,功能齐全,人机界面友好关键字:SPCE061A简易频谱分析仪一、方案论证频谱分析仪是在频域上观察电信号特征,并在显示仪器上显示当前信号频谱图的仪器。从实现方式上可分为模拟式与数字式两类方案,下面对两种方案进行比较:方案一:模拟式频谱分析仪模拟方式的频谱仪以模拟滤波器为基础,通常有并行滤波法、顺序滤波法,可调滤波法、扫描外差法等实现方法,现在广泛应用的模拟频谱分析仪设计方案多为扫描外差法,此方案原理框图如图1.1 :图1.1模拟外差式频谱仪原理框图图中的扫频振荡器是仪器内部的振荡源,当

3、扫频振荡器的频率I:在一定范围内扫动时,输入信号中的各个频率分量.在混频器中产生差频信号Y放大器,使亮点在屏幕上的垂直偏移正比),依次落入窄带滤波器的通带内(这个通带是固定的),获得中频增益,经检波后加到于该频率分量的幅值。由于扫描电压在调制振荡器的同时,又驱动X放大器,从而可以在屏幕上显示出被测信号的线状频谱图。这是目前常用模拟外差式频谱仪的基本原理。模拟外差式频谱仪具有高带宽和高频率分辨率等优点,但是模拟器件调试复杂,短期实现有难度,尤其是在对频谱信息的存储和分析上,逊色于新兴的数字化频谱仪方案。方案二:数字式频谱分析仪数字式频谱仪通常使用高速 A/D采集当前信号,然后送入处理器处理,最后

4、将得到的各频率分量幅度值数据送入显示器显示,其组成框图如图1.2 :图1.2数字式频谱仪组成框图按照对信号处理方式的不同,数字式频谱仪可分为以下三种:(1)基于FFT技术的数字频谱仪:这种频谱仪利用快速傅里叶变换可以将被测信号分解成分立的频率分量,达到与传统频谱分析仪同样的结果。这种新型的频谱分析仪采用数字方法直接由模拟/数字转换器(ADC)对输入信号取样,再经FFT处理后获得频谱分布图。FFT技术的数字式频谱分析仪在速度上明显超过传统的模拟式频谱分析仪,能够进A/D转换器和高速数字器件的配合。行实时分析。但由于FFT所取的是有限长度,运算的点数也是有限的,因此,实现高扫频宽度和高频率分辨率需

5、要高速(2) 基于数字滤波法的数字式频谱仪这种频谱仪原理上等同于模拟频谱仪中的并行滤波法或可调滤波法,通过设置多个窄带带通数字滤波器,或是中心频率可变的带通数字滤波器,提取信号经过数字滤波器的幅度值,实现测量信号频谱的目的,该方法受到数字器件资源的限制,无法设置足够多的数字滤波器,从而无法实现高频率分辨率和高扫频宽度。(3) 基于外差原理的数字式频谱仪数字式外差”原理是把模拟外差式频谱分析仪中的各模块利用数字可编程器件实现,其原理框图如图1.3 :图1.3基于外差原理的数字式频谱仪原理框图信号经高速A/D采集送入处理器,通过硬件乘法器与本地由DDS产生的本振扫频信号混频,变频后信号不断移入低通

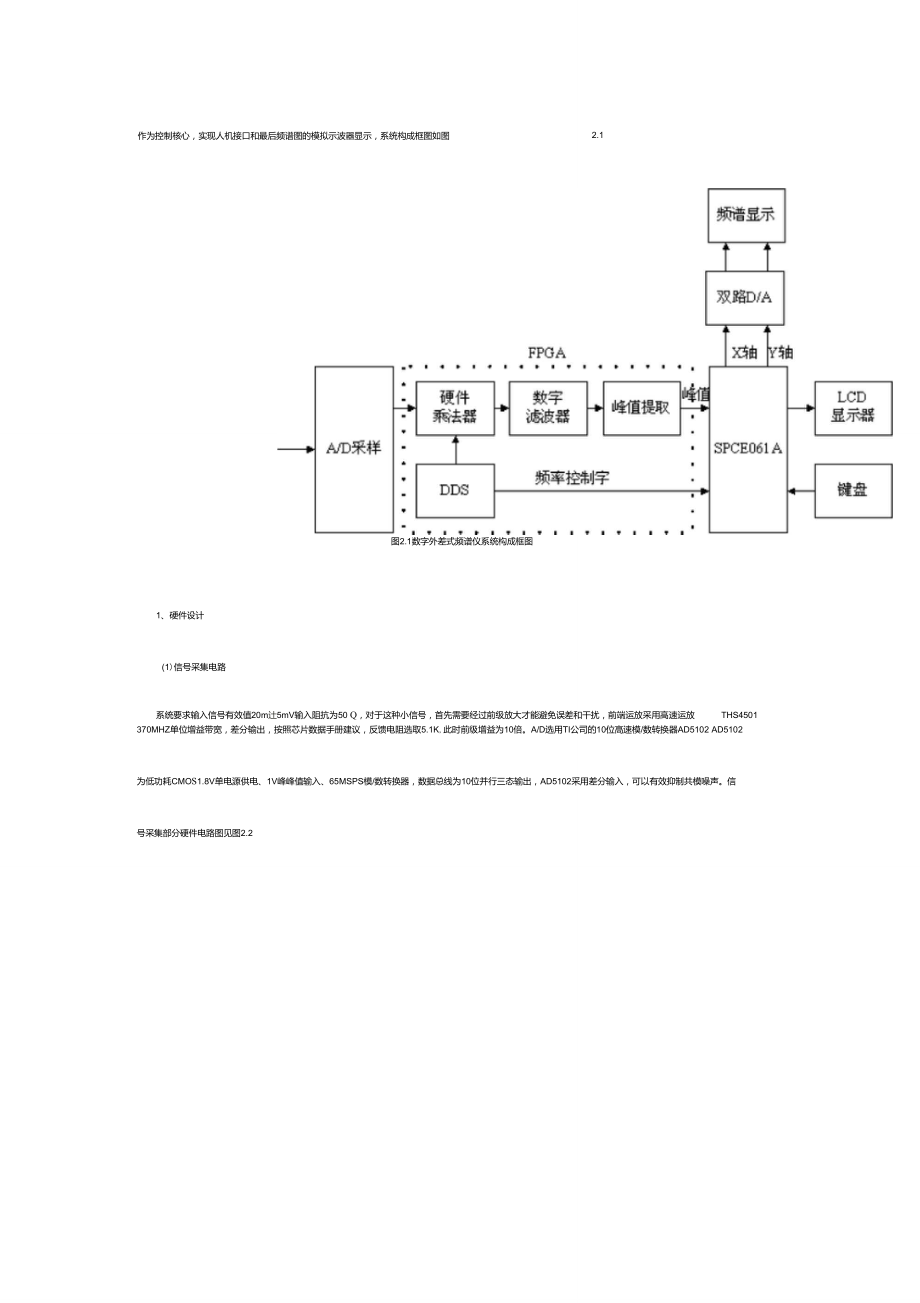

6、数字滤波器,然后提取通过低通滤波器的信号幅度,根据当前频率和提取到的幅度值,即可以绘制当前信号频谱图该方案利用数字器件实现传统方式上的外差式扫频仪,不但提高了速度,同时还可以对频谱信息实现存储和分析。理论上,只要数字滤波器的阶数足够高,频率分辨率可以做到很小,相比 FFT数字频谱仪方案和数字滤波法,系统中只要使用一个固定截止频率的低通滤波器,消耗资源少,同时可以省去大容量的存储器,这就在保证系统精度的前提下提高了系统集成度,节省了宝贵的片内资源。鉴于系统要求基于超外差原理设计频谱分析仪,权衡超外差频谱仪的模拟方案与数字方案,本系统采取方案二中的数字外差法方案。详细软硬件设计SPCE061A系统

7、采用XILINX VIRTEX-II 100万门的FPGA将本振扫频,混频,放大,低通滤波,提取峰值等工作全部数字化实现。控制方面,由凌阳单片机2.1 :作为控制核心,实现人机接口和最后频谱图的模拟示波器显示,系统构成框图如图图2.1数字外差式频谱仪系统构成框图1、硬件设计(1)信号采集电路系统要求输入信号有效值20m辻5mV输入阻抗为50 Q,对于这种小信号,首先需要经过前级放大才能避免误差和干扰,前端运放采用高速运放THS4501 370MHZ单位增益带宽,差分输出,按照芯片数据手册建议,反馈电阻选取5.1K,此时前级增益为10倍。A/D选用TI公司的10位高速模/数转换器AD5102 A

8、D5102为低功耗CMOS1.8V单电源供电、1V峰峰值输入、65MSPS模/数转换器,数据总线为10位并行三态输出,AD5102采用差分输入,可以有效抑制共模噪声。信号采集部分硬件电路图见图2.2图2.2前端采集系统电路图(2)控制核心设计控制核心采用凌阳16位单片机SPCE061,实现数据处理、与FPGA!讯、人机交互以及示波器控制。SPCE061A丰富的中断源、可编程的I/O 口及友好的调试环境为我们的设计提供了方便。凌阳单片机SPCE061?内部结构图如图2.3 :":l_: G曲 *人卅wci.hFLAM 毗Mlfl- -.1 忡靶鼻CPJ-IW4'dP>*?

9、4 lQADC a* «adc*ao僧i«W ttmsiaM»-D08H图2.3凌阳内部结构图(3)运算核心设计本系统以XILINX 100万门FPGA Virtex-II为作为运算核心,它除了内含大量可配置逻辑模块(CLB),输人输出模块(IOB)逻辑资源和布线资源外,还具有以下特点:a)内部时钟速度可达420MHz且具有丰富的全局时钟资源和数字时钟管理模块 (DCM),可以获得较小的时钟抖动。b)具有为算术运算而特别设计的硬件结构,如18 bit X18 bit嵌入式硬件乘法器、快速进位链等。c)包含丰富的模块化RAM这些特点简化了逻辑设计,缩短了设计时间,为

10、实现高速、实时DSP处理提供了极大的便利(4)示波器显示部分设计X-Y轴信号输出采用速度为10MH的 TLC7528双路D/A转换器,由凌阳单片机SPCE061控制,电路图如图2.4 :UliEfidVtBLSIosaoudUTBcesDSEira?RFSrt-PE®V例11目 ravsi ttrijii y w<r -. OXiSflBM.SgxRdlHi-GF1 Tierraiesw_KBaTIfbT图2.4示波器控制电路考虑到输出的谱线较为陡峭的情况,为避免因为运放摆率过小,显示时造成拖尾现象,选用压摆率为12V/US的运放LF356<(5) 供电设计电源系统是影响

11、系统稳定性的重要因素。由于系统上的器件要求供电有1.5V,1.8V,3.3V,1 5V,1 12V等多种电压,电源系统采用了多路独立供电的方式,1.5V/1.8V/3.3V 都由专用电源芯片 TPS54613独立供电,_5V由7805/7905提供, _ 12V由7812/7912提供。同时,由于整个系统主要有高速的数字器件组成。系统在工作中,数字器件会在电源和地上引入大量的脉冲干扰。对于高精度小信号的A/D转换器,为了保证采样精度,要求采样A/D的电源和地的噪声很小。解决方案是通过n型滤波隔离数字部分和模拟部分供电,同时对数字地与模拟地实现布线隔离,并且通过电感把两部分地单点连接。电路图如图

12、2.5 :图2.5 n型网络供电部分硬件电路图见图2.6L汕2、软件设计(1)单片机部分软件开发平台:操作系统 Windows Xp sp2开发环境u'nSP IDE 184软件流程图如图2.7所示:一*£|图2.6供电部分硬件电路图开始系统初始化显示菜单槪下1标定频谱显示般存储频谱回放设定中心频率淞中6«5率选择己有频谱王4r设定13频带宽设定扫頻带宽41图2.7单片机软件流程(2) FPGA 部分软件开发平台:操作系统 Windows Xp sp2开发环境 XILINX System Generator 6.3 XILINX ISE 6.3 MATLAB 6.5

13、综合工具 Synplify Pro 7.6仿真环境 ModleSim 6.5Se 调试工具 ChipScope 6.3本系统FPGA件设计采用Xilinx 提供的DSP设计工具System Generator首先利用 System Generator 对需要的操作进行数字的描述,然后得出算法的硬件实现。 System Generator 设计的流程包括以下几个步骤:1)用数学语言来描述算法;2)在设计环境中实现算法,开始时用双精度;3)把双精度算法转换成固定点算法;4)把设计翻译成有效的硬件。Simulink提供了一个可以创建和仿真动态系统的可视化的环境,System Generator以一个

14、被称为Xilinx blockset块包含在MATLAB/Simulink库里,并且 System Generator 作为一个软件把 Simulink 模型翻译成一个硬件可执行的模型。 System Generator 把在 Simulink 中定义的系统参数对应成硬件实现时的实体、构造体、输入输岀口、信号和属性。此外,System Generator自动地为FPGA勺综合,HDL仿真和实现工具生成命令档。System Generator设计流程如图 2.8 所示:XI阵(迪排IltlTiXKtttSttWKttWKSit/MHSit/MH图2.8 SG设计流程扫频源需要输出的频率经过单片机

15、计算得到相对应得DDS相位累加值,通过Gateway In1送入DDS模块。锁存信号经过Gateway In2输入FPGA其上升沿将Gateway In1输入的相位累加值锁存到DDS中的相位累加值寄存器中。此时DDS模块将会输出对应频率的扫频信号经过前级数据调理的输入信号与扫频信号在混频器Mult中相乘后,频谱被搬移到零频和频率处。将该信号经过FIR低通滤波器滤除频率处的频率分量。检波模块Convert用于将零频附近的信号的最大峰值提取出来,经过Gateway Out发送回单片机。三、测试说明1、单频信号的频谱测试输入信号为单频信号,有效值20mV mV在10KHz至30MHz范围内测试信号中

16、心频率,并观察示波器显示谱线位置。图。2、调幅信号的频谱测试输入信号为调幅信号,有效值20mV+5表3.1单频信号的频谱测试信号源输出频率10KHz500KHz1MHz5MHz10MHz30MHz实测频率10KHz500K1000K5005K10000K30005KmV调制度30%,调制信号频率为20kHz在10KHZ至30MHz范围内测试信号中心频率,并观察示波器显示频谱表3.2调幅信号的频谱测试信号源输出频率10KHz500KHz1MHz5MHz10MHz30MHz实测频率10 KHz510 KHz 1010 KHz5010 KHz9995 KHz29995KHz3、调频信号的频谱测试输入

17、信号为调频信号,有效值20mVmV调频波频偏为20KHz调制信号频率为1KHz在10KHz至30MHz范围内测试信号中心频率,并观察示波器显示频谱图表3.3调频信号的频谱测试信号源输出频率10KHz500KHz1MHz5MHz10MHz30MHz实测频率5K495K995 KHz5010 KHz9990 KHz30010KH;4、信号识别准确度测试输入信号依次为等幅信号,调幅信号,调频信号,有效值20mV+5mV调幅波调制度30%,调频波频偏为20KHZ调制信号频率为1KHz在10KHz至30MHz范围内测试信号识别准确性。表3.4调频信号的频谱测试信号源输出频率10KHz500KHz1MHz5MHz10MH;30MHz准确度正确正确正确正确正确正确5、测试结果分析本系统在10KHz到30MHz的频率范围内,可准确测定待测信号中心频率和识别信号调制类型,示波器

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025年cet 412月考试试题答案

- 河北省2022初中物理易丢分题型模拟训练 附避坑指南答案

- 放疗技师规培2022面试高分通关专属题库及标准答案

- 2026年关于创城的测试题及答案

- 2022烟草送货员面试冷门考点及对应标准答案

- 2026年龙生九子相关测试题及答案

- 2020年中小学大队委员笔试题库及答案 可直接背诵备考

- 2026年留置看护队员试题及答案

- 2026宇视科技笔试真题及答案 刷完直接进面试

- 2024年文学概论期末试题及答案 附简答论述万能答题模板

- 七律二首《送瘟神》课件

- Unit 5 Reading 2 电子教案 译林版英语七年级上册

- 2025年新能源汽车高压系统电气安全防护技术产品创新与设计报告

- 能源计量知识培训课件

- 网络应急知识培训课件

- 2025年4月全国自考《质量管理(一)》试题及答案

- 2025江苏苏州市中医医院、西苑医院苏州医院招聘编外工作人员拟聘模拟试卷及答案详解(必刷)

- 第一季度销售总结工作汇报

- 数字标注师能力评价规范

- 钉钉介绍的课件

- 中公国考面试协议班合同

评论

0/150

提交评论