版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、. . . . 基于CPLD和单片机的频率计设计引言:随着电子技术与计算机技术的不断发展,以单片机为核心的测量控制系统层出不穷。在被测信号中,较多的是模拟和数字开关信号,而且还经常遇到以频率为参数的被测信号,例如流量、转速、晶体压力传感器以与经过参变量一频率转换后的信号等。本次试验采用测频法,通过方案优化,达到了较高的精度。该测频系统的设计采用AT89C51单片机和具有部结构重组、现场可编程的CPLD芯片相结合起来,实现了对IHz10MHz信号频率的高精度测量。系统的整体稳定性和精度较高,达到了测频对精准度的要求。正文:1、 实验设计原理1.1 实验基本框架 图一传统的测频原理是在一定的时间间

2、隔T测某个周期信号的重复变化次数N,其频率可表示为f=N/T,其原理框图如图2所示。这种测量方式的精度随被测信号频率的下降而降低。 图二关于误差的分析将在下文中阐述。1.2 本实验采用等精度测频的原理为: 首先,Clock即标准时钟信号进过分频产生周期为1.25s,占空比为80%的闸门信号,从而闸门宽度为1s,将分频产生的信号和被测信号相与的结果即为计数器的技术时钟信号,在这1s的时间宽度技术到的结果就是被测信号的频率值,通过多路选择器,有单片机发送地址,每次四位将数据传送给单片机,经过单片机的代码转换,使用7个8段数码管显示。具体原理如图三所示。 图三1.3 CPLD模块逻辑设计1.3.1分

3、频模块的实现 分频器采用25位的二进制计数器,产生周期1.25s,占空比80%的宽度为1s的闸门信号。下图为在ISE仿真环境下的闸门输出。 图四1.3.2计数器 计数器采用28的BCD码计数,局部计数方式如下:if(en=1'b1)&&(clr=1'b0)&&(q3<4'b1001) begin q3 =q3+4'b0001; end else beginq3=4'b0000;下图为在ISE仿真环境下的计数结果: 图五鉴于数据较大,所以,我们仿真时候只选取了12位数据,结果是正确的。1.3.2多路选择器有单片机提供3

4、位地址信号,每次送四位数据给单片机,传送7次数据即可。1.4 单片机主控模块(1) P1口用来作为数码管的7个位选信号;(2) P2口用来向单片机提供段选码;(3) Latch:即与案例框图中由分频链给单片机的时钟信号,为了实现单片机与CPLD工作的同步而做的;在Latch信号为高电平期间单片机取数据,而此时,CPLD由于闸门为低电平使得计数停止;在Latch为低电平时,单片机部取数,而CPLD在计数。从而保证两者的正常工作。(4) P0口的低四位用来取数,P3口地高三位用来传送地址;(5) 单片机采用定时中断显示,每1ms改变一位,实现动态显示。2、 测频精度分析 图六 计数法测频误差示意图

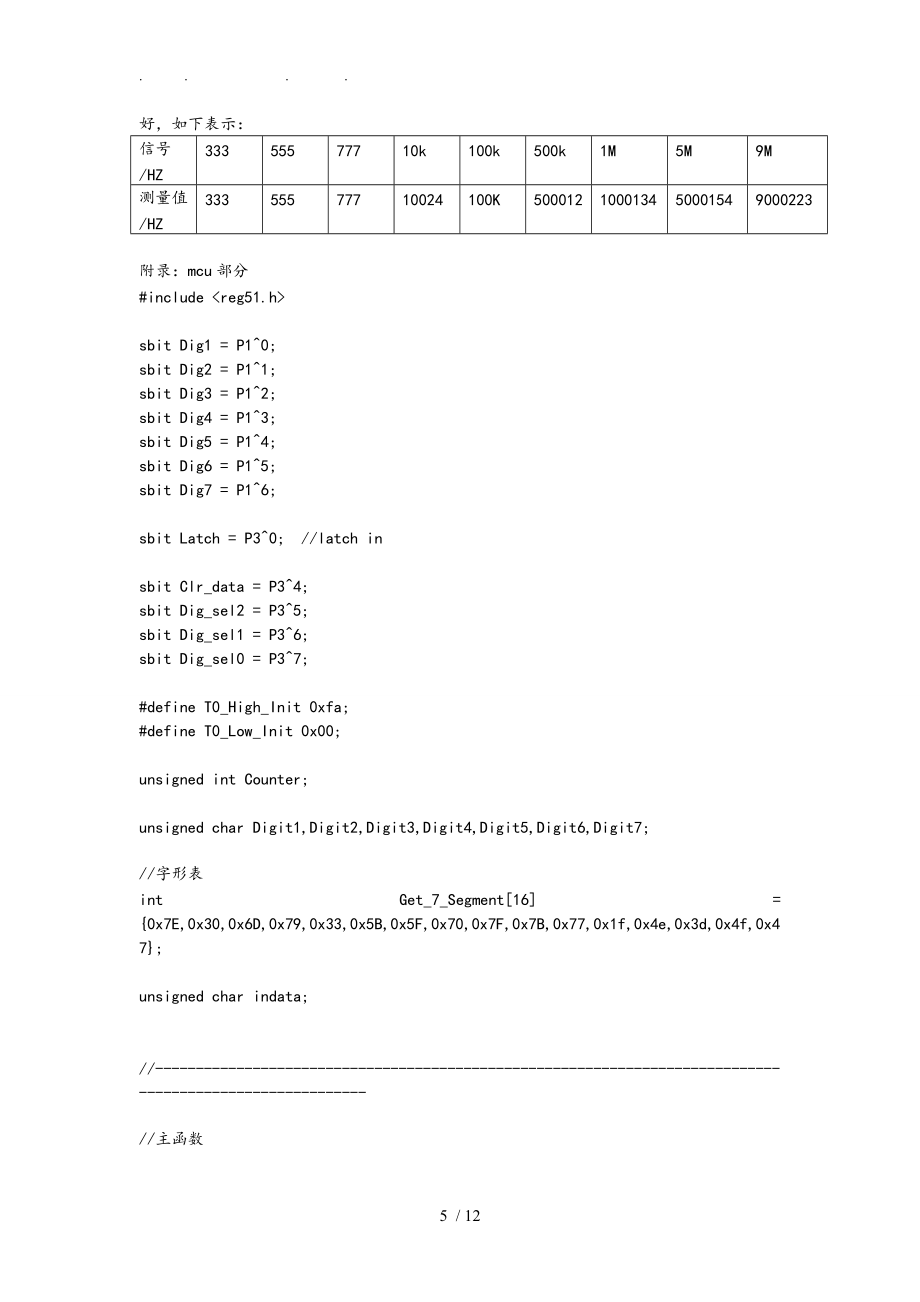

5、 说明:f x =由误差合成公式有上式中第一项为量化误差,是由于被测信号与门控闸门信号不相关引起的。 设主门的开启时间为T ,被测信号周期为Tx ,主门开启时刻至下一个计数脉冲的前沿为, 主门关闭时刻至下一个计数脉冲的前沿为,如上图所示。其最大误差为±1 个量化单位,则最大量化误差的相对值为。由式得到,被测频率越高,闸门时间越长,则量化误差越小. 但闸门时间太长,则降低测量速度,且受到显示位数的限制。3、 实验结果在试验中,频率计在1HZ到1KHZ段的误差很小,几乎可仪忽略不计,在高频时的进度也很好,如下表示:信号/HZ33355577710k100k500k1M5M9M测量值/HZ

6、33355577710024100K500012100013450001549000223附录:mcu部分#include <reg51.h>sbit Dig1 = P10;sbit Dig2 = P11;sbit Dig3 = P12;sbit Dig4 = P13;sbit Dig5 = P14;sbit Dig6 = P15;sbit Dig7 = P16;sbit Latch = P30; /latch insbit Clr_data = P34;sbit Dig_sel2 = P35;sbit Dig_sel1 = P36;sbit Dig_sel0 = P37; #de

7、fine T0_High_Init 0xfa;#define T0_Low_Init 0x00;unsigned int Counter;unsigned char Digit1,Digit2,Digit3,Digit4,Digit5,Digit6,Digit7;/字形表int Get_7_Segment16 = 0x7E,0x30,0x6D,0x79,0x33,0x5B,0x5F,0x70,0x7F,0x7B,0x77,0x1f,0x4e,0x3d,0x4f,0x47;unsigned char indata;/-/主函数/初始化函数void Initial(void) Counter =

8、0;TMOD = 0x11; /定时器工作方式TH0 = T0_High_Init;TL0 = T0_Low_Init; /设置定时器初值TR0 = 1; /启动定时器ET0 = 1; /允许定时器中断EA = 1; /开中断/延时void delay()int ti;for(ti=0;ti<10;ti+) /判断Latch是否为高电平int latch_high(void) int reci; /返回值 if(Latch) delay(); if(Latch) reci = 1; else reci = 0; else reci = 0; return reci;/判断Latch是否为

9、低电平int latch_low(void) int reci; /返回值 if(!Latch) delay(); if(!Latch) reci = 1; else reci = 0; else reci = 0; return reci;void get_data(void) Dig_sel2 = 0; Dig_sel1 = 0; Dig_sel0 = 0; delay(); indata = P0; Digit7 = indata & 0x0f; Dig_sel0 = 1; delay(); indata = P0; Digit6 = indata & 0x0f; Dig

10、_sel1 = 1; Dig_sel0 = 0; delay(); indata = P0; Digit5 = indata & 0x0f; Dig_sel0 = 1; delay(); indata = P0; Digit4 = indata & 0x0f;/* Dig_sel2 = 1; Dig_sel1 = 0; Dig_sel0 = 0; delay(); indata = P0; Digit3 = indata & 0x0f; Dig_sel0 = 1; delay(); indata = P0; Digit2 = indata & 0x0f; Dig

11、_sel1 = 1; Dig_sel0 = 0; delay(); indata = P0; Digit1 = indata & 0x0f; /主函数void main() Initial(); while( 1 ) while( latch_high() ); get_data(); Clr_data = 0; delay(); Clr_data = 1; while( latch_low() ); /-/中断/显示void Display_Digit(unsigned int Digit_Selected)if( Digit_Selected = 1 )Dig7 = 1;P2 =

12、Get_7_SegmentDigit1;Dig1 = 0; if( Digit_Selected = 2 )Dig1 = 1;P2 = Get_7_SegmentDigit2;Dig2 = 0;if( Digit_Selected = 3 )Dig2 = 1;P2 = Get_7_SegmentDigit3;Dig3 = 0;if( Digit_Selected = 4 )Dig3 = 1;P2 = Get_7_SegmentDigit4;Dig4 = 0; if( Digit_Selected = 5 )Dig4 = 1;P2 = Get_7_SegmentDigit5;Dig5 = 0;i

13、f( Digit_Selected = 6 )Dig5 = 1;P2 = Get_7_SegmentDigit6;Dig6 = 0;if( Digit_Selected = 7 )Dig6 = 1;P2 = Get_7_SegmentDigit7;Dig7 = 0;/中断处理函数void display(void) interrupt 1ET0 = 0;TR0 = 0;TH0 = T0_High_Init;TL0 = T0_Low_Init; /重装定时器初值TR0 = 1;if( +Counter = 8 )Counter = 1;Display_Digit(Counter); /显示ET0

14、 = 1;Cpld部分module fcounter(clk, clr, selector, single, gate, data); input clk; input clr; input 2:0selector; input single; output gate; output 3:0data; reg 3:0data; wire gate; reg 24:0gcount; reg 27:0count; reg a,b,c,d,e,f,g; wire clock; wire ssingle;assign gate=clock;always /输出数据begincase (selector

15、)3'b000: data=count3:0;3'b001: data=count7:4;3'b010: data=count11:8;3'b011: data=count15:12;3'b100: data=count19:16;3'b101: data=count23:20;3'b110: data=count27:24;3'b111: ;endcaseendalways(posedge clk) /时钟闸门beginif(gcount24:0=25'h01e8480) gcount=25'h185ee00;e

16、lse gcount=gcount+1;endassign clock=gcount24;assign ssingle=single&clock;/有效信号always(negedge ssingle or negedge clr)/计数begin if(clr=0) count=0; else if(count3:0=4'h9) begin if(count7:4=4'h9) begin if(count11:8=4'h9) begin if(count15:12=4'h9) begin if(count19:16=4'h9) begin if(count23:20=4'h9) begin if(count27:24=4'h9) count27:24=0; else count27:24=count27:24+1; count23:20=0; end else count23:2

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 一年质量工作总结

- 2024年计算机项目管理试题及答案

- 学期教育艺术鉴赏:儿童画

- 完善医院质量管理体系的工作计划

- 促进语言表达的系列活动计划

- 整合资源与搭建合作平台计划

- 合理分配资源的管理艺术计划

- 如何提升社区环境美化计划

- 2024年人力资源师考试回顾试题及答案

- 2024年投资咨询理论与实践试题及答案

- (3月省质检)福建省2025届高三毕业班适应性练习卷英语试卷(含答案)

- 秸秆破壁菌酶研发项目可行性研究报告(范文参考)

- 2025年上半年贵州黔东南州各县(市)事业单位招聘工作人员1691人笔试易考易错模拟试题(共500题)试卷后附参考答案

- 2025新疆机场(集团)有限责任公司阿克苏管理分公司第一季度招聘(75人)笔试参考题库附带答案详解

- 2025年阿斯利康能力测试题及答案

- 东莞市劳动合同模板6篇

- 《医疗机构重大事故隐患判定清单(试行)》知识培训

- TCACM 1470-2023 胃癌前病变治未病干预指南

- Unit 4 Eat Well(大单元教学设计)2024-2025学年七年级英语下册同步备课系列(人教版2024)

- 全国计算机等级考试《三级信息安全技术》专用教材【考纲分析+考点精讲+真题演练】

- 2024年天翼云认证运维工程师考试复习题库(含答案)

评论

0/150

提交评论