版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

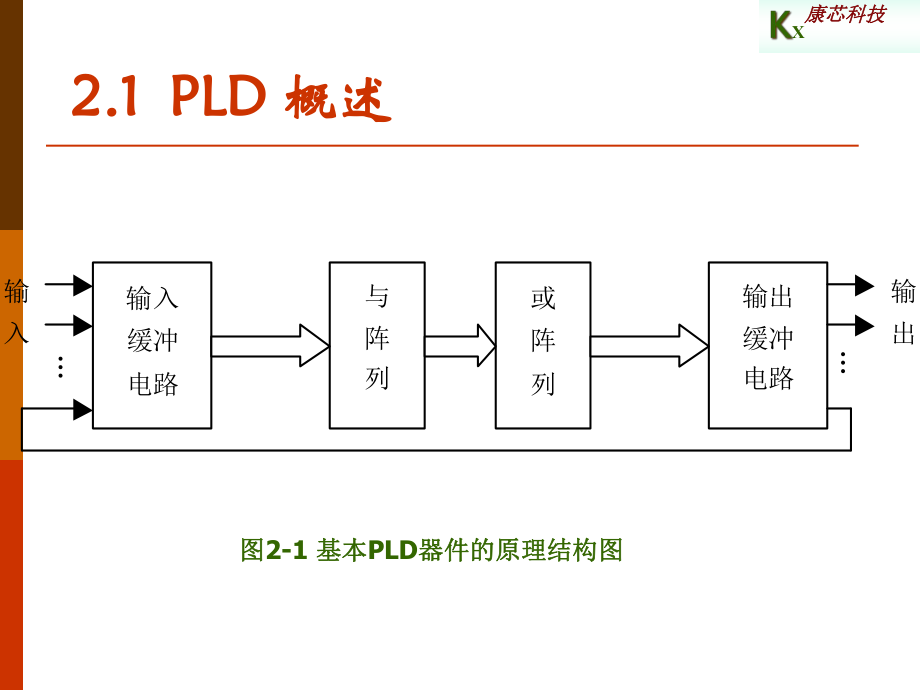

1、第第2 2章章X康芯科技康芯科技X康芯科技康芯科技2.1 PLD 2.1 PLD 概述概述 图图2-1 基本基本PLD器件的原理结构图器件的原理结构图 输入缓冲电路与阵列或阵列输出缓冲电路输入输出X康芯科技康芯科技2.1.1 PLD2.1.1 PLD的发展历程的发展历程 熔丝编程的熔丝编程的PROM和和PLA器件器件 AMD公公司推出司推出PAL器件器件 GAL器件器件 FPGA器器件件 EPLD器器件件 CPLD器器件件 内嵌复杂内嵌复杂功能模块功能模块的的SoPC 20世纪世纪70年代年代 20世纪世纪70年代末年代末 20世纪世纪80年代初年代初 20世纪世纪80年代中期年代中期 20世

2、纪世纪80年代末年代末 进入进入20世纪世纪90年代后年代后 2.1 PLD 概述概述 X康芯科技康芯科技2.1.2 PLD2.1.2 PLD的分类的分类 可编程逻辑器件(PLD) 简单 PLD 复杂 PLD PROM PAL PLA GAL CPLD FPGA 图图2-2 按集成度按集成度(PLD)分类分类 2.1 PLD 概述概述 X康芯科技康芯科技2.1.2 PLD2.1.2 PLD的分类的分类 1熔丝熔丝(Fuse)型器件。型器件。 2反熔丝反熔丝(Anti-fuse)型器件型器件 。 3EPROM型。称为紫外线擦除电可编程逻辑器件型。称为紫外线擦除电可编程逻辑器件 。 4EEPROM

3、型型 。 5SRAM型型 。 6Flash型型 。 2.1 PLD 概述概述 从编程工艺上划分从编程工艺上划分: : X康芯科技康芯科技2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 2.2.1 2.2.1 电路符号表示电路符号表示 图图2-3 常用逻辑门符号与现有国标符号的对照常用逻辑门符号与现有国标符号的对照 X康芯科技康芯科技2.2.1 2.2.1 电路符号表示电路符号表示 图图2-4 PLD的互补缓冲器的互补缓冲器 图图2-5 PLD的互补输入的互补输入 图图2-6 PLD中与阵列表示中与阵列表示 图图2-7 PLD中或阵列的表示中或阵列的表示 图图2-8 阵列线连接表示

4、阵列线连接表示 X康芯科技康芯科技2.2.2 PROM 2.2.2 PROM 图图2-9 PROM基本结构基本结构 地址译码器存储单元阵列0A1A1nA0W1W1pW0F1F1mFnp22.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 X康芯科技康芯科技2.2.2 PROM 2.2.2 PROM 0111201110110.AAAWAAAWAAAWnnnn PROM中的地址译码器是完成中的地址译码器是完成PROM存储阵列的行的选择,存储阵列的行的选择,其逻辑函数是:其逻辑函数是: 2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 X康芯科技康芯科技2.2.2 PROM

5、2.2.2 PROM 行单元的值列是存储单元阵列第而,其中11 2 1, 1pmMpmpn2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 01, 011, 111, 1101 , 011 , 111 , 1100, 010, 110, 10WMWMWMFWMWMWMFWMWMWMFmmpmpmpppp.X康芯科技康芯科技2.2.2 PROM 2.2.2 PROM 与阵列(不可编程)或阵列(可编程)0A1A1nA0W1W1pW0F1F1mFnp2图图2-10 PROM的逻辑阵列结构的逻辑阵列结构 2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 X康芯科技康芯科技2.2

6、.2 PROM 2.2.2 PROM 图图2-11 PROM表达的表达的PLD阵列图阵列图 与阵列(固定)或阵列(可编程)0A1A1A1A0A0A1F0F1010AACAAS2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 X康芯科技康芯科技2.2.2 PROM 2.2.2 PROM 图图2-12 用用PROM完成半加器逻辑阵列完成半加器逻辑阵列 01110100AAFAAAAF与阵列(固定)或阵列(可编程)0A1A1A1A0A0A1F0F2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 X康芯科技康芯科技2.2.3 PLA 2.2.3 PLA 图图2-13 PLA逻辑

7、阵列示意图逻辑阵列示意图 与阵列(可编程)或阵列(可编程)0A1A1A1A0A0A1F0F2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 X康芯科技康芯科技2.2.3 PLA 2.2.3 PLA 图图2-14 PLA与与 PROM的比较的比较 0A1A1F0F2A2F0A1A1F0F2A2F2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 X康芯科技康芯科技2.2.4 PAL 2.2.4 PAL 图图2-15 PAL结构结构 图图2-16 PAL的常用表示的常用表示 0A1A1F0F0A1A1F0F2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 X康芯科

8、技康芯科技图图2-17 一种一种PAL16V8的部分结构图的部分结构图 11100100R11100100RQQD11100100R11100100RVccSG1SL07SL17SG0SL0619I/O711100100R11100100RQQD11100100R11100100RVccSG1SL06SL16SG1SL0618I/O61CLK/I02I13I2078150 3 4 7 8121115 1619 2023 2427 2831X康芯科技康芯科技2.2.5 GAL 2.2.5 GAL 2.2 2.2 低密度低密度PLDPLD可编程原理可编程原理 GALGAL即通用阵列逻辑器件,首次在

9、即通用阵列逻辑器件,首次在PLDPLD上采用了上采用了EEPROMEEPROM工艺,使得工艺,使得GALGAL具有电可擦除重复编程的特点,具有电可擦除重复编程的特点,彻底解决了熔丝型可编程器件的一次可编程问题。彻底解决了熔丝型可编程器件的一次可编程问题。GALGAL在在“与与- -或或”阵列结构上沿用了阵列结构上沿用了PALPAL的与阵列可编程、或的与阵列可编程、或阵列固定的结构,但对阵列固定的结构,但对PALPAL的输出的输出I/OI/O结构进行了较大的结构进行了较大的改进,在改进,在GALGAL的输出部分增加了输出逻辑宏单元的输出部分增加了输出逻辑宏单元OLMC(OutputOLMC(Ou

10、tput Macro Cell) Macro Cell)。 X康芯科技康芯科技2.3 CPLD2.3 CPLD的结构与可编程原理的结构与可编程原理 图图2-18 MAX7000系列的单个宏单元结构系列的单个宏单元结构 X康芯科技康芯科技图图2-19 MAX7128S的结构的结构 1 1逻辑阵列块逻辑阵列块(LAB) (LAB) 2.3 CPLD2.3 CPLD的结构与可编程原理的结构与可编程原理 X康芯科技康芯科技2 2宏单元宏单元 全局时钟信号全局时钟信号全局时钟信号由高电平有效的时钟信号使能全局时钟信号由高电平有效的时钟信号使能 用乘积项实现一个阵列时钟用乘积项实现一个阵列时钟2.3 CP

11、LD2.3 CPLD的结构与可编程原理的结构与可编程原理逻辑阵列逻辑阵列MAX7000MAX7000系列中的宏单元系列中的宏单元 乘积项选择矩阵乘积项选择矩阵可编程寄存器可编程寄存器 X康芯科技康芯科技3 3扩展乘积项扩展乘积项 图图2-20 共享扩展乘积项结构共享扩展乘积项结构 2.3 CPLD2.3 CPLD的结构与可编程原理的结构与可编程原理X康芯科技康芯科技3 3扩展乘积项扩展乘积项 图图2-22 并联扩展项馈送方式并联扩展项馈送方式 共享扩展项共享扩展项 并联扩展项并联扩展项 X康芯科技康芯科技4 4可编程连线阵列可编程连线阵列(PIA) (PIA) 图图2-22 PIA信号布线到信

12、号布线到LAB的方式的方式 2.3 CPLD2.3 CPLD的结构与可编程原理的结构与可编程原理X康芯科技康芯科技5 5I/OI/O控制块控制块 图图2-23 EPM7128S器器件的件的I/O控制块控制块 X康芯科技康芯科技2.4 FPGA2.4 FPGA的结构与工作原理的结构与工作原理 在在FPGAFPGA开发技术的学习中,对于其硬件的了解主要应该注开发技术的学习中,对于其硬件的了解主要应该注意以下意以下5 5个方面:个方面: (1 1)FPGAFPGA的工作电源的类型和接入要求。的工作电源的类型和接入要求。 (2 2)编程口。)编程口。 (3 3)I/OI/O端口、多用途端口、专用输入口

13、、全局控制口、端口、多用途端口、专用输入口、全局控制口、LVDSLVDS口、锁相环时钟输入输出口的电气性能和使用方法。口、锁相环时钟输入输出口的电气性能和使用方法。 (4 4)FPGAFPGA内部的嵌入式模块。内部的嵌入式模块。 (5 5)配置器件。)配置器件。 X康芯科技康芯科技2.4.1 2.4.1 查找表逻辑结构查找表逻辑结构 图图2-24 FPGA查找表单元查找表单元 查找表LUT输入1输入2输入3输入4输出2.4 FPGA2.4 FPGA的结构与工作原理的结构与工作原理X康芯科技康芯科技0000010100000101161RAM输入A输入B输入C输入D查找表输出多路选择器2.4.1

14、 2.4.1 查找表逻辑结构查找表逻辑结构 图图2-25 FPGA查找表单元内部结构查找表单元内部结构 X康芯科技康芯科技2.4.2 Cyclone2.4.2 Cyclone系列器件的结构与原理系列器件的结构与原理 图图2-26 Cyclone LE结构图结构图 X康芯科技康芯科技2.4.2 Cyclone2.4.2 Cyclone系列器件的结构与原理系列器件的结构与原理 图图2-27 Cyclone LE普通模式普通模式 X康芯科技康芯科技2.4.2 Cyclone2.4.2 Cyclone系列器件的结构与原理系列器件的结构与原理 图图2-28 Cyclone LE动态算术模式动态算术模式

15、X康芯科技康芯科技2.4.2 Cyclone2.4.2 Cyclone系列器件的结构与原理系列器件的结构与原理 图图2-29 Cyclone LAB结构结构 X康芯科技康芯科技2.4.2 Cyclone2.4.2 Cyclone系列器件的结构与原理系列器件的结构与原理 图图2-30 LAB阵列阵列 X康芯科技康芯科技2.4.2 Cyclone2.4.2 Cyclone系列器件的结构与原理系列器件的结构与原理 图图2-31LAB控制信号生成的逻辑图控制信号生成的逻辑图 X康芯科技康芯科技2.4.2 Cyclone2.4.2 Cyclone系列器件的结构与原理系列器件的结构与原理 图图2-32 快

16、速进位选择链快速进位选择链 X康芯科技康芯科技图图2-33 LUT链和寄存器链的使用链和寄存器链的使用 2.4.2 Cyclone2.4.2 Cyclone系列器件的结构与原理系列器件的结构与原理 2.4 FPGA2.4 FPGA的结构与工作原理的结构与工作原理 X康芯科技康芯科技图图2-34 LVDS连接连接 2.4.2 Cyclone2.4.2 Cyclone系列器件的结构与原理系列器件的结构与原理 2.4 FPGA2.4 FPGA的结构与工作原理的结构与工作原理 X康芯科技康芯科技2.5 2.5 硬件测试技术硬件测试技术 2.5.1 2.5.1 内部逻辑测试内部逻辑测试 在ASIC设计中

17、的扫描寄存器,是可测性设计的一种,原理是把ASIC中关键逻辑部分的普通寄存器用测试扫描寄存器来代替,在测试中可以动态地测试、分析设计其中寄存器所处的状态,甚至对某个寄存器加以激励信号,改变该寄存器的状态。 X康芯科技康芯科技2.5.2 JTAG2.5.2 JTAG边界扫描测试边界扫描测试 引引 脚脚描描 述述功功 能能TDI测试数据输入测试数据输入(Test Data Input)测试指令和编程数据的串行输入引脚。数据在测试指令和编程数据的串行输入引脚。数据在TCK的上升沿移入。的上升沿移入。TDO测试数据输出测试数据输出(Test Data Output)测试指令和编程数据的串行输出引脚,数

18、据在测试指令和编程数据的串行输出引脚,数据在TCK的下降沿移出。如果数据没有被移出时,该引脚处于的下降沿移出。如果数据没有被移出时,该引脚处于高阻态。高阻态。TMS测试模式选择测试模式选择(Test Mode Select)控制信号输入引脚,负责控制信号输入引脚,负责TAP控制器的转换。控制器的转换。TMS必须在必须在TCK的上升沿到来之前稳定。的上升沿到来之前稳定。TCK测试时钟输入测试时钟输入(Test Clock Input)时钟输入到时钟输入到BST电路,一些操作发生在上升沿,而另电路,一些操作发生在上升沿,而另一些发生在下降沿。一些发生在下降沿。TRST测试复位输入测试复位输入(Te

19、st Reset Input)低电平有效,异步复位边界扫描电路低电平有效,异步复位边界扫描电路(在在IEEE规范中,规范中,该引脚可选该引脚可选)。表表2-1 边界扫描边界扫描IO引脚功能引脚功能 2.5 2.5 硬件测试技术硬件测试技术 X康芯科技康芯科技2.6 FPGA/CPLD2.6 FPGA/CPLD产品概述产品概述 2.6.1 Lattice2.6.1 Lattice公司公司CPLDCPLD器件系列器件系列 2.6.2 2.6.2 XilinxXilinx公司的公司的FPGAFPGA和和CPLDCPLD器件系列器件系列1. Virtex-4系列系列FPGA 2. Spartan&am

20、p; Spartan-3 & Spartan 3E器件系器件系 3. XC9500 & XC9500XL系列系列CPLD4. Xilinx FPGA配置器件配置器件SPROM X康芯科技康芯科技2.6 FPGA/CPLD2.6 FPGA/CPLD产品概述产品概述 2.6.3 2.6.3 AlteraAltera公司公司FPGAFPGA和和CPLDCPLD器件系列器件系列 1. Stratix II 系列系列FPGA 2. ACEX系列系列FPGA 3. MAX系列系列CPLD 4. Cyclone系列系列FPGA低成本低成本FPGA 5. Cyclone II系列系列FPGA

21、6. MAX II系列器件系列器件 7. Altera宏功能块及宏功能块及IP核核 X康芯科技康芯科技2.6 FPGA/CPLD2.6 FPGA/CPLD产品概述产品概述 2.6.4 2.6.4 ActelActel公司的公司的FPGAFPGA器件器件 2.6.5 2.6.5 AlteraAltera公司的公司的FPGAFPGA配置方式与配置器件配置方式与配置器件 X康芯科技康芯科技2.7 2.7 编程与配置编程与配置 表表2-2 各引脚信号名称各引脚信号名称 基于电可擦除存储单元的基于电可擦除存储单元的EEPROM或或Flash技术。技术。 基于基于SRAM查找表的编程单元。查找表的编程单元。 基于反熔丝编程单元。基于反熔丝编程单元。 引脚引脚12345678910PS模式模式DCKGNDCONF_DONEVCCnCONFIG-nSTATUS-DATA0GNDJATG模式模式TCKGNDTDOVCCTMS-TDIGNDX康芯科技康芯科技2.7 2.7 编程与配置编程与配置 2.7.1 JTAG2.7.1 JTAG方式的在系统编程方式的在系统编程 图图2

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2025高速公路工程施工合同

- 2025美团酒店预订合同协议

- 2025标准房屋租赁合同简化版范本

- 2025如何补办丢失的劳动合同证明

- 2025简易版权转让合同

- 2025专利权许可合同模板

- 2025电梯行业劳动合同范本

- 2025设备租赁合同与协议书范本

- 2025存量房买卖合同书

- 2025融资租赁合同的相关法律特征

- 2025至2030中国射频芯片市场趋势展望及需求前景研究报告

- 应急急救知识课件

- 慢性病管理与护理方法试题及答案

- 定向培养协议书模板

- 文综中考试卷及答案解析

- 鼠伤寒沙门菌护理查房

- 基于CRISPR-Cas9技术探索敲除RAB7A增强肺癌对吉西他滨敏感性的机制研究

- 社区文化活动服务行业跨境出海战略研究报告

- 汽车背户协议合同

- 碳中和目标下的公路建设策略-全面剖析

- 2025年山东省东营市广饶县一中中考一模英语试题(原卷版+解析版)

评论

0/150

提交评论