版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

第二章基本逻辑运算及集成逻辑门第1页,课件共30页,创作于2023年2月学习要求:掌握逻辑代数的基本概念,学会用逻辑函数描述逻辑问题的基本方法。掌握集成逻辑门的功能分析及应用。第2页,课件共30页,创作于2023年2月2.1基本逻辑运算

逻辑运算是逻辑思维和逻辑推理的数学描述.具有“真”“假”两种可能,并且可以判定其“真”“假”的陈述语句叫逻辑变量.用ABCD表示.逻辑变量只有“真”“假”两种可能,在逻辑数学中,把“真”“假”称为逻辑变量的取值,简称逻辑值,也叫逻辑常量,用“1”表示“真”,用“0”表示“假”.虽然“1”和“0”叫逻辑值,但是它们没有“大小”的含义,也无数量的含义.一个结论成立与否,取决于与其相关的前提条件是否成立.结论与前提条件之间的因果关系叫逻辑函数.通常记作F=f(A,B,C…)逻辑函数F也是一个逻辑变量,也叫输出变量.因此它们也只有“1”和“0”两种取值,相对地把A,B,C…叫做输入变量.第3页,课件共30页,创作于2023年2月与运算(•)

只有当决定一事件结果的所有条件同时具备时,结果才能发生.ABF000010100111逻辑式:

F=A•B=ABa.国际流行b.IEEE标准c.中国标准

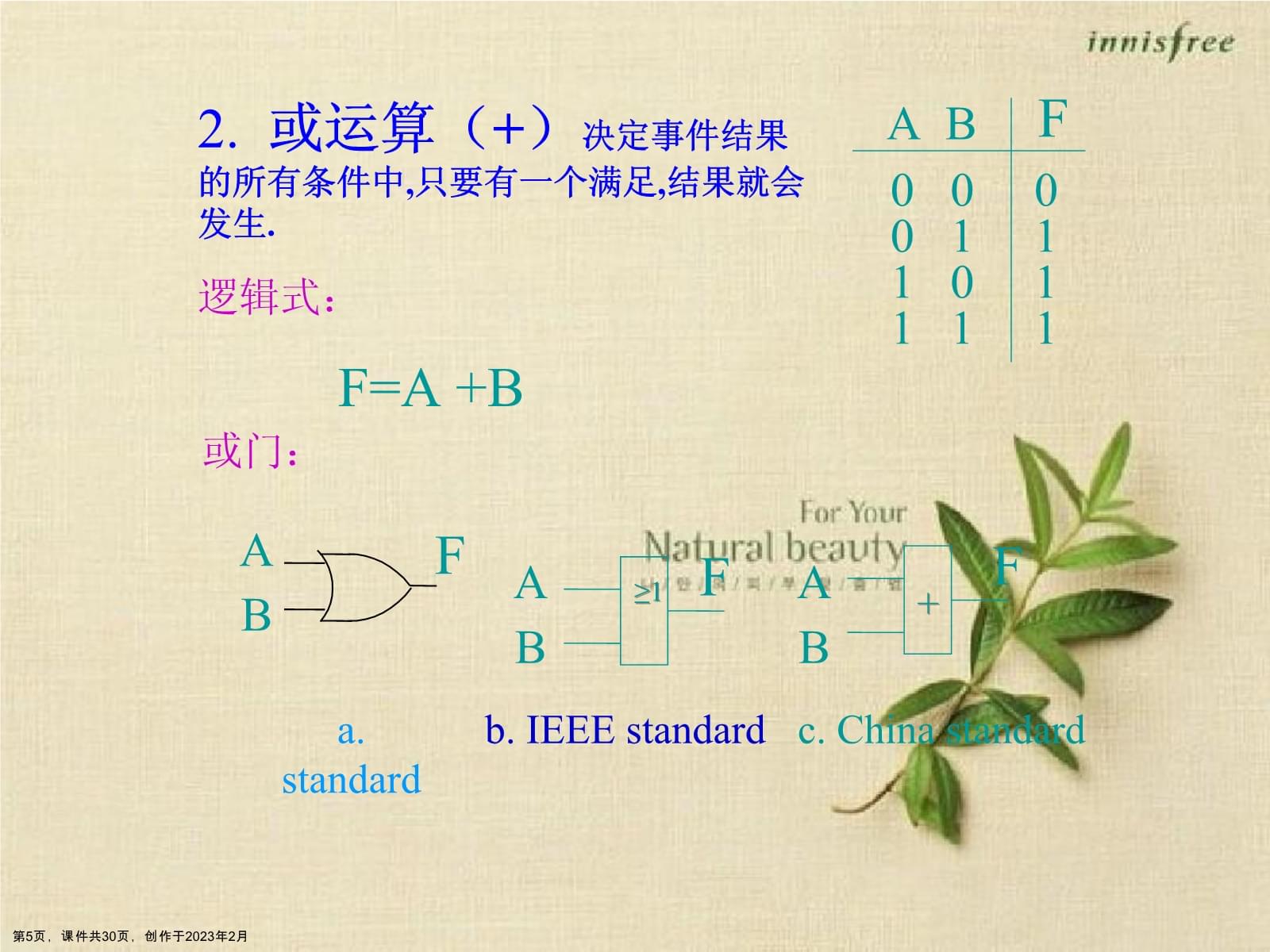

&ABFFFAABB逻辑门:与门第4页,课件共30页,创作于2023年2月ABF0000111011112.或运算(+)决定事件结果的所有条件中,只要有一个满足,结果就会发生.逻辑式:F=A+B≥1+a.standardb.IEEEstandardc.Chinastandard

FBFFAAABB或门:第5页,课件共30页,创作于2023年2月

3.非运算(¯)

非运算是逻辑的否定,当条件具备时,结果不会发生,当条件不具备时,结果一定会发生.逻辑式:F=ĀAF0110○1○a.standardb.IEEEstandardc.Chinastandard

第6页,课件共30页,创作于2023年2月2.2常用复合逻辑1.与非逻辑ABF&

ABF2.或非逻辑或非门第7页,课件共30页,创作于2023年2月3.异或逻辑ABF000011101110=1ABF=ABFABF0010101001114.同或逻辑F=A⊙B=第8页,课件共30页,创作于2023年2月“与或非”逻辑是“与”,“或”,“非”三种基本逻辑的组合.先“与”再“或”最后“非”。5.与或非逻辑&第9页,课件共30页,创作于2023年2月异或逻辑与同或逻辑公式F=A⊕BF=A☉BA⊕A=1A☉A=0A⊕A=0A☉A=1A⊕0=AA☉1=AA⊕1=AA☉0=AA⊕B=A⊕B=A☉BA☉B=A☉B=A⊕BA⊕B=B⊕AA☉B=B☉AA⊕(B⊕C)=(A⊕B)⊕CA☉(B☉C)=(A☉B)☉CA(B⊕C)=AB⊕ACA+(B☉C)=(A+B)☉(A+C)第10页,课件共30页,创作于2023年2月2.3正负逻辑一)正负逻辑:在数字系统中,逻辑值是用逻辑电平表示的.若用逻辑高电平UOH表示逻辑“真”,用逻辑电平UOL表示逻辑“假”,则称为正逻辑;反之,则称为负逻辑.二)逻辑运算的优先级别:在求解逻辑函数时,应首先进行级别高的逻辑运算.三)逻辑运算的完备性:任何数字系统都可以用“与”“或”“非”逻辑门来实现.称它们为完备集.“与非”“或非”“与或非”都是完备集.第11页,课件共30页,创作于2023年2月2.4集成逻辑门

把若干个有源器件和无源器件及其连线,按照一定的功能要求,制作在同一块半导体基片上,这样的产品叫集成电路.若它完成的功能是逻辑功能或数字功能,则称为逻辑集成电路或数字集成电路.最简单的数字集成电路是集成逻辑门.集成逻辑门,按照其组成的有源器件的不同可分为两大类:一类是双极性晶体管逻辑门;另一类是单极性绝缘栅场效应管逻辑门,简称MOS门.第12页,课件共30页,创作于2023年2月2.4.1TTL与非门第一级V1多射级输入(与)TTL与非门的各级工作状态总目录退出><目录

工作原理第二级V2反相第三级V3—V5互补推挽输出高电平3.6V低电平0.3V第13页,课件共30页,创作于2023年2月多射极晶体管的结构及等效电路总目录退出><目录第14页,课件共30页,创作于2023年2月2.4.2TTL与非门的特性与参数⒈电压传输特性DE段(饱和区):Ui>1.4V

V2,V5饱和UT:阀值电压1.4VUOFF:开门电平

UON:

关门电平总目录退出><目录AB段(截止区):Ui<=0.6V

V2,V5截止BC段(线性区)0.6<Ui<1.3V

V2导通,V5截止V2输入电阻=R3V2反相放大CD段(转折区):1.3=<Ui<1.4VV2,V5导通V2输入电阻=R3//Rbe5V2的放大倍数增加Ui第15页,课件共30页,创作于2023年2月ROFF—关门电阻=0.7KRON—关门电阻=2KTTL门输入电阻与输入电压的关系RI<0.7K时UI=VLRI>2K时UI=VH总目录退出><目录2.输入负载特性第16页,课件共30页,创作于2023年2月例:电路如图所示,标出输出电压的高低值第17页,课件共30页,创作于2023年2月3.输出特性①与非门处于输出低电平②与非门处于输出高电平TTL与非门输出低电平的输出特性TTL与非门输出高电平的输出特性总目录退出><目录(此时,IL为灌电流。为保证UOL≤0.35V,通常ILmax≤25mA)(此时,IL为拉电流。为保证UOH输出高电平,通常IL≤14mA)第18页,课件共30页,创作于2023年2月4.扇入扇出系数扇入系数Ni:逻辑门的输入端数。制造时已确定扇出系数No:一个逻辑门驱动同类门的个数。总目录退出><目录第19页,课件共30页,创作于2023年2月5.平均延迟时间tpdtpd=(tPHL+tPLH)12总目录退出><目录第20页,课件共30页,创作于2023年2月2.4.3集电极开路(OC)门集电极开路的门电路(OpenCollectorGate),简称OC门。其电路结构和逻辑符号如下图所示:(a)集电极开路与非门电路(b)OC门逻辑符号BAFR3R2R1BAF总目录退出><目录第21页,课件共30页,创作于2023年2月OC门的输出端可以直接并联在一起,但需要外接电阻OC门的并联处实现“线与”F=AB•CD=AB+CDCBFDAVCC总目录退出><目录第22页,课件共30页,创作于2023年2月2.4.4三态门三态输出门(简称三态门)是在普通门电路的基础上,增加控制端和控制电路构成。其电路结构图和逻辑符号如下图所示:EN=1F=ABEN=0F为高阻ENBFAVCCABENEN总目录退出><目录第23页,课件共30页,创作于2023年2月总目录退出><目录ABENFVCCENABEN第24页,课件共30页,创作于2023年2月Three-stateNOTgateThree-stateANDgateThree-state

NAND

gate总目录退出><目录第25页,课件共30页,创作于2023年2月eF0b1aQuestionF=?总目录退出><

线或(Wired-OR)

F=ae+be目录第26页,课件共30页,创作于2023年2月EN=1时G1工作G2高阻数据从D0D1EN=0时G2工作G1高阻数据从D1D0总目录退出><目录ENEND0D1ENG1G2用三态门实现双向传输第27页,课件共30页,创作于2023年2月Three-stateusedforBus

DisplayPrinterkeysCPU100100Bus总目录退出><目录第28页,课件共30页,创作于2023年2月

Bi-CMOS这种门电路的特点是逻辑部分采用CMOS结构,输出极采用双极型三极管,因此兼有CMOS电路的低功耗和双极型电路低输出内阻的优点。2.4.5Bi-CMOS反相器的两种电路结构型式总目录退出><目录两个双极型输出管的基极接有下拉电阻。

当Vi=ViH时,T2,T4导通,T1,T3截止,Vo=VoL。当Vi=ViL时,T1,T3导通,T2,T4截止,Vo=VoHViVoT1T2T3T4VD第29页,课件共30页,创作于2023年2月用T2,T4取代R1,R2,形成有源下拉式结构。

当=Vi

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 散酒促销活动策划方案(3篇)

- 线管钢钉施工方案(3篇)

- 泸州护栏施工方案(3篇)

- 2026天津市和平区面向社会公开选聘区管国有企业管理人员6人笔试参考题库及答案解析

- 2026年荆州市沙市区事业单位人才引进34人参考考试题库及答案解析

- 健康同行护理科普同行

- 呼吸科护理工作中的安全管理

- 心内科患者的出院指导

- 2026中国通号招聘3人(办公室、战略投资部)备考考试试题及答案解析

- 第四单元10沙滩上的童话

- 河南新乡鹤壁安阳焦作2026年1月高三一模物理试题+答案

- 2026年食品安全快速检测仪器项目可行性研究报告

- 2025年新版八年级上册历史期末复习必背历史小论文范例

- 2026年及未来5年市场数据中国电能计量装置市场竞争格局及投资战略规划报告

- 替人背债合同范本

- 鲁教版(五四学制)(2012)九年级英语全册期末总复习

- 下尿路症状(LUTS)前沿进展综述

- 初一数学2025年上学期单元测试专项训练试卷(含答案)

- 《电机与电气控制技术》电子教案

- 华菱钢铁ESG报告中碳排放信息披露质量评价及优化研究

- 安全生产管理机构设置及人员配备

评论

0/150

提交评论