版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

第三章

组合逻辑电路3.1概述3.2分析方法和设计方法3.3常用的组合逻辑电路器件3.1概述本章重点:

A.组合逻辑电路的分析方法;

B.组合逻辑电路的设计方法;

C.常用组合电路的功能和使用方法(读懂功能表)。对于具体逻辑电路结构仅需了解。常用组合逻辑电路包括:编码器;译码器;数据选择器;加法器;数值比较器2/4/202321、组合逻辑电路的特点数字电路按逻辑功能的特点可分为两大类:

A.组合逻辑电路(时间无关)

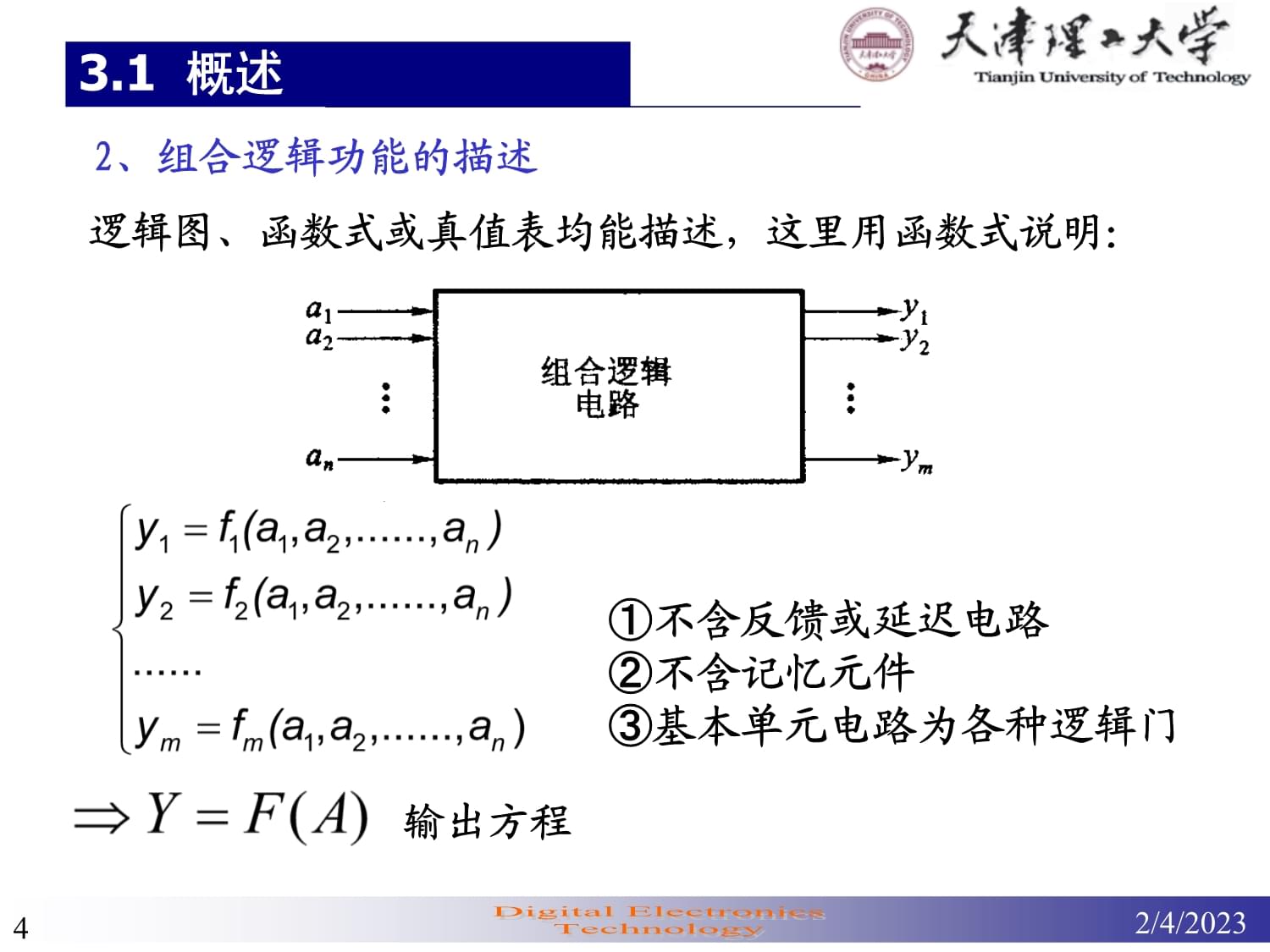

B.时序逻辑电路(时间相关)在组合逻辑电路在任意时刻的输出和状态只取决于该时刻的输入(而与电路原来的状态无关)。3.1概述2/4/202333.1概述2、组合逻辑功能的描述逻辑图、函数式或真值表均能描述,这里用函数式说明:输出方程①不含反馈或延迟电路②不含记忆元件③基本单元电路为各种逻辑门2/4/202341.组合电路的分析步骤

(1)由已知的逻辑图,写出相应的逻辑函数式;(2)对函数式化简;(3)根据化简后的函数式列真值表或者画波形图;(4)找出其逻辑功能。3.2组合逻辑电路的分析与设计方法

例1:试分析图示电路的逻辑功能。解:第一步:由逻辑图可以写输出F的逻辑表达式为:所谓组合逻辑电路的分析,就是根据给定的逻辑电路图,求出电路的逻辑功能。2/4/20235

第二步:可变换为

F=AB+AC+BC

第三步:列出真值表。ABCF00000010010001111000101111011111真值表

第四步:确定电路的逻辑功能。由真值表可知,三个变量输入A,B,C,只有两个及两个以上变量取值为1时,输出才为1。可见电路可实现多数表决逻辑功能。3.2组合逻辑电路的分析与设计方法2/4/202363.2组合逻辑电路的分析与设计方法例2:试分析图示电路的逻辑功能。解:第一步:由逻辑图可以写输出F的逻辑表达式为:第二步:列出真值表。

第三步:确定电路的逻辑功能。由真值表可知,求四个变量输入ABCD二进制,输出十进制9的补码,如ABCD大于9,则F为1。2/4/20237例3:试分析图示电路的逻辑功能。(1)表达式=1=1=1B3B2B1B0G3G2G1G0*3.2组合逻辑电路的分析与设计方法2/4/20238自然二进制码B3B2B1B0

G3G2G1G00000 0000000100010010001100110010010001100101011101100101011101001000110010011101101011111011111011001010110110111110100111111000(2)真值表(3)描述逻辑功能(1)表达式自然二进制码→格雷码的代码转换电路*3.2组合逻辑电路的分析与设计方法格雷码2/4/20239比较简单的组合电路可用画波形图的方法分析:由输入波形逐级画出各输出波形确定逻辑功能例4:若已知A、B、C的波形如图所示,求L的波形,并分析逻辑功能。三位判奇电路或奇校验器CBAZL3.2组合逻辑电路的分析与设计方法2/4/202310课堂练习&&&&ABSC1练习:试分析图示电路的逻辑功能。(半加器)2/4/2023112.组合逻辑电路的设计方法(重点内容)

设计步骤:

(1)分析设计要求,设置输入输出变量并逻辑赋值;

(2)列真值表或波形图;

(3)写出逻辑表达式,并化简;

(4)画逻辑电路图。与分析过程相反,组合逻辑电路的设计是根据给定的实际逻辑问题,求出实现其逻辑功能的最简单的逻辑电路。3.2组合逻辑电路的分析与设计方法2/4/202312

例1:一火灾报警系统,设有烟感、温感和紫外光感三种类型的火灾探测器。为了防止误报警,只有当其中有两种或两种以上类型的探测器发出火灾检测信号时,报警系统产生报警控制信号。设计一个产生报警控制信号的电路。解:(1)分析设计要求,设输入输出变量并逻辑赋值;

输入变量:烟感A、温感B,紫外线光感C;

输出变量:报警控制信号Y;

逻辑赋值:用1表示肯定,用0表示否定。3.2组合逻辑电路的分析与设计方法2/4/202313

(2)列真值表ABCY00000010010001111000101111011111

(3)由真值表写逻辑表达式,并化简:用卡诺图化简得最简式:

(4)画逻辑电路图:3.2组合逻辑电路的分析与设计方法2/4/202314某火车站有特快、直快和慢车三种类型的客运列车进出,试用两输入与非门和反相器设计一个指示列车等待进站的逻辑电路,3个指示灯一、二、三号分别对应特快、直快和慢车。列车的优先级别依次为特快、直快和慢车,要求当特快列车请求进站时,无论其它两种列车是否请求进站,一号灯亮。当特快没有请求,直快请求进站时,无论慢车是否请求,二号灯亮。当特快和直快均没有请求,而慢车有请求时,三号灯亮。例2:指示列车等待进站的电路3.2组合逻辑电路的分析与设计方法实质:用2输入与非门和反相器设计一个3输入(I0、I1、I2)、三输出(L0、L1、L2)的信号排队电路,Ii=1请求进站,Li=1灯亮。2/4/202315实现功能:

I0

=1(I1、I2为X)L0

=1、L1=L2=0I0=0、I1=1(I2为X)L1

=1、L0=L2=0I0=I1

=0、I2=1L2

=1、L0=L1=0(1)依题意列真值表(2)写出逻辑表达式:简化真值表I0

I1I2L0L1L20000001XX10001X010001001完整的真值表?3.2组合逻辑电路的分析与设计方法2/4/202316I0

I1I2L0L1L2000000001001010010011010100100101100110100111100I0I1I2

L0010001111000001111完整的真值表I0I1I2

L10100011110113.2组合逻辑电路的分析与设计方法2/4/202317

1、取值为1用原变量表示;取值为0用反变量表示。

2、取值组合中各变量相“与”;

3、使函数值为1的变量组合相“或”;

由此得到的逻辑式即为最小项表达式!※重申:由真值表如何写出逻辑表达式?I0

I1I2L0L1L20000001XX10001X0100010013.2组合逻辑电路的分析与设计方法2/4/202318(3)变换为与非-与非式(2输入与非门):(三级)(五级)11&&11&1I0I1I2L0L1L2可用一片74LS00(四2输入与非门)一片74LS04(六门反相器)或用二片74LS00实现实现3.2组合逻辑电路的分析与设计方法2/4/202319

二进制码余3码

B3B2B1B0E3E2E1E0000000011100010100200100101300110110401000111501011000601101001701111010810001011910011100101010ΦΦΦΦ

111011ΦΦΦΦ121100ΦΦΦΦ131101ΦΦΦΦ141110ΦΦΦΦ151111ΦΦΦΦ(2)卡诺图(1)真值表3.2组合逻辑电路的分析与设计方法例2:将十六进制码转换成余3BCD码2/4/202320(3)表达式3.2组合逻辑电路的分析与设计方法(4)电路图2/4/202321课堂练习:设计一个监视交通信号灯状态的逻辑电路如果信号灯出现故障,Z为1RAGZ参考答案如上用‘1’表示灯亮,“0”表示灯灭;用Z表示输出,且“1”表示有故障。2/4/202322比较常用的组合逻辑部件有编码器、译码器、数据选择器、加法器和数值比较器等等。1.编码器

3.3常用组合逻辑电路部件用二进制代码表示文字、符号或者数码等特定对象的过程,称为编码。实现编码的逻辑电路,称为编码器。普通编码器:83编码器优先编码器:83优先编码器(CD4532)4线-2线普通及优先编码器见P148(自学内容)2/4/2023233.3常用组合逻辑电路部件(1)普通编码器—8线-3线编码器

I0

I1I2

I3I4

I5

I6

I7Y2Y1Y010000000000010000000010010000001000010000011000010001000000010010100000010110000000011112/4/2023243.3常用组合逻辑电路部件(2)优先编码器(PriorityEncoder)当几个输入信号同时出现时,只对其中优先权最高的一个进行编码。优先级别的高低由设计者根据输入信号的轻重缓急情况而定。2/4/2023253.3常用组合逻辑电路部件8线—3线优先编码器74LS148(自学内容),从网上检索资料。2/4/2023263.3常用组合逻辑电路部件高电平有效GSEO工作状态00不工作,使能端EI无效01工作,但无输入10工作,且有输入11不可能出现EI:输入使能端,=1时编码器工作EO:输出使能端,与EI进行级联GS:编码状态标志,=1时处于编码状态2/4/2023273.3常用组合逻辑电路部件例:用2片CD4532组成一个16-4优先编码.P141.EI1EO1GS1EI0EO1GS0工作状态000000不工作,使能端无效110110工作,但无输入101000工作,且有输入(高8位)111111不可能出现低8位呢2/4/2023283.3常用组合逻辑电路部件上例仿真:2/4/2023293.3常用组合逻辑电路部件2.译码器(重点内容)inputcodewordoutputcodewordenableinputsmapDecoder译码:编码的逆过程,将编码时赋予代码的特定含义“翻译”出来。译码器:实现译码功能的电路。

输入为

n位二进制代码,输出为2n个状态,则称之为二进制译码器。2/4/2023303.3常用组合逻辑电路部件(1)二进制译码器——3-8译码器

11111111111111111111111111111110111111011111101111110111111011111101111110111111011111110XXXXXX1XXXXXX1XXX100000100001100010100011100100100101100110100111Y7Y6Y5Y4Y3Y2Y1Y0EE1E2A2A1A0

OutputsInputs2/4/2023313.3常用组合逻辑电路部件E为控制端(又称使能端),E=1译码工作;E=0禁止译码,输出全1。2-4译码器74LS139(自学内容),从网上检索资料。2/4/2023323.3常用组合逻辑电路部件74LS138仿真:2/4/2023333.3常用组合逻辑电路部件

应用举例(a)功能扩展(利用使能端实现)2/4/2023343.3常用组合逻辑电路部件(b)实现组合逻辑函数F(A,B,C)例:试用74LS138译码器实现逻辑函数:解:因为2/4/2023353.3常用组合逻辑电路部件例:试画出用3线-8线译码器74LS138和门电路产生如下多输出逻辑函数的逻辑图。2/4/2023363.3常用组合逻辑电路部件例:译码器真值表如图,用两片138实现。2/4/2023373.3常用组合逻辑电路部件(2)二-十进制译码器二-十进制译码器的逻辑功能是将输入的BCD码译成十个输出信号。2/4/2023383.3常用组合逻辑电路部件译中为0拒绝伪码2/4/2023393.3常用组合逻辑电路部件例:如下图2/4/2023403.3常用组合逻辑电路部件例:写出图中Z1、Z2、Z3的逻辑函数式,并化简为最简的与-或表达式。2/4/2023413.3常用组合逻辑电路部件(3)显示译码器

数字显示器件:用来显示数字、文字或者符号的器件。我们主要讨论发光二极管数码管。

LED数码管:LED数码管是由多个LED按分段式封装制成的。LED数码管有两种形式:共阴型和共阳型。公共阴极公共阳极高电平驱动低电平驱动七段显示LED数码管外形图2/4/2023423.3常用组合逻辑电路部件七段显示译码器7448的功能表2/4/2023433.3常用组合逻辑电路部件例:用七段显示译码器74LS48驱动共阴型LED数码管。74LS48驱动七段LED数码管仿真实现作为课后练习2/4/2023443.3常用组合逻辑电路部件3.数据选择器(多路开关)(重点内容)D0D1DnYSELEN...1D01D11Dn1YSELEN...2D02D12Dn2Y...3D03D13Dn3Y...能够按照给定的地址将某个数据从一组数据中选出来的电路。2/4/2023453.3常用组合逻辑电路部件74x153——双4选1数选器AB1G1C01Y1C11C22Y1C32G2C02C12C22C374X153751421643151091112131C02C01C12C11C22C21C32C31C001C101C201C3002C002C102C202C30000000001001000110100010101100111100010011010101111XX1Y2Y1G2GBAOutputsInputs2/4/2023463.3常用组合逻辑电路部件74x151——8选1数选器E’S2S1S0I0I1I2I3I4I5I6I7YY’1010000I0I0I0‘0001I1I1I1‘0010I2I2I2‘0011I3I3I3‘0100I4I4I4‘0101I5I5I5‘0110I6I6I6‘0111I7I7I7‘2/4/2023473.3常用组合逻辑电路部件 例:试用一个双4选1数据选择器74LS153接成一个8选1数据选择器。2/4/2023483.3常用组合逻辑电路部件例:试用一个双4选1数据选择器74LS153实现逻辑函数:

解:令思考:试用一个74LS153接成一个8选1数据选择器实现L=ABC+ABC+AB

和L=A⊕B⊕

C2/4/202349练习:[例]分析图示电路,写出输出Z的逻辑函数式。74151为8选1数据选择器,Y是同相输出,W是反相输出。1110111110110010110100DCBA12/4/2023503.3常用组合逻辑电路部件4.加法器(重点内容)(1)1位加法器S=A⊕B=A·B+A·BCO=A·B0010100100011011ABInputsSCOOutputs半加器2/4/2023513.3常用组合逻辑电路部件全加器——74LS283双全加器全加器能把本位两个加数An

、Bn

和来自低位的进位Cn-1三者相加,得到求和结果Sn

和该位的进位信号Cn

。Sn

Cn0000000110010100110110010101011100111111An

Bn

Cn-12/4/202352管脚图SN74LS28311A1B1Cn-11Cn1SnGND234567NC2Cn-12Cn2Sn2A2BUcc141312111098NC输入输入输出甩空甩空输入输出输出全加器74LS283—双全加器:3.3常用组合逻辑电路部件2/4/2023533.3常用组合逻辑电路部件(2)多位加法器串行进位加法器思考:用两片74LS283是否可以实现上述两个四位二进制数相加?2/4/2023544位二进制全加器3.3常用组合逻辑电路部件用加法器设计组合逻辑电路8421BCD码0011余3码

例:将8421BCD码转换成余3码。余3码=8421BCD码+3(即0011)2/4/2023553.3常用组合逻辑电路部件用加法器设计组合实现减法器

在实际应用中,通常是将减法运算变为加法运算来处理,即采用加补码的方法完成减法运算。若n位二进制的原码为N原,则与它相对应的2的补码为

N补=2N

N原

补码与反码的关系式

N补=N反+1 设两个数A、B相减,利用以上两式可得A

B=A+B补2n=A+B反+12n2/4/2023563.3常用组合逻辑电路部件用加法器设计组合实现减法器1)AB

0的情况(5-1=4)A=0101,B=0001

10100

结果表明,在A–B

0时,如加补进位信号为1,所得的结果就是其原码(即不需对结果进行求补)。10001000110111011001

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 2026中国航天科技集团临近空间无人机总体部英才招聘备考题库及答案详解参考

- 钢结构安装技术交底方案

- 2026渤海银行校园招聘备考题库附答案详解(模拟题)

- 2026四川大学华西医院医生助理招聘备考题库及答案详解(新)

- 2026广东肇庆市高要区教育局招聘高水平教师10人备考题库及完整答案详解1套

- 2026山东枣庄市山亭区校园招聘中学教师10人备考题库(曲阜师范大学站)含答案详解(综合卷)

- 2026广东华南师范大学招聘44人备考题库(编制)及答案详解(夺冠)

- 2026江苏南京中医药大学招聘体育教师备考题库(人事代理)附答案详解(综合卷)

- 2026海南三亚市天涯区教育系统赴高校面向应届毕业生招聘教师60人备考题库(第1号)及参考答案详解1套

- 2026年安徽电子信息职业技术学院公开招聘博士人才5名备考题库附答案详解(黄金题型)

- 财务知识培训课件

- 2026年教师资格证(历史学科知识与教学能力-高级中学)考试题及答案

- 2026年浙江单招酒店管理专业面试经典题含答案含应急处理题

- SJG 171-2024建筑工程消耗量标准

- 浙江省金丽衢十二校2026届高三上学期一模试题 英语 含解析

- 创新创业创效比赛项目介绍

- 新疆维吾尔自治区小学五年级下学期数学第二单元测试卷-因数和倍数单元检测

- 专升本康复治疗2025年物理治疗学测试试卷(含答案)

- XX市城投公司管理人员末等调整和不胜任退出管理制度

- 2025秋季贵州磷化(集团)有限责任公司校园招聘389人笔试历年常考点试题专练附带答案详解试卷3套

- 2025年中国LNG行业当前现状及未来趋势发展预测报告

评论

0/150

提交评论