版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

EDA技术实用教程第9章

VHDL结构与要素

9.1实体

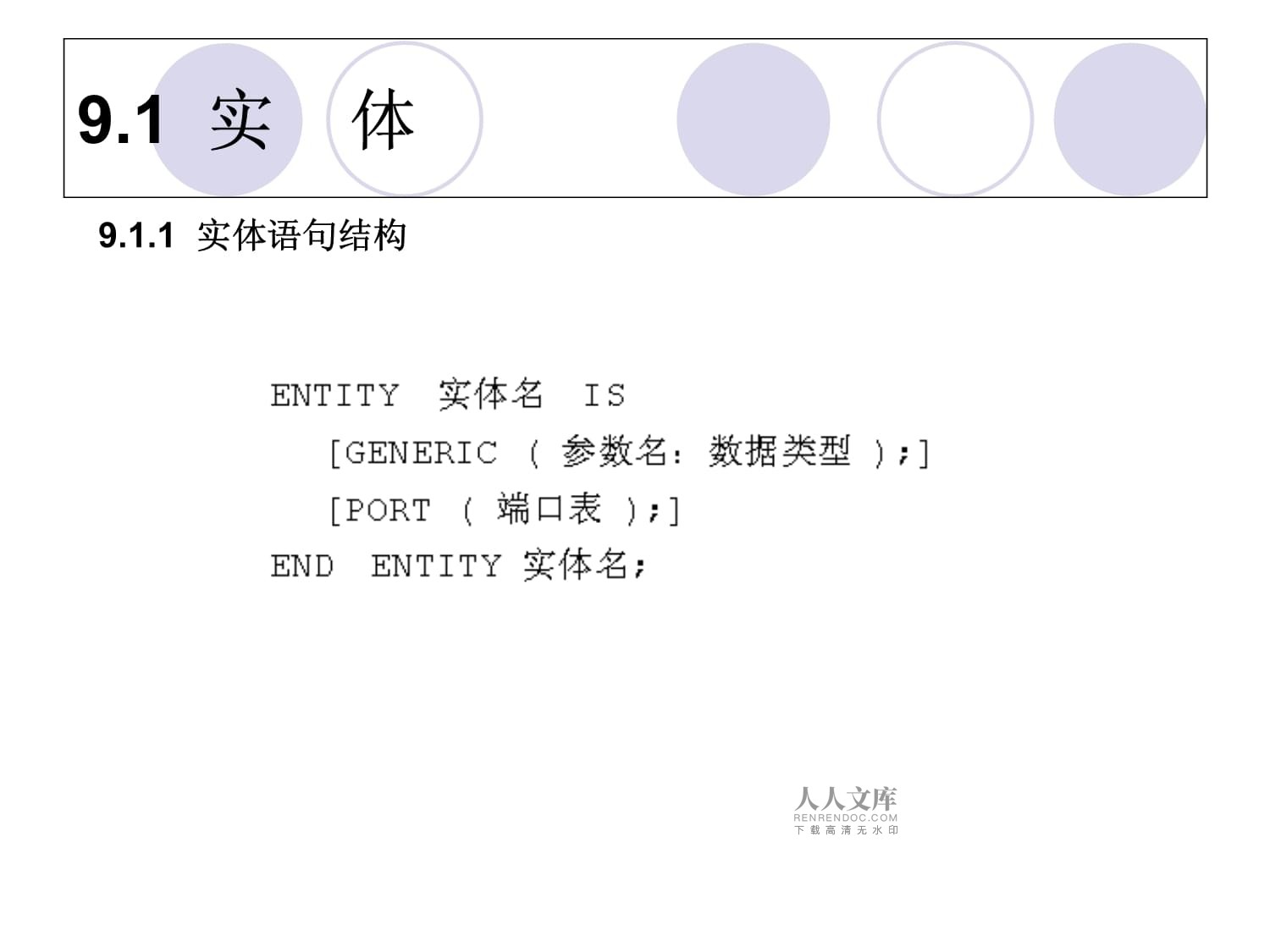

9.1.1实体语句结构

9.1实体

9.1.2参数传递说明语句

GENERIC语句是一种常数参数的端口界面,为所说明的环境提供了一种静态信息通道。

类属与常数不同:常数只能从设计实体的内部得到赋值,且不能再改变;而类属的值可以由设计实体外部提供。因此设计者可以从外面通过类属参量的重新设定而容易地改变一个设计实体或一个元件的内部电路结构和规模。

被传递的参数(又称类属参量)可以由设计实体外部提供,并可以重新设定。

GENERIC([常数名:数据类型[:设定值]{;常数名:数据类型[:设定值]});9.1实体

9.1.2参数传递说明语句9.1实体

9.1.2参数传递说明语句

9.1实体

9.1.3参数传递映射语句

GENERICMAP(类属表)

参数传递映射语句与端口映射语句PORTMAP()具有相似的功能和使用方法,它描述了相应元件类属参数间的连接和传送方式。它可用于设计从外部端口改变元件内部参数或结构规模的元件,又称类属元件。

9.1实体

9.1.3参数传递映射语句

9.1实体

9.1.3参数传递映射语句

9.1实体

9.1.3参数传递映射语句

9.1实体

9.1.4端口说明语句9.2结构体

对数据类型、常数、信号、子程序和元件等元素的说明部分

描述实体逻辑行为的、以各种不同的描述风格表达的功能描述语句

以元件例化语句为特征的外部元件(设计实体)端口间的连接。

结构体9.2结构体1.结构体的一般语言格式

2.结构体说明语句9.2结构体3.功能描述语句结构●进程语句●信号赋值语句●子程序调用语句●元件例化语句9.3VHDL子程序

子程序(SUBPROGRAM)是一个VHDL程序模块,它只能使用顺序语句。子程序不能像进程那样可以从本结构体的并行语句或进程结构中直接读取信号或象信号赋值。子程序的使用方式只能通过子程序调用及与子程序的界面端口进行通信。子程序可以在程序包、结构体和进程中定义,只有在程序包中定义过的子程序才可以被其他不同的设计调用。子程序分为两大类:过程(PROCEDURE)和函数(FUNCTION)。9.3子程序

9.3.1函数

函数参数的对象类型只能包括常量和信号,默认为常量。参数的端口模式只能是in,因此参数端口模式可以省略。函数的返回值只能有一个。9.3子程序

9.3.1函数

接下页9.3子程序

9.3.1函数

接上页9.3子程序

9.3.1函数

9.3子程序

9.3.1函数

9.3子程序

9.3.2重载函数VHDL允许同样名称的函数可以用不同的数据类型作为它的参数定义多次,以此定义的函数称为重载函数。接下页9.3子程序

9.3.2重载函数接上页接下页9.3子程序

9.3.2重载函数接上页9.3子程序

9.3.2重载函数接下页9.3子程序

9.3.2重载函数接上页9.3子程序

9.3.3转换函数

9.3子程序

9.3.3转换函数

9.3子程序

9.3.3转换函数

9.3子程序

9.3.3转换函数

接下页9.3子程序

9.3.3转换函数

接上页9.3子程序

9.3.4决断函数决断函数不可综合,主要用于VHDL仿真中解决信号被多个驱动源驱动时,驱动信号间的竞争问题。当多个驱动源都同时产生一个处理事项,只有其中一个驱动源的信号值能赋给被驱动的信号。决断函数输入一般是单一变量,多个驱动源的信号值组成非限定数组,多个信号驱动源,其信号值组成的未限定数组可依次类推。决断函数调用后返回的是单一信号值,称决断信号值。9.3子程序

9.3.5过程9.3子程序

9.3.5过程信号流向方向若未指定则默认为IN。只定义了IN模式而未定义目标参量的数据类型,则默认为常量CONSTANT;只定义了OUT或INOUT模式而未定义目标参量的数据类型,则默认为变量。9.3子程序

9.3.5过程9.3子程序

9.3.5过程9.3子程序

9.3.5过程9.3子程序

9.3.6重载过程

函数和过程的区别函数和过程的不同在于:函数只有一个输出,只能通过函数体内的RETURN语句来实现,函数体内不能有信号赋值语句;而过程却可以有不止一个输出,而且是通过过程体内的信号赋值语句或者变量赋值语句来实现的,过程体内的RETURN语句没有用处,因此不少过程都将其省略了。函数的调用只能通过表达式来实现,过程的调用则是通过过程调用语句来实现的。9.4VHDL库9.4.1库的种类1.IEEE库

std_logic_1164Numeric_BitNumeric_StdMath_RealMath_Complex2.STD库3.WORK库

4.VITAL库9.4VHDL库9.4.2库的用法

9.5程序包

(其他设计实体共享)常数说明

VHDL数据类型说明元件定义子程序定义程序包的一般语句结构如下:

PACKAGE程序包名IS--程序包首

程序包首说明部分

END程序包名;PACKAGEBODY程序包名IS--程序包体

程序包体说明部分以及包体内

END程序包名;9.5VHDL程序包

9.5VHDL程序包

9.5VHDL程序包

(1)STD_LOGIC_1164程序包。(2)STD_LOGIC_ARITH程序包。(3)STD_LOGIC_UNSIGNED和STD_LOGIC_SIGNED程序包。(4)STANDARD和TEXTIO程序包。9.6配置9.7VHDL文字规则9.7.1数字整数:

实数

:

9.7VHDL文字规则9.7.2字符串

“B”、“O”、“X”9.7VHDL文字规则9.7.3标识符及其表述规则9.7VHDL文字规则9.7.4下标名9.8数据类型●标量型(ScalarType):包括实数类型、整数类型、枚举类型、时间类型。●复合类型(CompositeType):可以由小的数据类型复合而成,如可由标量型复合而成。复合类型主要有数组型(Array)和记录型(Record)。●存取类型(AccessType):为给定的数据类型的数据对象提供存取方式。●文件类型(FilesType):用于提供多值存取类型。9.8数据类型9.8.1VHDL预定义数据类型

1.布尔类型2.位数据类型3.位矢量类型9.8数据类型9.8.1VHDL预定义数据类型

4.字符类型

5.整数类型

6.实数类型-2147483647~+21474836479.8数据类型9.8.1VHDL预定义数据类型

7.字符串类型8.时间类型9.8数据类型9.8.1VHDL预定义数据类型

9.文件类型

9.8数据类型9.8.2IEEE预定义标准逻辑位与矢量1.标准逻辑位数据类型2.标准逻辑矢量数据类型

9.8数据类型9.8.3其他预定义标准数据类型

1.无符号数据类型9.8数据类型9.8.3其他预定义标准数据类型

2.有符号数据类型

9.8数据类型9.8.4数据类型转换示例9.8数据类型9.8.4数据类型转换示例9.8数据类型9.8.4数据类型转换示例9.8数据类型9.8.4数据类型转换示例9.8数据类型9.8.4数据类型转换示例9.8数据类型9.8.4数据类型转换示例9.9VHDL操作符

9.9.1逻辑操作符

逻辑操作符(LogicalOperator)关系操作符(RelationalOperator)算术操作符(ArithmeticOperator)符号操作符(SignOperator)重载操作符(OverloadingOperator)。9.9VHDL操作符

9.9.1逻辑操作符

9.9VHDL操作符

9.9.1逻辑操作符

9.9VHDL操作符

9.9.1逻辑操作符

9.9VHDL操作符

9.9.1逻辑操作符

9.9VHDL操作符

9.9.2关系操作符“=”(等于)、“/=”(不等于)、“>”(大于)、“<”(小于)、“>=”(大于等于)和“<=”(小于等于)9.9VHDL操作符

9.9.2关系操作符9.9VHDL操作符

9.9.2关系操作符9.9VHDL操作符

9.9.3算术操作符

9.9VHDL操作符

9.9.3算术操作符

1.求和操作符9.9VHDL操作符

9.9.3算术操作符

1.求和操作符9.9VHDL操作符

9.9.3算术操作符

2.求积操作符

*(乘)、/(除)、MOD(取模)、RED(取余)3.符号操作符“+”和“-”

4.混合操作符

“**”“ABS”9.9VHDL操作符

9.9.3算术操作符

5.移位操作符SLL、SRL、SLA、SRA、ROL、ROR习题9-1说明实体、设计实体的概念。9-2举例说明GENERIC说明语句和GENERIC映射语句有何用处。9-3说明端口模式INOUT和BUFFER有何异同点。9-4什么是重载?重载函数有何用处?9-5在STRING、TIME、REAL、BIT数据类型中,VHDL综合器支持哪些类型?9-6详细说明例9-29中的语句作用和程序实现的功能。9-7表达式C<=A+B中,A、B和C的数据类型都是STD_LOGIC_VECTOR,是否能直接进行加法运算?说明原因和解决方法。9-8VHDL中有哪三种数据对象?详细说明它们的功能特点以及使用方法,举例说明数据对象与数据类型的关系。9-9能把任意一种进制的值向一整数类型的数据对象赋值吗?如果能,怎样做?习题9-10判断下列VHDL标识符是否合法,如果有误则指出原因:16#0FA#,10#12F#,8#789#,8#356#,2#0101010#74HC245,\74HC574\,CLR/RESET,\IN4/SCLK\,D100%9-11数据类型BIT、INTEGER和BOOLEAN分别定义在哪个库中?哪些库和程序包总是可见的?9-12函数与过程的设计与功能有什么区别?调用上有什么区别?9-13回答有关BIT和BOOLEAN数据类型的问题:(1)解释BIT和BOOLEAN类型的区别。(2)对于逻辑操作应使用哪种类型?(3)关系操作的结果为哪种类型?(4)IF语句测试的表达式是哪种类型?习题9-14运算符重载函数通常要调用转换函数,以便能够利用已有的数据类型。下面给出一个新的数据类型AGE,并且下面的转换函数已经实现:functionCONV_INTEGER(ARG:AGE)returnINTEGER;仿照本章中的示例,利用此函数编写一个“+”运算符重载函数,支持下面的运算:SIGNALa,c:AGE;...c<=a+20;9-15用两种方法设计8位比较器,比较器的输入是两个待比较的8位数A=[A7..A0]和B=[B7..B0],输出是D、E、F。当A=B时D=1;当A>B时E=1;当A<B时F=1。第一种设计方案是常规的比较器设计方法,即直接利用关系操作符进行编程设计;第二种设计方案是利用减法器来完成,通过减法运算后的符号和结果来判别两个被比较值的大小。对两种设计方案的资源耗用情况进行比较,并给以解释。9-16利用循环语句和移位操作符实现移位相加方式的纯组合电路8位乘法器设计。实验与设计

9-1乐曲硬件演奏电路设计(1)实验目的:(2)实验原理:

实验与设计

9-1乐曲硬件演奏电路设计(1)实验目的:(2)实验原理:

实验与设计

9-1乐曲硬件演奏电路设计(3)实验内容1:(4)实验内容2:(5)实验内容3:(6)实验内容4:(7)实验内容5:(8)实验内容6:(9)实验内容7:(10)实验报告:5E+系统的演示文件:/KX_7C5EE+/EXPERIMENTs/EXP4_Music/。

实验与设计

9-1乐曲硬件演奏电路设计(3)实验内容1:(4)实验内容2:(5)实验内容3:(6)实验内容4:(7)实验内容5:(8)实验内容6:(9)实验内容7:(10)实验报告:5E+系统的演示文件:/KX_7C5EE+/EXPERIMENTs/EXP4_Music/。

实验与设计

9-1乐曲硬件演奏电路设计(3)实验内容1:(4)实验内容2:(5)实验内容3:(6)实验内容4:(7)实验内容5:(8)实验内容6:(9)实验内容7:(10)实验报告:5E+系统的演示文件:/KX_7C5EE+/EXPERIMENTs/EXP4_Music/。

实验与设计

9-1乐曲硬件演奏电路设计(3)实验内容1:(4)实验内容2:(5)实验内容3:(6)实验内容4:(7)实验内容5:(8)实验内容6:(9)实验内容7:(10)实验报告:5E+系统的演示文件:/KX_7C5EE+/EXPERIMENTs/EXP4_Music/。

实验与设计

9-2数字彩色液晶显示控制电路设计(1)实验任务1:基于5E+系统的基本控制演示示例是:/KX_7C5EE+/EXPERIMENTs/EXP13_COLOR_LCD/(2)实验任务2:(3)实验任务3:(4)实验任务4:(5)实验任务5:(6)实验任务6:演示示例:/KX_7C5EE+/DEMOs/EXPL9_Super_Mario2/,和/DEMOs/EXP7_LCD_light_GAME/。实验与设计

9-3GPS应用的通信电路设计实验任务:参考GPS模块使用文件:/KX_7C5EE+/GPS文件。常用的GPS模块是UART通信方式。可以用两种方式读取GPS模块中的数据:1、软件方式。可以根据实验6-8,使用FPGA中的8051核与GPS通信,并将数据用液晶显示出来;2、硬件方式,即不使用任何CPU。可以根据实验7-6的原理设计UART硬件特性模块,读取GPS模块的数据,并显示于数码管或液晶屏上。演示示例:/KX_7C5EE+/EXPERIMENTs/EXP16_KX8051_FTEST_RS232/和/EXP17_KX8051_GPS_FTEST/。

实验与设计

9-3GPS应用的通信电路设计实验任务:演示示例:/KX_7C5EE+/EXPERIMENTs/EXP16_KX8051_FTEST_RS232/和/EXP17_KX8051_GPS_FTEST/。

9-4VGA动画图像显示控制电路设计实

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 小学语文一年级下册《语文园地三》教案

- 四年级上册音乐教案 第六单元 亲爱的回声苏少版

- 2024-2025学年校园霸凌的认知与预防教学设计

- 2022幼儿毕业典礼幼儿代表简单发言稿(9篇)

- 2022安全生产月激情演讲稿(10篇)

- 《黄昏里的男孩》读后感

- 孝亲感恩 传承爱心 教学设计-2023-2024学年中职下学期主题班会

- 高端幼儿园早教课程设计

- 服饰造型基础课程设计

- 广东省中山市七年级生物下册 4.7.1分析人类活动破坏生态环境的影响教案 (新版)新人教版

- 小儿肠炎护理查房

- 健康身体保健课件

- 小课题初高中数学结题报告

- 家庭农场认定申请书

- 山东省济宁市汶上县2023-2024学年九年级上学期第一次质检数学试卷

- 自然灾害预警信息记录表

- 公安区域合作方案

- 历年高中数学联赛真题分类汇编36不等式

- 办公家具采购方案(技术方案)

- 沟槽钢板桩支护工程施工方案

- GB/T 42554-2023计量器具环境试验的通用要求

评论

0/150

提交评论