版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

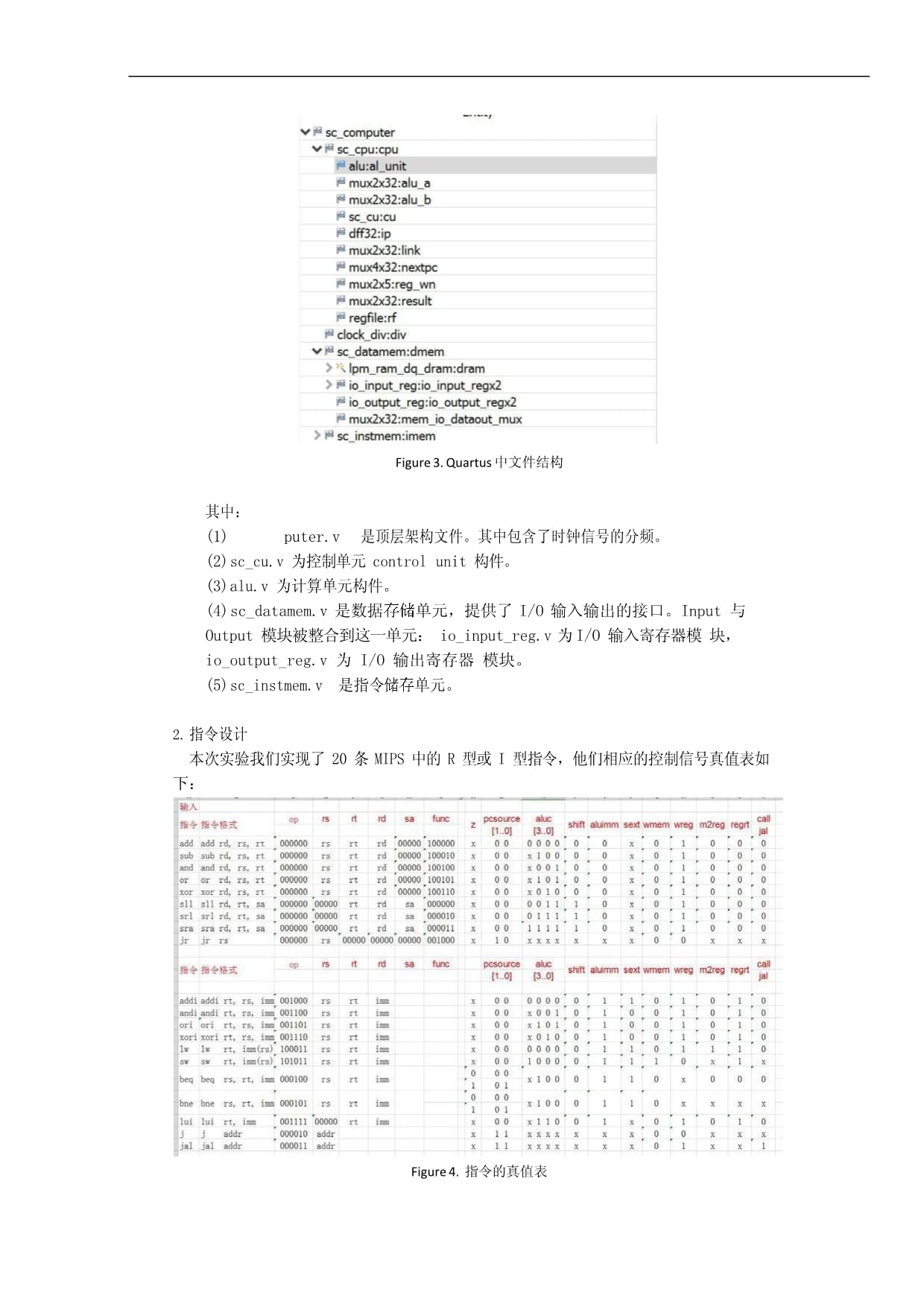

实验:基本单周期CPU设517030910304理解计算机 大组成部分的协调工作原理,理解程序自动执行的原理掌握运算器、器、控制器的设计原理。重点掌握控制器设计原理I/OI/OI/O端口与外部设备进行信息交互二、实验内容:VerilogHDLquartus20MIPSCPU利用实验提供的标准测试程序代码,完成仿真测试部分,实现CPU与外部设备的输入输出端口设计。实验中可采用高端地址。即将外部设备状态,读到CPU内部寄存器。I/OswDE2LED备的控制信号(或数据信息)CPU利用自己编写的程序代码,在自己设计的CPU上,实现对板载输入开关或按键的LED7LED4bit4bit2LED10LED10(具体任务形式不做严格规定,同学可自由创意)。Altera-DE2首先将程序和数据输入计算机的器中,然后从主存中“程序(程序执行的第一条指令的地址PU并产生具体的控制信号。指令执行完毕后修改PC值,决定下一条指令所在的Figure1.CPU五、设计思构件结(Instmen)DataMemory(简称Datamem),并分别实现他们Figure2.CPU最后,我的文件(entity)结构如下Figure3Quartus其中 是顶层架构文件。其中包含了时钟信号的分频sc_cu.vcontrolunitalu.vsc_datamem.v是数据单元,提供了I/O输入输出的接口。Input与io_output_reg.v为I/O输出寄存器模块。sc_instmem.v是指令单元指令设Figure4.分频设 mem_clock。此外,imem_clock在sc_instmem.v文件中实现。dmem_clock在sc_datamem.v文件中实现。Figure5.Figure6I/0在sc_datamem.v文件中,通过对输入的lw和sw指令的地址的判断,实现对数据RAMI/O控制寄存器组的区分和分别

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- T/CCAAS 001-2024新时代班组建设专业指南

- 电子包装买卖合同4篇

- 3G系列鼠标2025年度销售代理合同2篇

- 专业车辆考试题库及答案

- 上海安全员B证考试题库及答案

- 胰腺疾病术后护理

- 家具商场出租合同6篇

- 工业设计美学分享

- T/ZJSEE 0014-2023集中压缩空气综合供应系统建设质量验收规程

- 新型疫苗:亚单位疫苗项目绩效评估报告

- 牙周检查记录表

- 外墙涂料吊篮施工方案

- 《新时代劳动教育》新时代劳动价值观

- 第四章 地陪导游服务程序与服务质量

- 山东紫薇种质资源调查报告

- 2023年医疗招聘技术类-影像医学与核医学考试历年真题集锦附答案

- “循环经济关键技术与装备”重点专项2023年度项目申报指南

- 旅行社应急处置方案

- 中移L2认证(集团)备考题库(浓缩版)

- 混凝土交接单

- 单作用叶片泵的工作原理

评论

0/150

提交评论