版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

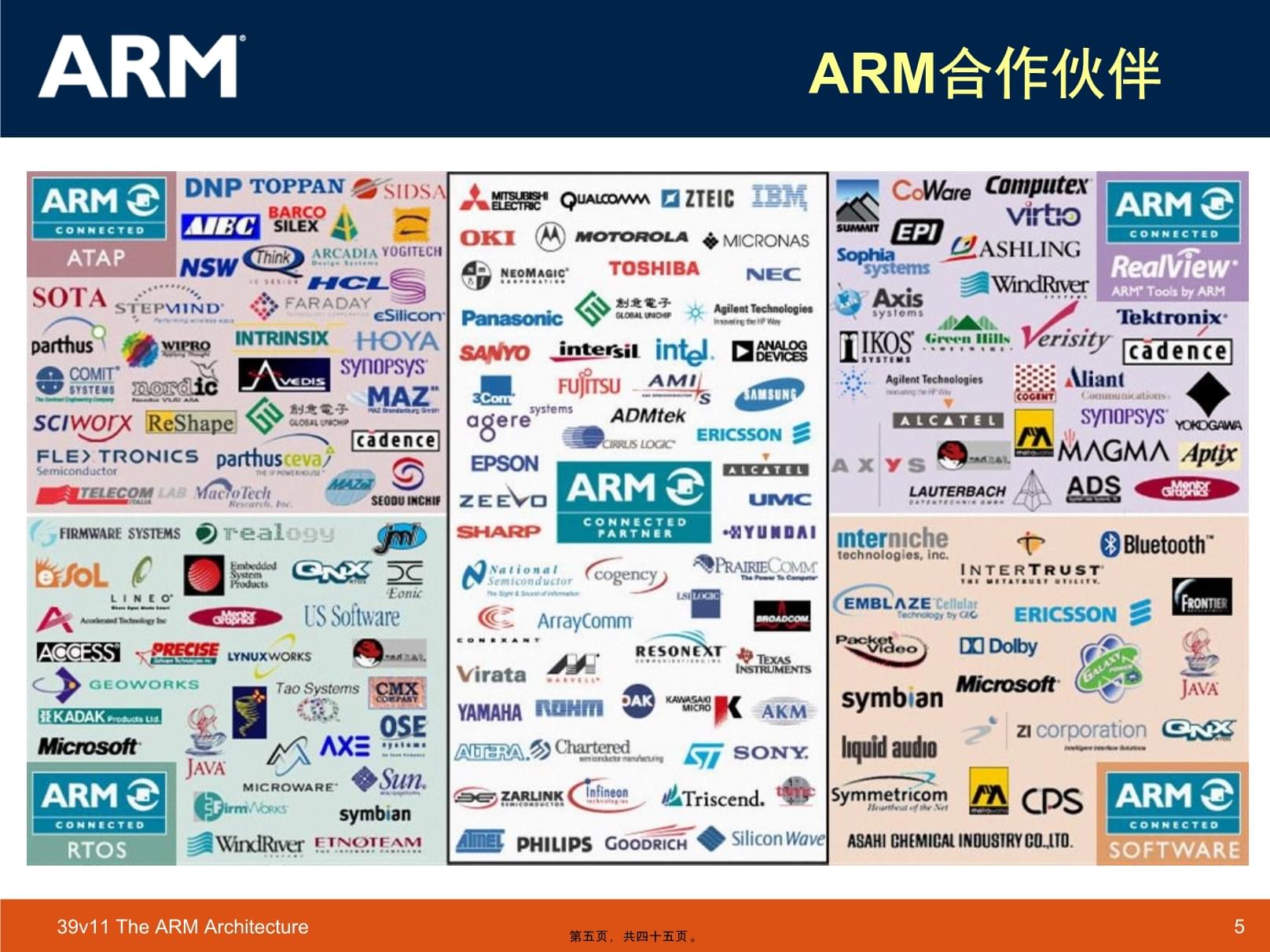

ARM体系结构第一页,共四十五页。ARMLtdARM-AdvancedRICSMachinesARM即可以认为是公司的名字,也可以认为是对一类微处理器的通称,也可以认为是一种技术的名字,还可以认为它是一种商业思想,1991年ARM公司成立于英国剑桥,主要出售芯片设计技术的授权第二页,共四十五页。ARM公司简介ARM公司作为32位处理器内核的提供者,拥有100多家办导体合作伙伴,拥有100多家半导体合作伙伴,ARMcore是目前消费类电子市场中占有量第一的CPU体系ARM是一个CPU内核。ARM公司自己并不生产或销售芯片,它采用技术授权模式,通过出售芯片技术授权,收取授权费与技术转让费随着ARM、MIPS、ARC等成熟内核的推出,很多过去没有32位CPU研发能力的半导体公司进入这一行列。第三页,共四十五页。ARM全球分布EnglandCambridge,Maidenhead,Sheffield,BlackburnGermanyMunich FranceParis,SophiaAntipolisKoreaSeoulUSSeattle,LosGatos,WalnutCreek,Austin,Boston,SanDiegoAsiaTaiwanJapanShin-Yokohama(Tokyo)第四页,共四十五页。ARM合作伙伴第五页,共四十五页。ARMLtd世界各大半导体商场商从ARM公司购买其设计的ARM微处理器核,根据各自不同的应用领域,加入适当的外围电路,从而形成自己的ARM微处理器芯片进入市场。基于ARM技术的微处理器应用约占据了32位RICS微处理器80%以上的市场份额,ARM技术正在逐步渗入到我们生活的各个方面。第六页,共四十五页。将技术授权给其它芯片厂商形成各具特色的ARM芯片...第七页,共四十五页。ARM微处理器的特点低功耗、低成本、高性能采用RICS指令集使用大量的寄存器ARM/THUMB指令支持三/五级流水线第八页,共四十五页。ARM微处理器的特点采用RICS体系结构

固定长度的指令格式、指令简单、基本寻找方式有2-3种使用单周期指令,便于流水线操作执行大量使用寄存器,数据处理指令只对寄存器进行操作,只有加载/存储指令可以访问存储器,以提高指令的执行效率大量使用寄存器31个通用寄存器,包括程序计数器(PC指针)均为32位寄存器6个状态寄存器,用以表示CPU的工作状态及程序运行状态,均为32位高效的指令系统ARM处理器支持两种指令集:ARM指令集和THUMB指令集ARM指令为32位的长度、THUMB指令为16位长度。THUMB指令集为ARM指令集的功能子集,但与等价的ARM代码相比较,可节省30%-40%以上的存储空间,同时具备32位代码的所有优点。第九页,共四十五页。ARM微处理器的特点ARM体系结构还采用一些特别的技术,在保证高性能的前提下尽量缩小芯片的面积,并降低功耗所有的ARM指令都可以根据前面的执行结果决定是否被执行,从而提高指令的执行效率可用加载/存储指令批量传输数据,以提高数据的传输效率。可在一条数据处理指令中同时完成逻辑处理和移位功能。在循环处理中使用地址的自动增减来提高运行效率第十页,共四十五页。ARMcore的增强结构Thumb指令集主要是在代码长度和窄带宽存储器性能两方面:因为当在一个16位存储器系统里面取1条32位指令的时候,需要耗费2个存储器访问周期;比之32位的系统,其速度正好大概下降一半左右。而16位指令在32位存储器系统或16位存储器系统里的表现基本相同。正是存储器造成的系统瓶颈导致了这个的差别,除了在窄带宽系统里面的性能优势外。Thumb指令的另外一个好处的代码尺寸。同样一段C代码,用Thumb指令编译的结果,其长度大约只占ARM编译结果的65%左右,可以明显地节省空间。在大多数情况下,紧凑的代码和窄带宽的存储器系统,还会带来功耗上的优势。Thumb指令集在功能上只是ARM指令集的一个子集,某些功能只能在ARM状态下执行,如CPSR和协处理器的访问。进行异常响应时,处理器会自动进入ARM状态。从系统优化考虑,在宽带存储器上不应该放置Thumb代码,很多窄带系统具有宽带的内部存储器即使是一个单纯的Thumb应用系统,也必须加一个汇编的交互头程序,因为系统总是自动从ARM开始启动所以,不可避免会产生ARM与Thumb之间的交互问题。第十一页,共四十五页。ARMcore的增强结构指令流水线注意:执行ADD指令时PC已经指向CMP指令所在位置(即+8的位置)ADDSUBADDCMPSUBADD

取指译码执行时间周期1周期2周期3ARM7系列使用3级流水线ARM95级,ARM106级,ARM117级第十二页,共四十五页。为增加处理器指令流的速度,ARM7系列使用3级流水线.允许多个操作同时处理,比逐条指令执行要快。PC指向正被取指的指令,而非正在执行的指令FetchDecodeExecute从存储器中读取指令解码指令寄存器读(从寄存器Bank)移位及ALU操作寄存器写(到寄存器Bank)PC PCPC-4 PC-2PC-8 PC-4ARM ThumbARMcore的增强结构第十三页,共四十五页。最佳流水线该例中用6个时钟周期执行了6条指令所有的操作都在寄存器中(单周期执行)指令周期数(CPI)=1

操作周期 1 2 3 4 56ADDSUBMOVANDORREORCMPRSBFetchDecodeExecuteFetchDecodeExecuteFetchDecodeExecuteFetchDecodeExecuteFetchDecodeExecuteDecodeExecuteFetchDecodeFetchFetch第十四页,共四十五页。LDR流水线举例该例中,用6周期执行了4条指令指令周期数(CPI)=1.5周期

操作 1 2 3 4 5 6ADDSUBLDRMOVANDORRFetchDecodeExecuteFetchDecodeExecuteFetchDecodeExecuteDataWritebackFetchDecodeExecuteFetchDecodeFetch第十五页,共四十五页。分支流水线举例流水线被阻断注意:内核运行在ARM状态ARM7的指令周期数(CPI)=1.9周期

12345

0x8000BL0x8FEC0x8004X0x8008XX0x8FECADD0x8FF0SUB0x8FF4MOV地址

操作FetchDecodeExecuteFetchDecodeExecuteFetchDecodeFetchFetchDecodeExecuteLinkretAdjustFetchDecodeFetch第十六页,共四十五页。ARMcore的增强结构JAVA加速器SIMD指令集单指令流多数据流(SingleInstructionMultipleData,SIMD)能力使得软件更有效地完成高性能的媒体应用象声音和图像编码器。ARMv6指令集合中加入了超过60个SIMD指令。加入SIMA指令将使性能提高2倍到4倍。SIMD能力可以完成高端的图像编码、语音识别、3D图像DSP功能扩展(早期控制,不带乘法和乘加运算)

几条新的完成16位数据乘法和乘加操作指令实现饱和的有符号数的加减法操作的指令Cache预取指令PLDTRUSTZone技术第十七页,共四十五页。数据和指令类型ARM采用的是32位架构(总线结构).4/8/16/32,主流8/32;8位:控制简单的低端产品,32位(手机、数码相机、PDA、通信设备、医疗设备等这些高端产品)ARM约定:Byte: 8bits(最小单位为字节)Halfword:16bits(2byte)(半字必须与2个字节的边界对准)Word: 32bits(4byte)(字必须与4个字节的边界对准)大部分ARMcore提供:ARM指令集(32-bit)(执行ARM指令集的状态称之为ARM状态)Thumb指令集(16-bit)(执行Thumb指令集的状态称之为Thumb状态)第十八页,共四十五页。ARM微处理器:存储器格式大端的数据存放格式低地址高地址地址A地址A+1地址A+2地址A+3最高有效字节的地址就是该word的地址最高有效字节位于最低地址worda=0xf6

73

4b

cdf6734bcd第十九页,共四十五页。ARM微处理器:存储器格式小端的数据格式

低地址高地址地址A地址A+1地址A+2地址A+3最低有效字节的地址就是该word的地址最低有效字节位于最低地址worda=0xf6

73

4b

cdf6734bcdLPC2000小端通常是ARM处理器的缺省格式。第二十页,共四十五页。ARM微处理器:处理器工作状态(PROCESSOROPERATINGSTATES)处理器有两种工作状态:ARM:32位,执行字对准的ARM指令Thumb:16位,执行半字对准的Thumb指令ARM和Thumb之间状态的切换不影响处理器的模式或寄存器的内容,状态切换开销几乎为0.;从Arm状态切换到Thumb状态LDRR0,=Lable+1BXR0;从Thumb状态切换到ARM状态LDRR0,=LableBXR0LableADDR0,R1,R2地址最低位为1,表示切换到Thumb状态地址最低位为0,表示切换到ARM状态跳转地址标号(偶数)第二十一页,共四十五页。ARM微处理器:处理器工作状态进入Thumb状态:执行BX指令,并设置操作数寄存器的状态(位[0])为1。在Thumb状态进入异常(IRQ,FIQ,UNDEF,ABORT,SWIetc.),当异常处理返回时自动转换到Thumb状态进入ARM状态:执行BX指令,并设置操作数寄存器的状态(位[0])为0。进入异常时,将PC放入异常模式链接寄存器中,从异常向量地址开始执行也可进入ARM状态BXRm第二十二页,共四十五页。ARM状态和Thumb状态的切换;从ARM状态转变为Thumb状态CODE32LDRR0,=Label+1BXR0;从ThumbARM状态转变为ARM状态CODE16LDRR0,=LabelBXR0第二十三页,共四十五页。例子CODE32adr r0,Tstart+1

bx r0 nopCODE16Tstart mov r0,#10 mov r1,#3 bl doadd

stop b stopdoadd add r0,r0,r1

bx

lr

end 第二十四页,共四十五页。ARM微处理器:处理器工作状态(PROCESSOROPERATINGSTATES)Thumb代码所需的存储空间约为ARM代码的60%-70%。Thumb代码使用的指令数比ARM的代码多30%-40%。若使用32位的存储器,ARM代码比Thumb代码快约40%若使用16位的存储器,Thumb代码比ARM代码快约40%-50%与ARM代码相比较,使用Thumb代码,存储器的功耗会降低约30%系统性能有较高要求,应用32位的存储系统与ARM指令集;对系统的成本和功耗有较高要求,则应使用16位的存储系统和Thumb指令集;两者可结合使用第二十五页,共四十五页。ARM体系结构版本ARM体系结构从最初开发到现在有了巨大的改进,并仍在完善和发展。为了清楚的表达每个ARM应用实例所使用的指令集,ARM公司定义了6种主要的ARM指令集体系结构版本,以版本号V1~V8表示。第二十六页,共四十五页。ARMV4ARMV4是目前支持的最老的架构,是基于32-bit地址空间的32-bit指令集。ARMv4除了支持ARMv3的指令外还扩展了:支持halfword的存取支持byte和halfword的符号扩展读支持Thumb指令提供Thumb和Normal状态的转换指令进一步的明确了会引起Undefined异常的指令对以前的26bits体系结构的CPU不再兼容

第二十七页,共四十五页。ARMv4TARMv4T增加了16-bitThumb

指令集,这样使得编译器能产生紧凑代码(相对于32-bit代码,内存能节省到35%以上)并保持32-bit系统的好处。Thumb在处理器中仍然要扩展为标准的32位ARM指令来运行。用户采用16位Thumb指令集最大的好处就是可以获得更高的代码密度和降低功耗。第二十八页,共四十五页。ARMV5TE1999年推出ARMv5TE其增强了Thumb体系,增强的Thumb体系增加了一个新的指令同时改进了Thumb/ARM相互作用、编译能力和混合及匹配ARM与Thumb例程,以更好地平衡代码空间和性能并在ARMISA上扩展了增强的DSP

指令集:

增强的DSP指令包括支持饱和算术(saturatedarithmetic),并且针对AudioDSP应用提高了70%性能。‘E’扩展表示在通用的CPU上提供DSP能力。第二十九页,共四十五页。ARMv5TEJ2000年推出ARMv5TEJ,增加了Jazelle扩展以支持Java加速技术。Jazelle状态下允许直接运行java8位码.Java字节码8-bits独立架构的指令集。Jazelle用硬件执行大多数的字节码Jazelle技术比仅仅基于软件的JVM性能提高近8倍的性能减少了80%的功耗。

ARMJazelle(ARM发布的java硬件加速虚拟机优化技术,目的是为了提高java应用的启动运行及反应速度)第三十页,共四十五页。ARMv62001年推出ARMv6,它在许多方面做了改进如内存系统、异常处理和较好地支持多处理器。SIMD扩展使得广大的软件应用如Video和Audiocodec的性能提高了4倍。Thumb-2和TrustZone技术也用于ARMv6中。ARMv6第一个实现是2002年春推出的ARM1136J(F)-STM处理器,2003年又推出了

ARM1156T2(F)-S

和ARM1176JZ(F)-S处理器。第三十一页,共四十五页。ARMv7ARMv7定义了3种不同的处理器配置(processorprofiles):ProfileA是面向复杂、基于虚拟内存的OS和应用的(2G)ProfileR是针对实时系统的ProfileM是针对低成本应用的优化的微控制器的(50M)所有ARMv7profiles实现Thumb-2技术,同时还包括了NEON™技术的扩展提高DSP和多媒体处理吞吐量400%

,并提供浮点支持以满足下一代3D图形和游戏以及传统嵌入式控制应用的需要。第三十二页,共四十五页。ARMv8ARMv8-A

将64位架构支持引入ARM架构中,其中包括:

64位通用寄存器、SP(堆栈指针)和

PC(程序计数器)64

位数据处理和扩展的虚拟寻址两种主要执行状态:AArch64

-64位执行状态AArch32

-32位执行状态第三十三页,共四十五页。ARM处理器的分类结构体系版本(Architecture)ARMv4TARMv5TEARMv6ARMCortex(v7)ProcessorFamilyARM7ARM9ARM10ARM11ARMCortex按应用特征分类应用处理器

ApplicationProcessor实时控制处理器

Real-timeController微控制器

Micro-controller特征:MMU,Cache最快频率、最高性能、合理功耗特征:MPU,Cache实时响应、合理性能、较低功耗特征:nosub-memorysystem一般性能、最低成本、极低功耗第三十四页,共四十五页。ARM发展SA-110ARM7TDMI4T1Halfwordandsignedhalfword/bytesupportSystemmodeThumbinstructionset24ARM9TDMISA-1110ARM720TARM940TImprovedARM/ThumbInterworkingCLZ5TESaturatedmathsDSPmultiply-accumulateinstructionsXScaleARM1020EARM9E-SARM966E-S3EarlyARMarchitecturesARM9EJ-S5TEJARM7EJ-SARM926EJ-SJazelleJavabytecode

execution6ARM1136EJ-SARM1026EJ-SSIMDInstructionsMulti-processingV6Memoryarchitecture(VMSA)UnaligneddatasupportV7架构;cortex第三十五页,共四十五页。v4v5TESA110v4TARM720TARM7TDMI-SARM920TARM940TARM922TARM966E-SARM946E-SARM1020Ev5TEJ/Jazellev6/JazelleARM7EJ-SARM926EJ-SARM1026EJ-SARM11Micro-ArchitectureRoadmapofARMV4/V5/V6第三十六页,共四十五页。ARMFamilyARM7™FamilyARM9™FamilyARM10™FamilyARM11™Family150DMIPS300DMIPS500DMIPS1000DMIPSARMCortex™FamilyARM720TARM1136JARM1176JZARM1026EARM920T/ARM922TARM926EJCortexAApplicationProcessorARM7TDMIARM1156T2ARM1026EARM946ECortexREmbeddedRTControllerARM7TDMIARM966EARM968ECortexMMicro-controllerARMArchitecture第三十七页,共四十五页。系列相应产品性能特点ARM7系列ARM7TDMI,ARM7TDMI-S,ARM720T,ARM7EJ三级流水性能:0.9MIPS/MHz,可达到130MIPs(Dhrystone2.1)

ARM9系列ARM920T,ARM922T

五级流水,性能:1.1MIPS/MHz,可达300MIPS(Dhrystone2.1),单32-bitAMBAbus接口,支持MMUARM9E系列ARM926EJ-S,RM946E-S,ARM966E-S,ARM968E-S,ARM996HS

五级流水,支持DSP指令。性能:1.1MIPS/MHz,可达300MIPS(Dhrystone2.1),高性能AHB,软核(softIP)

ARM10系列ARM1020E,ARM1022EARM1026EJ-S

6级流水支持分支预测(branchprediction),支持DSP指令。性能:1.35MIPS/MHz,可达430+Dhrystone2.1

MIPS,,可选支持高性能浮点操作,双64位总线接口,内部64位数据通路第三十八页,共四十五页。系列相应产品性能特点ARM11系列ARM11MPCore,ARM1136J(F)-S,ARM1156T2(F)-S,ARM1176JZ(F)-S

8级流水线(9级ARM1156T2(F)-S),独立的load-store和arithmetic流水线,支持分支预测和返回栈(ReturnStack)。强大的ARMv6指令集,支持DSP,SIMD(SingleInstructionMultipleData)扩展,支持ARMTrustZone、Thumb-2核心技术。740Dhrystone2.1MIPS,低功耗0.6mW/MHz(0.13µm,1.2V)Cortex系列Cortex-A8,Cortex-M3,Cortex-R4Cortex-A系列:面向用于复杂OS和应用的应用处理器(applicationsprocessors),支持ARM,ThumbandThumb-2指令集。Cortex-R系列:面向嵌入式实时领域的嵌入式处理器,支持ARM,Thumb,和Thumb-2指令集。Cortex-M系列:面向深嵌入式价格敏感的嵌入式处理器,只支持Thumb-2指令集SecurCore系列SecurCoreSC100,SecurCoreSC200用于SmartCard和SecureIC的32-bit解决方案。支持ARM和Thumb

指令集,软核。具有安全特征和低成本安全存储保护单元

第三十九页,共四十五页。主流ARM处理器ARM7世界上最为广泛使用的CPU之一<100MHz(一般)ARM9100-300MHz1.7BARMPowredshipmentinyearof2005,31%isARM9based.第四十页,共四十五页。ARM11芯片ARM11300-700+MHzSIMD

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 预制路面维修合同范本

- 土工材料采购合同范本

- 高血压透析病人的护理

- 服装代设计合同范本

- 2025鸡肉购销合同鸡肉购销合同样本

- 铲车代理运营合同范本

- 2025年内江货运从业资格模拟考试

- 2025年南宁从业资格货运资格考试题库及答案

- 2025年银川货运从业资格证考试模拟考试题库及答案大全

- 机构合并合同范本

- 初中劳动教育课程实施方案

- 呵护地球家园点亮绿色希望-2025年4月22日第56个世界地球日主题教育班会 高中主题班会优 质课件

- 政务人员礼仪培训课件

- 2025年阿拉伯语水平测试模拟试卷:阿拉伯语数字与日期表达应用试题

- 棱柱棱锥棱台的表面积和体积课件高一下学期数学人教A版1

- 《血管活性药物静脉输注护理》团体标准解读课件

- 屋顶光伏的钢结构施工方案

- 第15课《青春之光》课件-2024-2025学年统编版语文七年级下册

- 中考语文古诗欣赏试题汇编(课内古诗比较阅读)(截至2024)

- 云梯车作业交底

- 《孙权劝学》历年中考文言文阅读试题40篇(含答案与翻译)(截至2024年)

评论

0/150

提交评论