版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

第五章:存储器层次结构-C[AdaptedfromComputerOrganizationandDesign,4thEdition,Patterson&Hennessy,©2008,MK]CourtesyforMaryJaneIrwinofPSU复习:一台计算机的主要部件

处理器控制器数据通路存储器设备输入输出高速缓存主存辅助存储器(硬盘)怎样管理存储层次结构?寄存器

存储器by编译器(程序员?)高速缓存

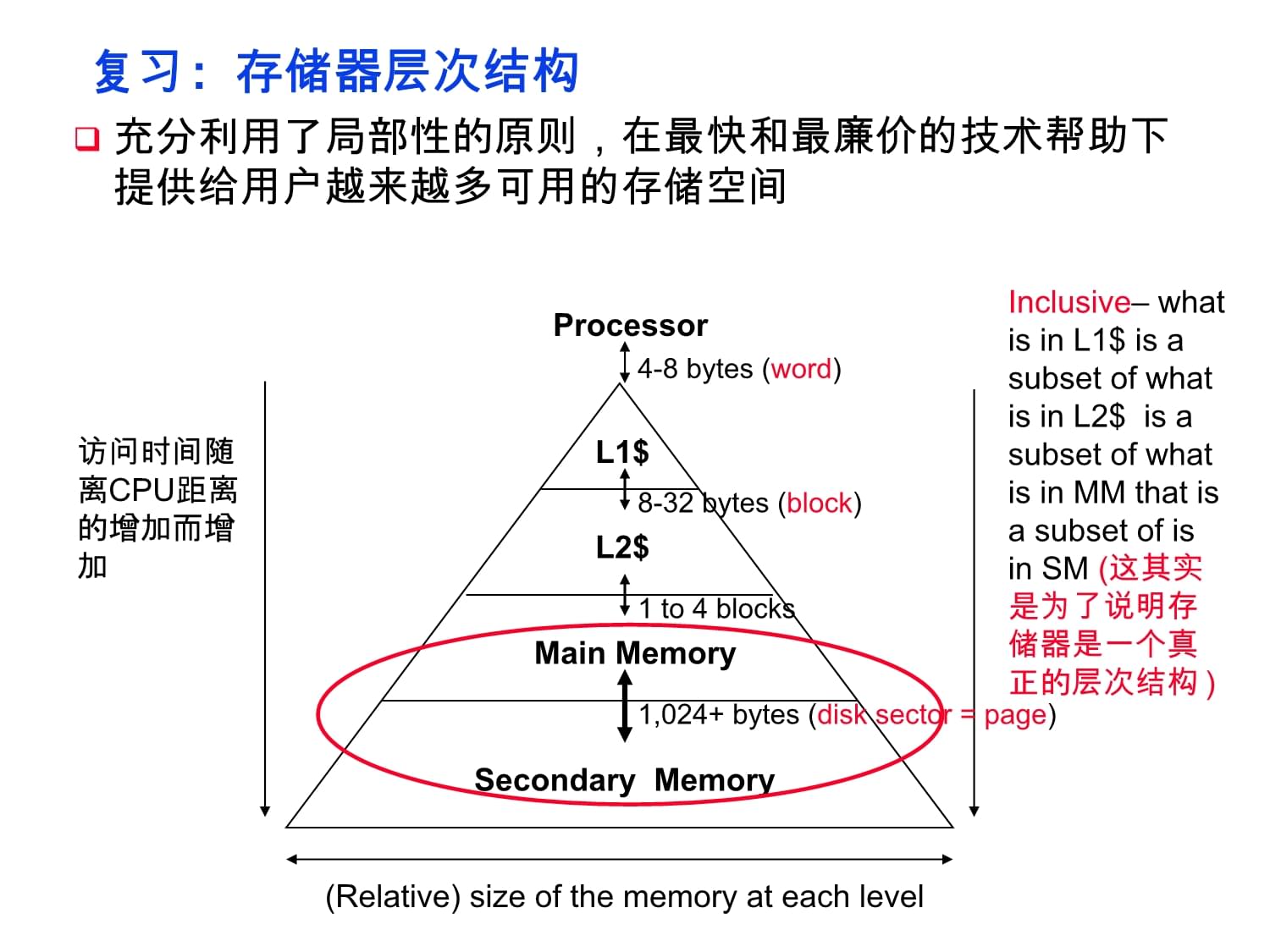

主存bycache控制器硬件主存硬盘(外存)by操作系统(虚拟存储器)通过快表(TLB)实现虚拟地址到物理地址的转换by程序员(files)复习:存储器层次结构访问时间随离CPU距离的增加而增加L1$L2$MainMemorySecondaryMemoryProcessor(Relative)sizeofthememoryateachlevelInclusive–whatisinL1$isasubsetofwhatisinL2$isasubsetofwhatisinMMthatisasubsetofisinSM(这其实是为了说明存储器是一个真正的层次结构)4-8bytes(word)1to4blocks1,024+bytes(disksector=page)8-32bytes(block)充分利用了局部性的原则,在最快和最廉价的技术帮助下提供给用户越来越多可用的存储空间虚拟存储器将主存用作辅助存储器高速缓存的技术允许在多道程序之间有效而安全地共享存储器使那些需要比物理存储器更大的存储空间的程序能够运行

提供重定位来简化执行时的程序加载过程(例如,允许将程序加载到主存中的任何位置)工作原理?–还是局部性原则在任何时间内,程序都是可能去访问整个地址空间内某一部分相对较小的地址空间每个程序都是编译到它自己的地址空间–一个“虚拟”的地址空间在程序运行时,每个虚拟地址都是必须要转化为物理地址

(主存中的地址)共享物理内存的两个程序Program1虚拟地址空间主存储器一个程序的地址空间划分为很多页

(所有的页固定为同一大小)or段(大小可变)每个页的开始地址(在主存中或辅存中)包含在程序的页表中Program2虚拟地址空间地址转换虚拟地址(VA)页内偏移虚拟页号3130...1211...0页内偏移物理页号物理地址

(PA)29...12110地址变换所以每个访存需求最开始都需要通过地址变换将虚拟空间转换为物理空间虚拟存储器中,访问缺失被称为缺页(例如,访问的页不在物理存储器中)虚拟地址到物理地址的转换是需要软硬件结合地址转换机制物理页的基地址主存储器硬盘存储器(外存)虚拟页号V11111101010页表(在主存中)页内偏移物理页号页内偏移页表寄存器VirtualAddressingwithaCache由于页表存放在主存中,因此程序多出一次额外的访存-需要一次访存以获得物理地址(通过地址变换将虚拟地址VA转换为物理地址PA),此后的访存才是获得数据CPUTrans-lationCacheMainMemoryVAPAmisshitdata这样使存储器(缓存)访问变得开销很大

(程序每次访存至少需要两次)现代处理器都包含一个特殊的cache以追踪最近使用过的地址变换,这个特殊的地址转换cache就是快表TranslationLookasideBuffer(TLB)–用于记录最近使用地址的映射信息的一个较小的高速缓存,从而可以避免每次都要访问页表加速地址转换物理页基地址主存储器硬盘存储器虚拟页号V1111110101011101标记物理页基地址V快表页表(在物理存储器中)页表寄存器TranslationLookasideBuffers(TLBs)快表正和其它的cache一样,TLB的组织形式也是全相联,组相联,直接映射这几种TLB的访问时间通常是要比cache的访问时间短(因为TLB比cache小很多)TLB通常不会超过512项ATLBintheMemoryHierarchyTLB缺失–判断是缺页还是仅仅是一次TLB缺失?

如果该页在主存中,那么TLB缺失只是一次转换缺失,处理器可以通过将页表中的变换装载到TLB并重新访问来进行缺失处理(TLB缺失既可以通过硬件处理,也可以通过软件处理)Takes10’sofcyclestofindandloadthetranslationinfointotheTLB如果该页不在主存中,TLB缺失就是一次真的缺页Takes1,000,000’sofcyclestoserviceapagefaultTLB缺失比缺页要频繁得多CPUTLBLookupCacheMainMemoryVAPAmisshitdataTrans-lationhitmiss¾t¼tTLB中可能发生的事件组合TLBPageTableCache可能发生么?如果可能,什么情况下发生?HitHitHitHitHitMissMissHitHitMissHitMissMissMissMissHitMissMiss/HitMissMissHit

Yes–whatwewant!Yes–althoughthepagetableisnotcheckediftheTLBhitsYes–TLBmiss,PAinpagetableYes–TLBmiss,PAinpagetable,butdatanotincacheYes–pagefaultImpossible–TLBtranslationnotpossibleifpageisnotpresentinmemoryImpossible–datanotallowedincacheifpageisnotinmemory处理一次TLB缺失考虑一次TLB缺页在存储器中发生(例如,

设置页表中的有效位)TLB缺失(缺页异常)必须在访存发生的同一时钟周期的末尾被判定,因此下一个时钟周期就开始进行异常处理而不是继续正常的指令执行。下表见图5-27寄存器CP0

寄存器号说明EPC14WheretorestartafterexceptionCause13CauseofexceptionBadVAddr8AddressthatcausedexceptionIndex0LocationinTLBtoberead/writtenRandom1PseudorandomlocationinTLBEntryLo2PhysicalpageaddressandflagsEntryHi10VirtualpageaddressContext4Pagetableaddress&pagenumberTLB缺失处理程序(MIPS)当TLB缺失发生时,MIPS的硬件将被引用的页号保存在一个叫BadVAddr的特殊寄存器中,然后产生异常。这个异常请求操作系统通过软件来处理缺失,控制权被转移到地址80000000hex,TLB缺失处理程序的位置TLBmiss:mfc0$k1,Context #copyaddrofPTEinto$k1lw$k1,0($k1) #putPTEinto$k1mtc0$k1,EntryLo

#putPTEintoEntryLo

tlbwr #putEntryLointoTLB # atRandomeret #returnfromexception指令tlbwr

把控制寄存器EntryLo

中的内容复制到由控制寄存器

Random所选择的TLB表项中。TLB缺失大概需要花费12个时钟周期一些虚拟存储器的设计参数PagedVMTLBsTotalsize16,000to250,000words16to512entriesTotalsize(KB)250,000to1,000,000,0000.25to16Blocksize(B)4000to64,0004to8Hittime0.5to1clockcycleMisspenalty(clocks)10,000,000to100,000,00010to100Missrates0.00001%to0.0001%0.01%to1%两个机器的快表参数IntelNehalemAMDBarcelonaAddresssizes48bits(vir);44bits(phy)48bits(vir);48bits(phy)Pagesize4KB4KBTLBorganizationL1TLBforinstructionsandL1TLBfordatapercore;bothare4-waysetassoc.;LRUL1ITLBhas128entries,L2DTLBhas64entriesL2TLB(unified)is4-waysetassoc.;LRUL2TLBhas512entriesTLBmisseshandledinhardwareL1TLBforinstructionsandL1TLBfordatapercore;botharefullyassoc.;LRUL1ITLBandDTLBeachhave48entriesL2TLBforinstructionsandL2TLBfordatapercore;eachare4-waysetassoc.;roundrobinLRUBothL2TLBshave512entriesTLBmisseshandledinhardware为什么不用虚拟寻址cache?虚拟寻址cache只需要对cache缺失进行地址转换dataCPUTrans-lationCacheMainMemoryVAhitPA

但是使用虚拟地址访问cache,并且两个程序之间共享数据时,可能有别名-两个虚拟地址对应到同一个物理地址,所以在cache中有共享数据的两个备份,在TLB中有两个表项,这将导致一致性问题Mustupdateallcacheentrieswiththesamephysicaladdressorthememorybecomesinconsistent减短地址变换时间可以使cache访问和TLB访问重叠虚拟地址的高位用于访问TLB,低位用于cache的索引TagData=TagData=CacheHitDesiredwordVATagPATagTLBHit2-wayAssociativeCacheIndexPATagBlockoffsetPageoffsetVirtualpage#TheHardware/SoftwareBoundary虚拟地址到物理地址的转换过程中哪些部分是需要硬件支持的呢?TLB快表:用于记录最近用过的地址变换的高速缓存TLBaccesstimeispartofthecachehittimeMayallotanextrastageinthepipelineforTLBaccess(多一级)页表存储,故障检测和更新Pagefaultsresultininterrupts(precise)thatarethenhandledbytheOS缺页导致的中断由操作系统处理Hardwaremustsupport(i.e.,updateappropriately)DirtyandReferencebits(e.g.,~LRU)inthePageTables

硬件要支持页表中的重写位、引用位存储器层次结构的4个问题Q1:一个块可以被放到何处?

(Entryplacement)Q2:如何找到一个块?

(Entryidentification)Q3:当cache缺失时替换哪一块?

(Entryreplacement)Q4:写操作如何处理?

(Writestrategy)Q1&Q2:块可以被放到哪以及如何找到一个块#ofsetsEntriespersetDirectmapped#ofentries1Setassociative(#ofentries)/associativityAssociativity(typically2to16)Fullyassociative1#ofentriesLocationmethod#ofcomparisonsDirectmappedIndex1SetassociativeIndextheset;compareset’stagsDegreeofassociativityFullyassociativeCompareallentries’tagsSeparatelo

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 边坡环境恢复工程方案

- 住宅楼道改造与美化方案

- 水资源综合利用工程实施方案

- 城市绿道建设工程方案

- 绿色物流园区建设方案

- 道路标志标线日常维护方案

- 电动汽车充电桩建设方案

- 工程预算编制与控制方案

- 装修风格定位与选择方案

- 道路施工项目评估方案

- 汽车租赁服务规范与操作手册(标准版)

- 2026年食品安全员培训考试模拟题库及解析答案

- 2025国家国防科技工业局核技术支持中心社会招聘13人模拟试卷附答案

- 2025年大学新能源材料与器件(新能源材料研发)试题及答案

- 深度解析(2026)《HGT 5145-2017甲醇制混合芳烃》

- 道路交通反违章培训课件

- 2025年度麻醉科主任述职报告

- Scratch讲座课件教学课件

- 2025年度安全生产工作述职报告

- 2025年全国硕士研究生考试《管理类联考综合能力》试题及答案

- 护理质量管理质控方案2026

评论

0/150

提交评论