版权说明:本文档由用户提供并上传,收益归属内容提供方,若内容存在侵权,请进行举报或认领

文档简介

1、2022-5-301第5章 CMOS反相器VDDVoutCLVin2022-5-3025.1 引言n反相器是所有数字设计的核心核心。其它复杂电路的电气特性都可以从反相器中得到的结果推断推断出来。(延伸)静态反相器有几个不同的设计指标:成本:用复杂性和面积来表示。完整性和稳定性:用静态(稳态)特性来表示。性能:由动态(瞬态)响应决定。能量效率:由能耗和功耗决定。2022-5-3035.2静态CMOS反相器综述VDDVoutCLVin把MOS晶体管当成简单的开关模型。即晶体管只不过是一个具有无限关断电阻晶体管只不过是一个具有无限关断电阻和有限导通电阻的开关和有限导通电阻的开关。(VGS与VT 的关

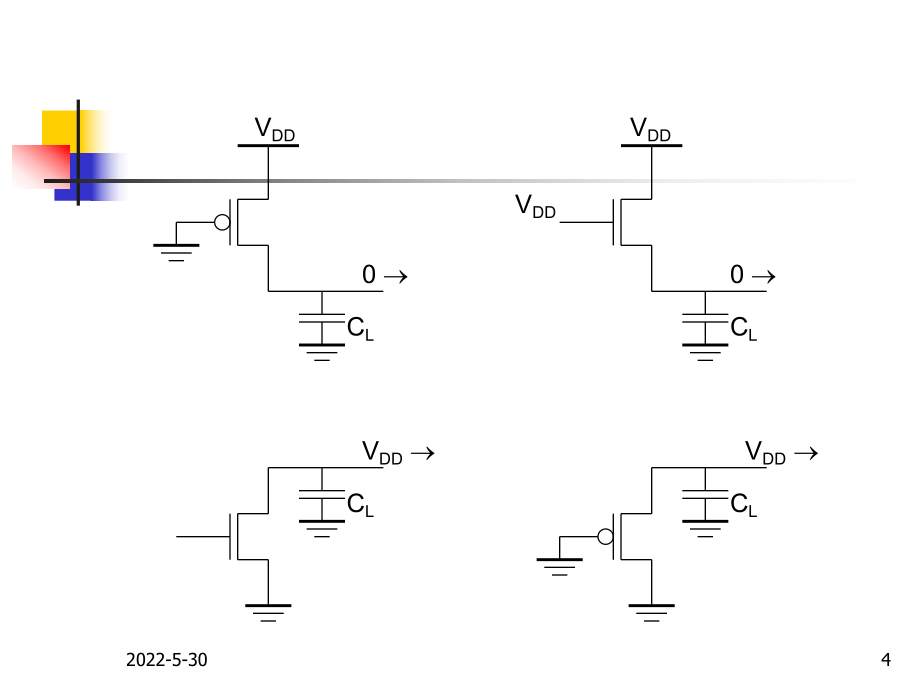

2、系所决定)2022-5-304VDDVDD 0 CLCL0 CLVDDVDDVDD CL2022-5-305静态CMOS的几个重要特性:1、输出高电平和低电平分别为输出高电平和低电平分别为VDD和和GND。即电压摆幅等于电源电压电压摆幅等于电源电压。因此 噪声容限很大。2、逻辑电平与器件的相对尺寸无关无关。所以晶体管可采用最小尺寸(无比逻辑)。3、稳态时在输出和稳态时在输出和VDD或或GND之间总存在一条具有有限电阻的通路之间总存在一条具有有限电阻的通路。因此一个 较好的CMOS反相器具有低输出阻抗,这使它对噪声和干扰不敏感。4、CMOS反相器的输入电阻极高,因为反相器的输入节点只连到晶体管的

3、栅上, 所以稳态输入电流几乎为零。理论上可以驱动无穷多个门。稳态输入电流几乎为零。理论上可以驱动无穷多个门。5、在稳态工作情况下电源线和地线之间没有直接的通路稳态工作情况下电源线和地线之间没有直接的通路。没有电流存在(忽略 漏电流)意味着该门并不消耗任何静态功率。2022-5-306NMOS的I-V特性曲线ID (A)VDS (V)X 10-4VGS = 1.0VVGS = 1.5VVGS = 2.0VVGS = 2.5VLinear dependenceNMOS transistor, 0.25um, Ld = 0.25um, W/L = 1.5, VDD = 2.5V, VT = 0.4V

4、2022-5-307ID (A)VDS (V)X 10-4VGS = -1.0VVGS = -1.5VVGS = -2.0VVGS = -2.5VPMOS transistor, 0.25um, Ld = 0.25um, W/L = 1.5, VDD = 2.5V, VT = -0.4V2022-5-308IDSp = -IDSnVGSn = Vin ; VGSp = Vin - VDDVDSn = Vout ; VDSp = Vout - VDDVoutIDnVGSp = -2.5VGSp = -1Vin = VDD + VGSpIDn = -IDpVin = 1.5Vin = 0Vin =

5、 1.5Vin = 0Vout = VDD + VDSp2022-5-309CMOS 反相器的负载曲线IDn (A)Vout (V)X 10-4Vin = 1.0VVin = 1.5VVin = 2.0VVin = 2.5V0.25um, W/Ln = 1.5, W/Lp = 4.5, VDD = 2.5V, VTn = 0.4V, VTp = -0.4VVin = 0VVin = 0.5VVin = 1.0VVin = 1.5VVin = 0.5VVin = 2.0VVin = 2.5VVin = 2VVin = 1.5VVin = 1VVin = 0.5VVin = 0VPMOSNMOS2

6、022-5-3010 当NMOS和PMOS器件的电流相等时,一个直流(dc)工作点成立。因此dc工作点必须处在两条相应负载线工作点必须处在两条相应负载线的交点上。的交点上。所有的交点(工作点)不是在高输出电平就是在低输出电平上。因此反相器的VTC曲线显示出具有非常窄的过渡区。在过渡区内,两管同时导通且处于饱和状态。2022-5-3011CMOS 反相器 VTCVin (V)Vout (V)2022-5-3012CMOS 反相器 VTCVin (V)Vout (V)NMOS offPMOS resNMOS satPMOS resNMOS satPMOS satNMOS resPMOS satNM

7、OS resPMOS off2022-5-3013n瞬态特性(动态响应):主要由门的输出电容CL决定。它包括NMOS和PMOS晶体管的漏扩散电容、连线 电容 以及扇出门的输入电容。2022-5-3014VDDRnVoutCLVin = V DDVDDRpVoutCLVin = 0l 门的响应时间是由通过电阻Rp和充电电容CL所需要的时间决定的。t=0.69RC因此一个快速门的设计是通过减小输出电容或者减小晶体管的导通电阻实现的。2022-5-30155.3CMOS反相器稳定性的评估静态特性n开关阈值是使得电路门发生翻转时的电压值,即定义为Vin = Vout 的电压点。当VDS = VGS 时

8、PMOS和NMOS管总是饱和的。通过两个晶体管的电流相等便可以求出开关阈值的表达式。5.3.1 开关阈值2022-5-3016VM rVDD/(1 + r) r = kpVDSATp/knVDSATn表明开关阈值取决于比值r,它是PMOS和NMOS管相对驱动强度的比。为了使低电平噪声容限和高电平噪声容限具有相近的值。一般希望VM的值处在电压摆幅的中点附近。为此要求r的值接近于1。为使VM 上移,要求r值较大,即PMOS的尺寸越大。 (W/L)p knVDSATn(VM-VTn-VDSATn/2) (W/L)n kpVDSATp(VDD-VM+VTp+VDSATp/2)=2022-5-3017V

9、T0(V)(V0.5)VDSAT(V)k(A/V2)(V-1)NMOS0.430.40.63115 x 10-60.06PMOS-0.4-0.4-1-30 x 10-6-0.1 (W/L)p (W/L)n =n使用通用0.25umCMOS工艺实现一个CMOS反相器的开关阈值处在电源电压的中点处。并假设电源电压为2.5V。最小尺寸器件的宽长比为1.5。2022-5-3018VT0(V)(V0.5)VDSAT(V)k(A/V2)(V-1)NMOS0.430.40.63115 x 10-60.06PMOS-0.4-0.4-1-30 x 10-6-0.1n使用通用0.25umCMOS工艺实现一个CMO

10、S反相器的开关阈值处在电源电压的中点处。并假设电源电压为2.5V。最小尺寸器件的宽长比为1.5。 (W/L)p 115 x 10-6 0.63 (1.25 0.43 0.63/2) (W/L)n -30 x 10-6 -1.0 (1.25 0.4 1.0/2)=xx= 3.5 (W/L)p = 3.5 x 1.5 = 5.25 如果 VM 为 1.25V时2022-5-3019(W/L)p/(W/L)nVM (V)q VM 对于器件比值的变化相对来说是不敏感的。q当PMOS和NMOS两者的比率为3, 2.5 and 2 产生的开关阈值 VM的值为 1.22V, 1.18V, 和 1.13Vq

11、改变Wp对Wn比值的影响使VTC的过渡区平移。增加PMOS 的宽度使得 VM 移向 VDD,增加NMOS 的宽度使得 VM 移向GND.13.42022-5-3020VinVoutVOH = VDDVM根据定义, VIH 和 VIL 是当 dVout/dVin = -1 (= gain)时的工作点。VOL = GND对VTC进行逐段线性近似简化了VIL和VIH的推导 NMH = VDD - VIH NML = VIL - GND VIH = VM - VM /g VIL = VM + (VDD - VM )/g我们希望在过渡区有较高的增益是我们所希望的。5.3.2噪声容限 VIH VIL=-(

12、VOH-VOL)/g =-VDD/g2022-5-3021增益表达式Vin增益 (1+r)g - (VM-VTn-VDSATn/2)(n - p )ID(VM)是Vin = VM时流过反相器的电流,这一增益几乎完全取决于工艺参数,特别是沟长调制。 Vin(V)pnDSATppDSATnnMDVkVkVIg)(1对Vin = VM 时:2022-5-3022Vin (V)Vout (V)0.25um, (W/L)p/(W/L)n = 3.4(W/L)n = 1.5 (最小尺寸)VDD = 2.5VID(VM)=5910-6AVM 1.25V, g = -27.5VIL = 1.2V, VIH =

13、 1.3VNML = NMH = 1.2(确切的实际 VIL = 1.03V, VIH = 1.45VNML = 1.03V & NMH = 1.05V)CMOS反相器的电压传输特性和噪声容限2022-5-30235.3.3再谈稳定性Vin (V)Vout (V)标准情形好的 PMOS差的 NMOS差的 PMOS好的 NMOS1、器件参数变化2022-5-3024n实际的工作温度会影响到器件的性能变化,偏离典型值。但是,静态CMOS反相器的直流特性对这些变化不敏感。因此该门能在一个很宽范围的工作条件下正确工作。好的器件,好的管子?并且当采用差的管子时,也只是引起开关阈值的平移,并且得到的曲线与

14、典型的曲线相同,该门的工作没有受任何影响。这也是静态CMOS门得以普遍使用的主要原因。2022-5-3025Vin (V)Vout (V)降低VDD改善了增益Vin (V)Vout (V)增益增益=-1对非常低的电源电压传输特性变差2、降低电源电压2022-5-3026当电源电压降低时反相器是否仍能工作?是否对其还有一个可能的限制?n对于固定的晶体管尺寸比r,VM近似的正比于VDD,所以当电源电压降低时反相器在过渡区的增益实际上随电源电压的降低而加大。n特别当电源电压(=0.5V)接近构成它的晶体管的阈值电压时,过渡区的宽度只是电源电压的10%,而电源电压(=2.5V)时,它加大到17%。可见

15、,当电源电压降低时可以改善dc特性,为什么,我们不使所有的数字电路都选择在这样低的电源电压下工作呢?理由有三:2022-5-30271、毫无原则的降低电源电压虽然对减少能耗有正面 影响,但它绝对会使门的延时加大。2、一旦电源电压和阈值电压变的接近时,dc特性对 器件参数的变化就变得越来越敏感。3、降低电源电压意味着减小信号摆幅,并对外部噪 声源更加敏感。2022-5-3028即使电源电压很低时,晶体管仍能导通,仍然具有反相器的特性,因为亚阈值电流足以使该门在低电平和高电平之间切换,并提供足够的增益从而得到可接受的VTC。但使得门的特性变的很差。VOL和VOH不再等于电源的两个电平,并且过渡区的

16、增益接近1。为了能得到足够的增益以用于数字电路,必须使电源为热电势的两倍,否则就只能降低热电势,即降低环境温度,冷却该电路2022-5-3029VDDGNDNMOS (2/.24 = 8/1)PMOS (4/.24 = 16/1)金属金属2金属金属1多晶硅多晶硅输入输入输出输出金属金属1-多晶多晶 接触孔接触孔金属金属2-金属金属1 通孔通孔金属金属1-扩散扩散 接触孔接触孔P扩散区扩散区n扩散区扩散区2022-5-30305.4 CMOS反相器的性能:动态特性t=0.69RCL使得CL 尽可能小是实现高性能CMOS电路的关键。假设所有的电容一起集总成一个单个的电容CL2022-5-3031V

17、outCwVinCDB2CDB1CGD12M2M1M4M3Vout2CG4CG3Vout2VinVoutCLN漏P漏5.4.1计算电容值 包括了影响节点Vout 瞬态响应的所有电容假设输入Vin由一个上升和下降时间均为零的理想电压源所驱动2022-5-3032CL可分解为以下几部分:1、栅漏电容Cgd12=2CGDOW2、扩散电容Cdb1和Cdb23、连线电容CW4、扇出负载门的栅电容Cg3和Cg4假设扇出电容等于负载门M3和M4总的栅电容,因此Cfan-out=Cgate(NMOS)+Cgate(PMOS)=(CGSOn+CGDOn+WnLnCox)+(CGSOp+CGDOp+WpLpCox

18、)线性化2022-5-3033Ceq = Keq Cj0高到低低到高KeqbpKeqswKeqbpKeqswNMOS0.570.610.790.81PMOS0.790.860.590.72022-5-3034一个0.25umCMOS反相器的电容InOutMetal1VDDGND1.2 mm=2 1.125/0.250.375/0.25PMOSNMOSPolysiliconW/LAD (m mm2)PD (m mm)AS (m mm2)PS (m mm)NMOS0.375/0.250.31.8750.31.875PMOS1.125/0.250.72.3750.72.3750.1250.52022

19、-5-3035电容电容表达式表达式值值 (fF) HL值值 (fF) LHCGD12 Con Wn0.230.23CGD22 Cop Wp0.610.61CDB1KeqbpnADnCj + KeqswnPDnCjsw0.660.90CDB2KeqbppADpCj + KeqswpPDpCjsw1.51.15CG3(2 Con)Wn + CoxWnLn0.760.76CG4(2 Cop)Wp + CoxWpLp2.282.28Cw提取参数0.120.12CL6.16.02022-5-30365.4.2 传播延时:一阶分析2022-5-3037n当给一个电压阶跃激励时,一个电路的传播延时正比于由这

20、个电路的下拉电阻和负载电容形成的时间常数。 tpHL = ln(2) Reqn CL = 0.69 Reqn CL tpLH = ln(2) Reqp CL = 0.69 Reqp CL tp = (tpHL + tpLH)/2 = 0.69 CL(Reqn + Reqp)/2n当希望一个门对于上升和下降输入具有相同的传播延时,可通过使NMOS和PMOS晶体管的导通电阻近似相等来实现。VDDRnVout = 0Vin = V DDCLtpHL = f(Rn, CL)2022-5-3038VinVout (V)t (秒) x 10-10 VDD=2.5V0.25mmW/Ln = 1.5W/Lp

21、= 4.5Reqn= 13 k ( 1.5)Reqp= 31 k ( 4.5)模拟得到的图5.15反相器的瞬态响应2022-5-3039VinVout (V)t (sec) x 10-10 VDD=2.5V0.25mmW/Ln = 1.5W/Lp = 4.5Reqn= 13 k ( 1.5)Reqp= 31 k ( 4.5)tpHL = 36 pstpLH = 29 ps因此tp = 32.5 pstftrtpHLtpLH从仿真结果可得: tpHL = 39.9 ps and tpLH = 31.7 psVout2022-5-3040VDD (V) tp(normalized)tpHL = 0

22、.69 Reqn CL = 0.69 (3/4 (CL VDD)/IDSATn ) 0.52 CL / (W/Ln kn VDSATn )可通过展开延时公式中的Req得出决定延时的参数,从而来处理或优化门的延时CMOS反相器传播延时与电源电压的关系2022-5-3041n减小 CLn门本身的内部扩散电容n要求漏扩散区的面积越小越好n互连线电容n扇出电容n增加晶体管的 W/L 比n这是设计者手中最有力和最有效的性能优化工具nW/L增加使得t变小,但也增加了扩散电容,因而增加了CL。n注意自载效应! 当本征电容开始超过由连线和扇出形成的外部负载时,增加门的尺寸对减少延时并没有帮助。只是加大了门的面

23、积。(自载效应)n增加 VDDn一个门的延时可通过改变电源电压来调整。这一灵活性使设计者可以用能量来换取性能。n增加 VDD 超过一定程度后改善就会非常有限,因而应当避免n对可靠性方面的考虑也迫使在深亚微米工艺中对VDD 要规定严格的上限可通过以下方式减小一个门的传播延时:2022-5-30425.4.3从设计角度考虑传播延时n至今我们一直使PMOS较宽,以使它的电阻与下拉的NMOS相匹配,这通常要求两管的宽度比在3-3.5之间。目的:n对称的 VTCn由高至低与由低至高的传播延时相等n如果我们特意的关注速度时,就应该减少PMOS的宽度来加快反相器的速度。 n虽然使PMOS较宽因充电电流的增加

24、而改善了反相器的tpLH ,但它也由于产生较大的寄生电容而使tpHL 变差,当这两个相反的效应存在时,必定存在一个晶体管的宽度比使反相器的传播延时最小。2022-5-3043wgndnLgngpdndpnpwgngpdndpLCCCCCCCCLWLWCCCCCC)(1 (,)/()/()()(2122112211又根据传播延时的表达式可得:)2(69. 02eqneqpLPLHPHLpRRCttt2022-5-3044)1 ()(1(345. 0)(1(269. 02121rRCCCtRRCCCteqnwgndnpeqpeqnwgndnp且 r = Reqp/Reqn代表尺寸完全相同的PMOS

25、和NMOS晶体管的电阻比。令0pt可以求出的最大值,即:2022-5-3045opt = r)1 (21gndnwoptCCCr意味着当导线电容可以忽略时:如果导线电容占主导地位时,那么应当采用较大的值2022-5-3046 = (W/Lp)/(W/Ln) tp(sec)x 10-11 为 2.4 (= 31 k/13 k)时将得到对称的瞬态响应 在1.6 到 1.9 时可以得到最优的性能tpLHtptpHL确定以相同门为负载的CMOS反相器的尺寸2022-5-3047n把反相器的负载电容分为本征和外部电容两个部分:nCint : 代表反相器的本征输出电容,与N和P的扩散以及栅漏电容有关nCe

26、xt : 外部负载电容,来自扇出和导线电容tp = 0.69 Req Cint (1 + Cext/Cint) = tp0 (1 + Cext/Cint)n这里 tp0 = 0.69 Req Cint代表反相器的负载只是本征电容时的延时(本征延时)2022-5-3048n门的电阻与参考门的关系为Req = Rref/S, 本征电容正比于晶体管的宽度 Cint = SCiref tp = 0.69 Rref Ciref (1 + Cext/(SCiref) = tp0(1 + Cext/(SCiref)得出两个结论: ntp0 与门的尺寸无关;只取决于工艺及反相器的版图。当不存在任何的外部负载时

27、,门的驱动强度的提高完全为随之而增加的电容所抵消n使S无穷大将达到最大可能的性能改善,因为这消除了任何外部负载的影响,使延时减小到只有本征延时值。然而任何比(Cext/Cint)足够大的尺寸系数S都会显著增加硅面积而得到类似的结果。晶体管的尺寸是如何影响门的性能:晶体管的尺寸是如何影响门的性能:尺寸系数S表示的是把反相器的晶体管尺寸与一个参考门(通常是一个最小尺寸的反相器)的晶体管尺寸联系起来2022-5-3049S tp(sec)x 10-11 当S = 5时已得到了大部分的改善. 而尺寸系数大于10几乎得不到任 何额外的收益.对固定的扇出,以相同的系数S放大N和P管的尺寸来提高反相器的性能

28、有很显著的自载效应由表5.2得到Cint/Cext=1.05。Cint=3.0fF,Cext=3.15fF。可以预见最大的性能改善为2.05。当尺寸系数为10时得到的性能改善与最佳的差距只为10%之内,再加大就效果不大了。2022-5-3050nCint = Cg,这就是反相器的输入栅电容Cg与本征输出电容之间的关系,这两个电容均正比于门的尺寸。n是比例系数,只与工艺有关,并且对于大多数的亚微米工艺接近于1。确定反相器链的尺寸:当一个门处在实际环境中时如何确定它的最优尺寸。2022-5-3051ntp = tp0 (1 + Cext/ Cint) =tp0 (1 + Cext/ Cg) = t

29、p0 (1 + f/)n由上式可知,反相器的延时只取决于它的外部负载电容与输入栅电容间的比值,这一比值称为等效扇出f。nf = Cext/Cg2022-5-3052InOutCLn我们的目标是使通过反相器链的延时最小。其中第一个反相器的输入电容为Cg1,而反相器链末端为一个固定的负载电容CLn 第j级反相器的延时表达式为:tp,j = tp0 (1 + Cg,j+1/(Cg,j) = tp0(1 + fj/ ) 又因为 tp = tp1 + tp2 + . . . + tpN 因此 tp = tp,j = tp0 (1 + Cg,j+1/(Cg,j) Cg,112N这个方程含有N-1个未知数,

30、即Cg2,Cg3,.CgN。通过求N-1次偏微分并令他们都等于0,即:0,jgptt可求得最小延时,并得到下列的一组约束条件2022-5-3053nCg,j+1/Cg,j=Cg,j/Cg,j-1 其中j=2Nn换而言之,每一个反相器的最优尺寸是与它相邻的前后两个反相器尺寸的几何平均数:nCg,j= Cg,j-1 Cg,j+1n这意味着每个反相器的尺寸都相对于它前面反相器的尺寸放大相同倍数f,即每个反相器都具有相同的等效扇出,因而也具有相同的延时2022-5-3054n当Cg,1和CL给定时,可推导出尺寸系数为:nf = CL/Cg,1 = Fn通过该反相器链的最延时为:ntp = N tp0

31、(1 + ( F ) / )nF代表该电路的总等效扇出,为CL/Cg,1。n当只存在一级时,这是一个线性关系,加入第二级将使它变为平方根关系。依次类推。n现在明显的问题是对于给定的F值如何选定级数使延时最短。NN2022-5-3055选择一个反相器链的正确级数n对于给定的 F (=fN)在选择级数时需要综合考虑。n当级数太大时,公式的第一部分(它代表了反相器级的本征延时)将占主导地位。n如果级数太小,则每一级的等效扇出变大,使公式的第二部分占主导地位。NNn通过求最小延时表达式对级数的导数并令它为0,可以求得最优值。我们得到: + F - ( F lnF)/N = 0n当 = 0 (忽略自载,

32、因此负载电容只由扇出构成) ,得到最优的级数为N = ln (F) ,且每一级的等效扇出为 f = e = 2.71828,这一优化的缓冲器设计以一种指数形式逐级放大各级尺寸。n当 = 1 (典型情况下) 最优的效率扇出系数接近于3.6,一个通常的做法是选择最优的扇出为4。NN2022-5-3056最优扇出n选择扇出值大于最优值并不会过多的影响延时,但能减少所要求的缓冲器级数和实现面积n一个通常的做法是选择最优的扇出为f = 4 (对 = 1)n但是采用过多的级数对延时会有明显的负面影响,因而应当避免。foptf最小尺寸下的延时2022-5-3057CL = 64 Cg,1Cg,1 = 11C

33、L = 64 Cg,1Cg,1 = 118CL = 64 Cg,1Cg,1 = 11416CL = 64 Cg,1Cg,1 = 112.8822.6N f tp1 64 652 8 1834 154 2.8 15.32022-5-3058n在驱动非常大的电容负载时,采用串联的反相器可以达到非常明显的加速。F ( = 1)无缓冲器无缓冲器两级反相器两级反相器反相器链反相器链10118.38.31001012216.51,00010016524.810,00010,00120233.1引入缓冲器级的影响引入缓冲器级的影响不同驱动器结构的topt/tp0与F的关系2022-5-3059nCL/Cg,

34、1 若被分成3级,即 N = 3 反相器的 CL/Cg,1 = 8/1 f = InOutCL = 8 Cg,1Cg,112022-5-3060InOutCL = 8 Cg,1Cg,11f = 2f2 = 4nCL/Cg,1 若被分成3级,即 N = 3 反相器的 CL/Cg,1 = 8/1 f = 38 = 22022-5-3061n实际上,输入信号是逐渐变化的,而且N和P管会暂时同时导通一段时间,这会影响所得到的充(放)电总电流,从而影响传播延时。ts(秒)tp(秒)x 10-11 x 10-11 对于扇出为单个门的最小尺寸反相器,tp与输入信号斜率的关系n一旦ts tp, tp随输入斜率

35、的增加而(近似的)线性增加。nts 是输入的上升/下降时间。输入信号的上升输入信号的上升-下降时间下降时间2022-5-3062n一个门的设计永远不会是孤立的,它的性能要受扇出以及驱动其输入端的门的驱动强度的影响,这样就得到了一个在反相器链中反相器i传播延时的修正表达式:tip = tistep + ti-1step ( 0.25)反相器i的传播延时等于同样的门在阶跃输入时(即输入斜率为无穷大)的延时加上它前面一级门的阶跃输入延时的一部分。n保持门的输入信号的上升时间小于或等于门的传播延时是很有利的.n提高性能n降低功耗n使信号的上升和下降时间较小并且具有接近相等的值是高性能设计面临的主要挑战

36、之一。这称为斜率工程设计( slope engineering)设计挑战设计挑战2022-5-30635.5 功耗、能量和能量延时n具有理想VTC的静态CMOS反相器表现出极佳的稳定性,从而打开了自动化设计的大门。n静态CMOS在稳态工作时几乎没有完全功耗。n正是由于上面两点使得静态CMOS技术成为大多数现代数字设计的选择。对称形状全逻辑摆幅高噪声容限2022-5-30645.5.1动态功耗1、由充放电电容引起的动态功耗2、由直接通路电流引起的功耗VDDRnVoutCLVin = V DDVDDRpVoutCLVin = 02022-5-3065输出电压从0翻转到VDD时从电源中取得的能量值E

37、VDD以及在翻转结束时在电容上存储的能量Ec通过在相应周期上对瞬时功耗积分可得:2000200021)()(DDLVoutoutLoutoutLoutVDDDDLoutDDLoutLDDDDVDDVDDVCdvvCdtvdtdvCdtVtiEcVCdvVCdtdtdvCVdtVtiEDD1、由充放电电容引起的动态功耗、由充放电电容引起的动态功耗2022-5-3066n每当电容CL通过P管充电时,它的电压从0上升至VDD,此时从电源吸取了一定数量的能量,该能量的一部分消耗在P管中,而其余则存放在负载电容上。n在由高至低的翻转期间,这一电容被放电,于是存放的能量被消耗在N管中。消耗在P管和消耗在N

38、管上的能耗都与管子的尺寸没有关系。2022-5-3067n每一个开关周期(由L H和H L翻转组成)都需要一个固定数量的能量,即CLVDD2。为了计算功耗,我们必须考虑器件的开关频率。如果这个门每秒通断f0 1次,则功耗等于:Pdyn = CL VDD2 f01 式中, f 01代表消耗能量的翻转的频率,对于静态CMOS为0 1翻转 2022-5-3068nf 01 也称为开关活动性,对于复杂的门与输入信号的本质及统计特性、整个电路的拓扑结构以及要实现的功能有关。因此它是一个非常复杂的变量。Pdyn = CL VDD2 f01 =CL VDD2 P 01 f= CEFF VDD2 f F代表输

39、入发生变化事件的最大可能的速率(通常是时钟速率),而P 01是时钟变化事件在该门的输出端引起01(消耗功率)变化事件的概率。 CEFF= P 01 CL称为等效电容,它表示每时钟周期发生开关的平均电容。 2022-5-3069n假设维持相同的时钟速率,降低电源电压可使得功耗成平方关系减小,但一旦VDD接近2VT时就会严重降低性能。(优先采用)n当因外部限制使得VDD达到它的下限时,减少功耗的方法就是减少等效电容。可通过它的两方面来实现:实际电容及翻转活动性。n减少翻转活动性只能在逻辑和结构的抽象层次上实现。低能量低能量-功耗设计技术功耗设计技术2022-5-3070n减少实际电容从总体上来说比

40、较值得,由于在一个组合逻辑电路中大部分的电容是晶体管电容(栅电容和扩散电容),所以应保证晶体管尽可能的达到合理的最小尺寸,同时可通过逻辑或结构上的加速技术来弥补对性能的影响。n晶体管尺寸放大的唯一情形是当负载电容由外部电容(如扇出或导线电容)占主导地位的时候。n在标准单元库中一般也使得晶体管较大以便满足一定范围的负载和性能要求。2022-5-3071用图解法来确定晶体管尺寸使能耗最小F为总等效扇出,f为尺寸系数。123456700.511.5f归一化的能量F=1F=2F=5F=10F=201234567012.54fVDD(V)F=1F=2F=5F=10F=202022-5-3072n改变器件

41、尺寸并降低电源电压是减小逻辑电路能耗的非常有效的方法。对于具有较大等效扇出的电路犹为如此。n在最优值之外过多的加大晶体管的尺寸会付出较大的能量代价。n在F值较大时,在达到最小能量时的最优尺寸系数一般比考虑最优性能时的最优尺寸系数要小。当 F=20, fopt(能量) = 3.53,而fopt(性能) = 4.472022-5-30732、直接通路电流引起的功耗、直接通路电流引起的功耗n当输入信号不为无穷大的斜率造成了开关过程中VDD和GND之间在短期内出现一条直流通路。此时两管都导通。VinVoutCLIsc2022-5-3074vinishortIpeakttVTVDD-VT过渡期间的短路电

42、流在(合理)(合理)假设所形成的电流脉冲可近似成三角形及反相器的上升和下降响应是对称的条件下,可计算出每个开关周期消耗的能量如下:2022-5-3075Edp=VDDIpeaktsc/2+VDDIpeaktsc/2=tscVDDIpeakPdp=tscVDDIpeakf=CscVDD2f平均功耗为:8 . 022)( frDDTDDsDDTDDsctVVVtVVVt直接通路引起的功耗与开关活动性成正比,有点类似电容功耗。Tsc代表两个器件同时导通的时间。直线输入斜率代表0-100%的翻转时间2022-5-3076VinVoutCLIsc 0VinVoutCLIsc Imax大电容负载小电容负载2022-5-3077n考虑一个静态CMOS反相器在输入端发生由0到1的翻转。n首先假设负载电容很大,所以输出的下降时间明显大于输入的上升时间。在这种情况下输入在输出开始改变之前就已经通过了过渡区。n由于这一时期P管的源漏电压近似为0,因此该器件甚至还没有传导任何电流就断开了。n在这种情况下短路电流接近于零。2022-5-3078Ipeak (A)时间 (秒)x 10-4CL = 20 fFCL = 100 fFCL = 500 fFCMOS反相器通过N

温馨提示

- 1. 本站所有资源如无特殊说明,都需要本地电脑安装OFFICE2007和PDF阅读器。图纸软件为CAD,CAXA,PROE,UG,SolidWorks等.压缩文件请下载最新的WinRAR软件解压。

- 2. 本站的文档不包含任何第三方提供的附件图纸等,如果需要附件,请联系上传者。文件的所有权益归上传用户所有。

- 3. 本站RAR压缩包中若带图纸,网页内容里面会有图纸预览,若没有图纸预览就没有图纸。

- 4. 未经权益所有人同意不得将文件中的内容挪作商业或盈利用途。

- 5. 人人文库网仅提供信息存储空间,仅对用户上传内容的表现方式做保护处理,对用户上传分享的文档内容本身不做任何修改或编辑,并不能对任何下载内容负责。

- 6. 下载文件中如有侵权或不适当内容,请与我们联系,我们立即纠正。

- 7. 本站不保证下载资源的准确性、安全性和完整性, 同时也不承担用户因使用这些下载资源对自己和他人造成任何形式的伤害或损失。

最新文档

- 安全培训考核奖罚制度

- 麻醉科新人培训制度

- 保安负责制度规范

- 大厅窗口培训制度

- 公司讲师培训奖励制度

- 安全技术培训交底制度

- 护士规培化培训相关制度

- 物流企业内部培训制度

- 相关方来访人员培训制度

- 艺术培训学校休假制度

- 水库安全运行管理培训课件

- 2026年中国热带农业科学院橡胶研究所高层次人才引进备考题库有答案详解

- 高考英语读后续写技巧总结

- 2026年保安员资格证理论知识考试题库

- 2026年孝昌县供水有限公司公开招聘正式员工备考题库及一套完整答案详解

- 2025年下半年河南郑州市住房保障和房地产管理局招聘22名派遣制工作人员重点基础提升(共500题)附带答案详解

- 收费室课件教学课件

- 维修事故协议书

- 2025ESC+EAS血脂管理指南要点解读课件

- 2025至2030外周静脉血栓切除装置行业调研及市场前景预测评估报告

- DB34∕T 5176-2025 城市轨道交通智能运维系统建设指南

评论

0/150

提交评论